208点击型号即可查看芯片规格书

1149点击型号即可查看芯片规格书

特征

为高性能3.3V系统优化

- 5 ns端到端逻辑延迟,内部系统频率高达208 MHz

- 小型封装,包括vqfps、tqfps和csp(芯片级封装)

- 所有套餐均提供免费PB

- 低功率运行

- 5V容限I/O引脚接受5V、3.3V和2.5V信号

- 3.3V或2.5V输出能力

- 先进的0.35微米功能尺寸CMOS快速闪存技术

先进的系统功能

- 系统内可编程

- 卓越的销锁定和可布线性

FastConnect II开关矩阵

- 超宽54输入功能块

- 每个宏单元最多90个产品术语,并有单独的产品术语分配

:XC9500XL设备系列

- 具有三个全局和一个积项时钟的本地时钟反转

- 每个输出管脚的单独输出启用(带本地反转)

- 所有用户和边界扫描管脚输入上的输入滞后

- 所有用户引脚输入上的总线保持电路

- 支持热插拔功能

- 在所有设备上完全支持ieee标准1149.1边界扫描(jtag)

四针兼容设备密度

- 36至288个宏单元,800至6400个可用门

快速并发编程

单个输出的回转率控制

增强的数据安全功能

卓越的质量和可靠性

- 10000个程序/擦除周期耐久等级

- 20年数据保留

引脚与5V芯XC9500系列兼容,采用通用封装封装封装

家庭概况

FastFlash XC9500XL系列是一个3.3V CPLD系列,主要用于高端通信和计算系统中的高性能、低电压应用,在这些系统中,高设备可靠性和低功耗非常重要。每个xc9500xl设备都支持系统内编程(isp)和完整的ieee std 1149.1(jtag)边界扫描,从而为小尺寸封装提供优越的调试和设计迭代能力。XC9500XL系列设计用于与XilinxVirtex系列、Spartan系列和XC4000XL系列的现场可编程门阵列密切合作,使系统设计师能够在快速接口电路和高密度通用逻辑之间以最佳方式划分逻辑。如表1所示,XC9500XL设备的逻辑密度范围分别为800至6400个可用门和36至288个寄存器。多个包选项和相关的I/O容量如表2所示。XC9500XL系列成员完全兼容管脚,允许在给定的封装外形中跨多个密度选项进行轻松的设计迁移。

XC9500XL体系结构特性满足了系统内可编程性的要求。增强的插针锁定功能避免了昂贵的板返工。在整个商业运行范围内的系统编程和高编程耐久性评级提供无忧的系统现场升级重新配置。扩展的数据保留支持更长、更可靠的系统操作寿命。

先进的系统功能包括输出转换率控制和用户可编程的接地引脚,以帮助减少系统噪音。每个用户引脚与5V、3.3V和2.5V输入兼容,输出可配置为3.3V或2.5V操作。XC9500XL设备显示对称的3.3V全输出电压摆动,以允许平衡上升和下降时间。

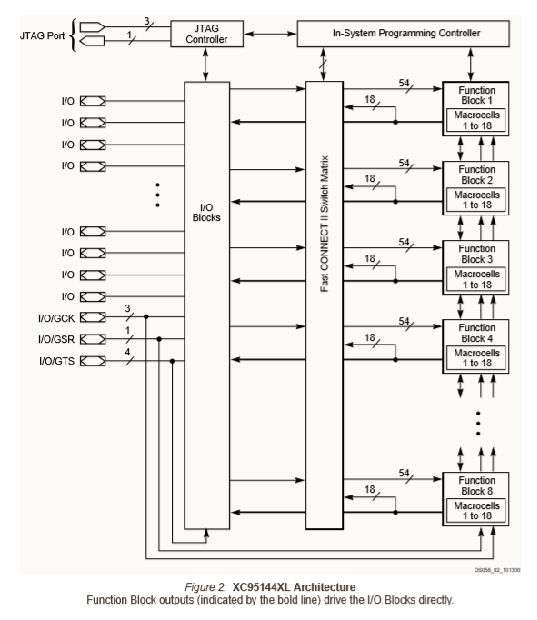

每个XC9500XL设备是一个子系统,由多个功能块(FBS)和I/O块(IOB)组成,通过FastConnect II开关矩阵完全互连。iob为设备输入和输出提供缓冲。每个FB提供可编程逻辑能力,具有额外的54个输入和18个输出。FastConnect II开关矩阵将所有FB输出和输入信号连接到FB输入。对于每个FB,多达18个输出(取决于封装管脚计数)和相关的输出使能信号直接驱动到IOB

功能块

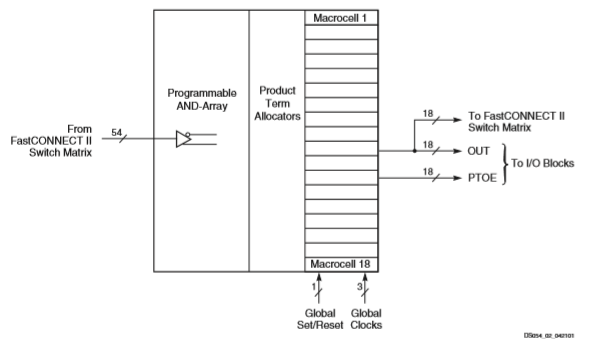

每个功能块由18个独立的宏单元组成,每个宏单元能够实现组合或注册的功能。FB还接收全局时钟、输出启用和设置/重置信号。FB产生18个驱动FastConnect开关矩阵的输出。这18个输出及其相应的输出使能信号也驱动iob。

fb中的逻辑是使用产品表示的总和来实现的。54个输入向可编程和阵列提供108个真实和补充信号,形成90个产品术语。这些产品术语中的任意数量(最多90个可用术语)都可以由产品术语分配器分配给每个宏单元。

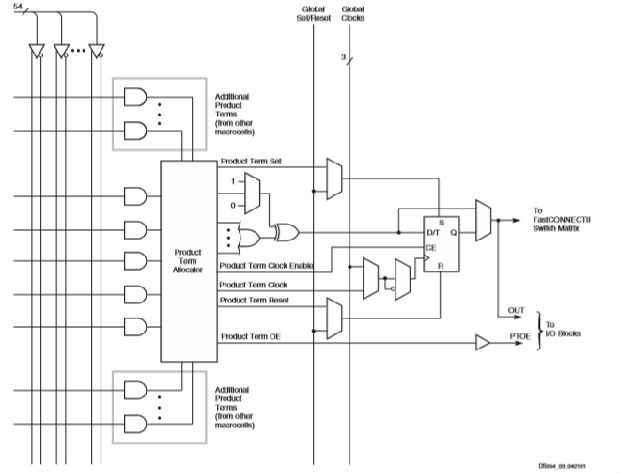

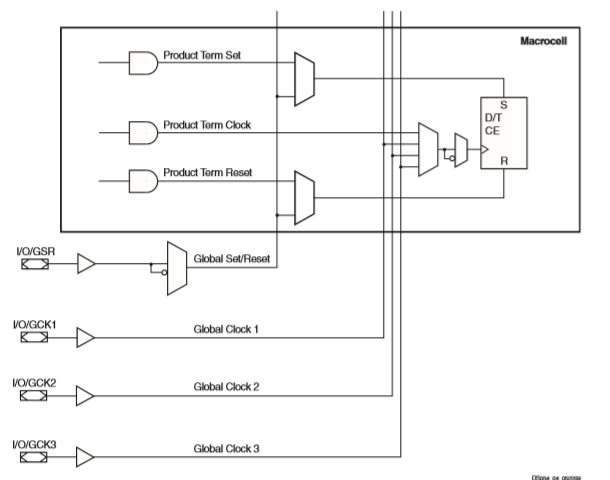

每个xc9500xl宏单元可以单独配置操作。每个寄存器都支持两个异步集

用于组合函数或注册函数。宏单元和重置操作。通电时,所有用户注册

相关的FB逻辑如图3所示。初始化为用户定义的预加载状态(如果未指定,则默认为0 5个来自和数组的直接产品术语可用)。

用作主要数据输入(到或和异或门)以实现组合功能,或用作控制输入,包括时钟、时钟启用、设置/重置和输出启用。与每个宏单元关联的产品术语分配器选择如何使用这五个直接术语。

功能块内的XC9500XL宏单元

所有全局控制信号可用于每个宏单元,包括时钟、设置/重置和输出启用信号。宏单元寄存器时钟源于三个全局时钟或一个乘积项时钟。所选时钟源的真极性和补极性都可以在每个宏单元中使用。还提供gsr输入以允许将用户寄存器设置为用户定义的状态。

产品术语分配器

产品术语分配器控制如何将五个直接产品术语分配给每个宏单元。例如,所有五个直接项都可以驱动或函数

直接积项宏单元逻辑

产品术语分配器可以在fb中重新分配其他产品术语,以增加宏单元超过五个直接术语的逻辑容量。任何需要附加产品条款的宏单元都可以访问FB内其他宏单元中的未提交产品条款。一个宏单元最多可以使用15个产品项,而TPTA的增量延迟很小注意,增量延迟只影响其他宏单元中的乘积项。直接产品条款的时间没有改变。

输入缓冲器与5V CMOS、5V TTL、3.3V CMOS和2.5V CMOS信号兼容。输入缓冲器使用内部3.3V电压源(V)来确保输入阈值是恒定的,并且不随V电压变化。每个输入缓冲器提供输入滞后(典型为50 mV),以帮助降低具有缓慢上升或下降边缘的输入信号的系统噪声。CCNTCIO

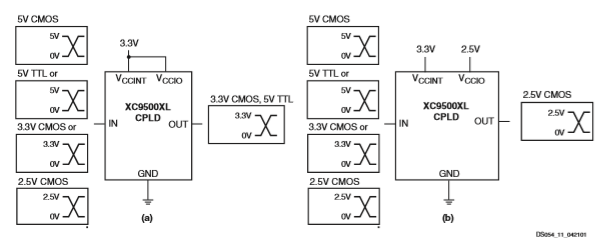

每一个输出驱动器的设计,以提供快速切换和最小的功率噪声。设备中的所有输出驱动器可以配置为通过将设备输出电压电源(v)连接到3.3v或2.5v电压电源来驱动3.3v cmos电平(也与5v ttl电平兼容)或2.5v cmos电平。图11显示了XC9500XL设备如何在只有3.3V的系统和混合电压系统中使用,以及5V、3.3V和2.5V电源的任何组合。CIO

每个输出驱动器也可以配置为回转率限制操作。在用户控制下,可以降低输出边缘速率以降低系统噪声(附加时间延迟t)。

输出使能可以从四个选项之一生成:来自宏单元的产品术语信号、任何全局输出使能信号(gts),始终为“1”或始终为“0”。对于具有72个或更少宏单元的设备,有两个全局输出使能,对于具有144个或更多宏单元的设备,有四个全局输出使能。任何选定的输出使能信号可在每个管脚输出处进行局部反转,以提供最大的设计灵活性。

每个IOB提供用户可编程的接地引脚能力。这允许将设备I/O管脚配置为附加接地管脚,以强制其他未使用的管脚进入低压状态,并提供附加设备接地能力。引脚的接地是通过内部逻辑实现的,该逻辑强制逻辑低输出,而不考虑内部宏单元信号,因此内部宏单元逻辑不受可编程接地引脚能力的影响。

每个iob还提供在有效用户操作期间处于活动状态的总线保持电路(也称为“保持器”)。总线保持特性通过保持输入的最后一个已知状态直到下一个输入信号出现,消除了连接未使用引脚的需要,无论是高还是低。总线保持电路通过50 kΩ的标称电阻(R)驱动相同的状态。注:总线保持输出将驱动不高于V,以防止与2.5V组件接口时信号过驱动。BHCIO

XC9500XL设备,仅适用于(A)3.3V和(B)混合5V/3.3V/2.5V系统

当设备不在有效的用户操作中时,总线保持电路默认为等效的50 kΩ上拉电阻器,以提供已知的可重复设备状态。当设备处于擦除状态、编程模式、JTAG INTEST模式或初始通电时,会发生这种情况。下拉电阻器(1kΩ)可以外部添加到任何引脚,以覆盖默认的R电阻,从而在通电或任何其他模式期间强制处于低状态。BH

5V容错I/O

即使核心电源为3.3伏,每个XC9500XL设备上的I/O都具有完全5伏的耐受能力。这允许5V CMOS信号直接连接到XC9500XL输入,而不会损坏。在将5V信号应用于I/O之前,3.3V电源必须至少为1.5V。在3.3v/2.5v混合系统中,用户管脚、核心电源(v)和输出电源(v)可以按任意顺序供电。CCNTCCNTCIO

Xilinx专有ESD电路和高阻抗初始状态允许使用这些设备的热插拔卡。

销钉锁定能力

在设计迭代期间锁定用户定义的管脚分配的能力取决于体系结构适应意外更改的能力。xc9500xl设备包含了一些架构特性,这些特性增强了接受设计更改的能力,同时保持了相同的引脚。

xc9500xl架构结合了fastconnect ii交换机矩阵中的大量路由交换机、54宽的输入功能块以及每个宏单元内灵活的双向产品术语分配,提供了优越的pin锁定特性。这些特性解决了需要添加或更改内部路由的设计更改,包括将附加信号添加到现有方程中,或分别增加方程复杂性。

系统内编程

一个或多个XC9500XL设备可以菊花链连接在一起,并通过标准4针JTAG协议在系统中编程,如图14所示。系统内编程提供快速有效的设计迭代,并消除包处理。xilinx开发系统使用xilinx下载电缆、第三方jtag开发系统、jtag兼容板测试仪或模拟jtag指令序列的简单微处理器接口提供编程数据序列。

在系统编程过程中,所有的I/O都是3态的,并由总线保持电路拉高。如果在此期间某个特定信号必须保持低电平,则可以在引脚上添加下拉电阻器。

外部编程

XC9500XL设备也可以由Xilinx HW-130设备程序员和第三方程序员进行编程。这提供了在制造过程中使用预编程设备的额外灵活性,并为将来的增强和设计更改提供了系统内可编程选项。

可靠性和耐久性

所有xc9500xl cpld在系统程序/擦除周期中提供至少10000的持久性级别和至少20年的数据保持期。每个设备都符合此持续时间限制内的所有功能、性能和数据保留规范。

ieee标准1149.1边界扫描(jtag)

xc9500xl设备完全支持ieee标准1149.1边界扫描(jtag)。每个设备都支持extest、sample/preload、bypass、usercode、intest、idcode、highz和clamp指令。系统编程操作中包含附加说明。

设计安全性

XC9500XL设备包含高级数据安全功能,可完全保护编程数据免受未经授权的读取或意外的设备擦除/重新编程。表3显示了四种不同的可用安全设置。

用户可以设置读取安全位,以防止读取或复制内部编程模式。设置后,它们还禁止进一步的程序操作,但允许设备擦除。擦除整个设备是重置读取安全位的唯一方法。

当jtag管脚受到噪声(例如系统通电期间)影响时,写安全位提供额外的保护,防止意外的设备擦除或重新编程。一旦设置,当设备需要用有效模式和特定的jtag指令序列重新编程时,可以停用写保护。

低功率模式

所有XC9500XL设备都为单个宏单元或跨所有宏单元提供低功耗模式。此功能可显著降低设备功率。

每个宏单元可以由用户在低功耗模式下编程。应用程序的性能关键部分可以保持在标准电源模式,而应用程序的其他部分可以编程为低功耗操作,以减少总体功耗。为低功耗模式编程的宏单元在管脚到管脚的组合延迟和寄存器设置时间中产生附加延迟(tlp)。产品项时钟输出和产品项输出启用延迟不受宏单元功率设置的影响。以小于50ns上升/下降时间的速率切换的信号应分配给在低功率模式下配置的宏单元。

时序模型

XC9500XL架构的一致性允许整个设备的简化计时模型。基本计时模型仅适用于使用直接乘积项的宏单元函数,具有标准功率设置和标准转换率设置。表4显示了产品术语分配器(如果需要)、低功耗设置和回转限制设置对每个关键定时参数的影响。

乘积项分配时间取决于宏单元函数的逻辑跨度,宏单元函数的逻辑跨度定义为小于乘积项路径中的最大分配器数。如果只使用直接乘积项,则逻辑跨度为0。

通电特性

通电期间,XC9500XL设备I/O可能未定义,直到V上升到1伏以上。这个时间段被称为亚阈值区,因为晶体管还没有完全打开。如果v在v之前或与v同时通电,则i/o可以在此电压转换范围内驱动。如果在V通过亚阈值区域后V通电,I/O将处于3状态,并有微弱的上拉,直到V达到用户操作状态的阈值(约2.5V)。当V达到这一点时,初始化用户寄存器(通常在200μs内),然后I/O将采用由用户模式确定的行为,如图17所示。小精灵小精灵小精灵小精灵小精灵小精灵小精灵

如果设备处于擦除状态(在对任何用户模式进行编程之前),则设备输出将在弱上拉时保持禁用状态。JTAG引脚允许设备在任何时候进行编程。所有设备出厂时都处于擦除状态。

如果对设备进行了编程,则设备输入和输出将呈现其正常运行的配置状态。jtag管脚允许在任何时候进行设备擦除或边界扫描测试。

开发系统支持

XC9500XL系列和相关的系统内编程功能在Xilinx提供的任何一个软件解决方案中都完全受支持。

基金会系列是一个包含示意性条目、HDL(VHDL、Verilog)的集成开发系统。

时序模型参数

以及模拟能力。它支持xc9500xl系列以及其他cpld和fpga系列。

联盟系列包括cpld和fpga实现技术,以及联盟伙伴eda解决方案所需的所有库和接口。

FastFlash技术

采用先进的0.35微米特征尺寸CMOS闪存工艺制造所有XC9500XL器件。fastflash过程提供高性能逻辑能力、快速编程时间、卓越的可靠性和持久性评级。