FIN24C点击型号即可查看芯片规格书

特征

低功耗,对电池寿命的影响最小多种断电模式带直流平衡的交流耦合待机模式下为100NA,典型运行5mA条件电缆缩减率:25:4或更大双向操作50:7或以上任意方向最多24位高达20MHz并行接口操作电压从1.65V转换为3.6V超小型和经济高效的包装高ESD保护:>7.5kV HBM并行I/O电源(VDDP)范围介于1.65伏至3.6伏

应用

微型控制器或像素接口图像传感器小型显示器液晶显示器、手机、数码相机、便携式游戏机,打印机、PDA、摄像机、汽车 一般说明:FIN24Cμserdes是一种低功耗串行器/可以帮助最小化成本的反序列化程序(serdes)以及传输宽信号路径的能力。通过使用串行化传输的信号数从一个点到另一个点可以显著减少。单向路径的典型缩减率为4:1到6:1。对于双向操作,使用半双工信号源,可以将信号降低增加到接近10:1。通过使用差分信号,屏蔽和emi滤波器也可以最小化,进一步降低序列化的成本。差分信号对于提供能够承受无线电和电噪声源的噪声不敏感信号也很重要。功耗的大幅度降低使得在超便携应用中对电池寿命的影响。一独特的词边界技术确保反序列化数据时标识字边界。这保证了每个单词都正确对齐在反序列化程序中逐字逐句地通过不重复的时钟和数据的唯一序列除了单词边界。一个pll就足够了适用于大多数应用,包括双向操作。

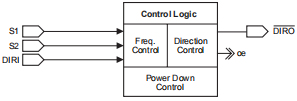

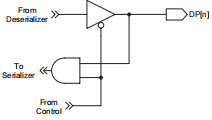

嵌入式字钟操作FIN24C与位时钟同步发送和接收串行数据源。位时钟被修改为在每个数据的末尾创建一个字边界单词。单词边界由跳过低时钟脉冲。这个出现在序列中作为连续三位时间的时钟流,其中信号CKSO仍然很高。为了实现这种方案,两个额外的数据位是必修的。在字边界阶段,根据实际数据字的最后一位,数据切换为先高后低或先低后高。提供了一些实际数据字和添加了字边界位的数据字。注意在串行传输期间,24位字扩展到26位。位25和位26是相对于位定义的24。位25总是位24的倒数,位26是始终与第24位相同。这样可以确保“0”—“1”“1”—“0”转换总是在CKSO高的嵌入字阶段。序列化程序生成字边界数据位以及边界时钟条件并将其嵌入串行数据流。反序列化程序寻找结尾要捕获和传输的字边界条件数据到并行端口。反序列化程序只使用要查找和捕获数据。这些边界位在发送到并行端口的单词。lvcmos数据i/olvcmos输入缓冲器具有标称阈值值等于一半VDDP。只有当设备作为序列化程序运行时,输入缓冲区才可操作。当设备作为反序列化程序运行时,输入被关闭以节省电源。LVCMOS三态输出缓冲器的额定值为在1.8V下,源/汇电流为2mas。输出为当DIRI信号被断言为低时激活。当diri信号被断言为高,双向lvcmosI/O处于高Z状态。纯电容负载下条件下,输出在GND和VDDP之间摆动。未使用的LVCMOS输入缓冲区必须绑定到有效逻辑低电平或有效逻辑高电平以防止由浮动输入引起的静态电流消耗。未使用的LVCMOS输出应保持浮动。未使用的双向引脚应通过高值电阻器。如果FIN24C设备配置为单向序列化程序,未使用的数据I/O可以是作为未使用的输入。如果FIN24C是作为反序列化程序,未使用的日期I/O可以被视为未使用输出。

差分I/O电路FIN24C采用了FSC专有的CTL I/O技术。CTL是一种低功耗、低EMI差分摆动I/O技术。ctl输出驱动程序生成一个常量输出源和汇电流。CTL输入接收器从其连接的输出缓冲区感测电流差和方向。这与LVDS,它使用恒定电流源输出,但是电压感应接收器。像lvds一样,输入源端接电阻器用于正确端接传输线。FIN24C设备包含CKSI接收器上的内部终端电阻器和DS输入端的门控内部终端电阻器接收器。门控终端电阻确保不管数据流的方向如何终止。电流传感器的灵敏度相对较高CTL允许它在更低的电流驱动和更低的电压。在断电模式下,差分输入被禁用并断电,差分输出为处于高z状态。CTL输入具有固有的支持浮动输入的故障安全功能。什么时候?序列化器的cksi输入对未使用,它可以可靠地保持浮动。或者两个输入都可以是接地。CTL输入永远不能连接到VDD。当反序列化程序的ckso输出未使用时,应该允许它浮动。锁相环电路ckref输入信号用于提供锁相环。pll产生内部定时信号,能够以26倍于输入ckref的速度传输数据信号。PLL的输出是用串行数据流。有两种方法可以禁用pll:输入模式0状态(s1=s2=0)或检测到低通电时s1和s2信号。任何其他模式都是通过断言s1或s2高并提供ckref信号输入。锁相环通电后通过锁定序列。等待指定数量的在将有效数据捕获到并行系统之前的时钟周期端口。当μserdes芯片组从断电状态(s1,s2=0,0)到通电状态(例如s1,s2=1,1),反序列化程序上的ckp将在短时间内低转换,然后返回高。之后,ckp处反序列化程序的信号级别对应于序列化程序信号级别。关闭pll的另一种方法是停止ckref信号(高或低)。内部电路检测到缺少转换并关闭PLL串行I/O关闭。然而,内部引用是未禁用,允许PLL通电并重新锁定比退出模式时更少的时钟周期0。当在ckref信号上看到转换时,PLL被重新激活。