AD7893点击型号即可查看芯片规格书

110点击型号即可查看芯片规格书

4096点击型号即可查看芯片规格书

883点击型号即可查看芯片规格书

一般说明

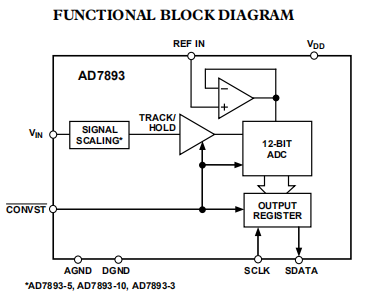

AD7893是一个快速的12位ADC,它从一个+5V电源,安装在小型8针微型DIP和8针SOIC中。该部分包括6μs逐次逼近a/d转换器、片上跟踪/保持放大器、片上时钟和高速串行接口。

AD7893的输出数据通过高速串行接口端口提供。该两线串行接口具有串行时钟输入和串行数据输出,外部串行时钟访问部件的串行数据。

除了线性、满标度和偏移误差等传统的直流精度规范外,AD7893还规定了动态性能参数,包括谐波失真和信噪比。部件接受±10 V(AD7893-10)的模拟输入范围,±2.5 V(AD7893-3)、0 V至+5 V(AD7893-5)或0 V至+2.5 V(AD7893-2)并从单个+5 V电源运行,典型消耗仅为25 mW。

AD7893采用模拟器件的线性兼容CMOS(LC2MOS)工艺制造,这是一种将精密双极电路与低功耗CMOS逻辑相结合的混合工艺。该部件有一个8针0.3英寸宽的小型塑料或密封双列直插式封装(mini-dip)和一个8针小型轮廓集成电路(soic)。

产品亮点

1、8针封装的快速12位ADC

AD7893包含一个6μS ADC、一个跟踪/保持放大器、控制逻辑和一个高速串行接口,全部采用8针封装。这比其他解决方案节省了大量空间。

2、低功率、单电源运行

AD7893由一个+5 V电源供电,耗电量仅为25兆瓦。这种低功耗、单电源操作使其成为电池供电或便携式应用的理想选择。

3、高速串行接口

该部分提供高速串行数据和串行时钟线,允许简单的两线串行接口安排。

术语:信噪比

这是在A/D转换器输出端测得的信噪比(噪声+失真)。信号是基波的均方根振幅。噪声是所有非基本信号的均方根和,不超过采样频率(fs/2)的一半,直流除外。该比率取决于数字化过程中量化层级的数量;层级越多,量化噪声越小。具有正弦波输入的理想n位转换器的理论信噪比为:信噪比(噪声+失真)=(6.02n+1.76)db,因此对于12位转换器,这是74 db。

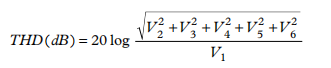

总谐波失真

总谐波失真(thd)是谐波的均方根和与基波的比值。对于AD7893,定义如下:

其中v1是基波的均方根振幅,v2、v3、v4、v5和v6是第二次谐波至第六次谐波的均方根振幅。

峰值谐波或杂散噪声

峰值谐波或杂散噪声被定义为adc输出频谱中下一个最大分量(最高fs/2,不包括dc)的均方根值与基波的均方根值之比。通常,本规范的值由频谱中最大的谐波确定,但对于谐波埋入噪声层的部分,它将是噪声峰值。

互调失真

当输入由两个频率fa和fb的正弦波组成时,任何具有非线性的有源器件都会在mfa±nfb的和频和差频产生畸变产物,其中m,n=0,1,2,3等。互调项是m和n都不等于零的项。例如,二阶术语包括(fa+fb)和(fa-fb),三阶术语包括(2fa+fb),(2fa-fb),(fa+2fb)和(fa-2fb)。

AD7893使用CCIF标准进行测试,其中使用接近输入带宽顶端的两个输入频率。在这种情况下,二阶和三阶项的意义是不同的。二阶项通常在频率上与原始正弦波相距较远,而三阶项通常在接近输入频率的频率上。因此,二阶和三阶术语是分开指定的。互调失真的计算是按照thd规范进行的,其中是单个失真产品的均方根和与以dbs表示的基波的均方根振幅的比值。

相对精度

相对精度或端点非线性是通过adc传递函数端点的直线的最大偏差。

微分非线性

这是ADC中任意两个相邻代码之间的测量值和理想1 LSB变化之间的差值。

正满标度误差(AD7893-10)

这是最后一个代码转换(01)的偏差。…110到01。…111)调整双极零点误差后,从理想的4×ref in–1 lsb(ad7893-10±10 v范围)开始。

正满标度误差(AD7893-3)

这是最后一个代码转换(01)的偏差。…110到01。…111)调整双极零点误差后,从理想值(ref in–1 lsb)开始。

正满标度误差(AD7893-5)

这是最后一个代码转换(11)的偏差。…110到11。…111)调整单极偏移误差后,从理想值(2×ref in–1 lsb)开始。

正满标度误差(AD7893-2)

这是最后一个代码转换(11)的偏差。…110到11。…111)调整单极偏移误差后,从理想值(ref in–1 lsb)开始。

双极零点误差(AD7893-10,10 V;AD7893-3,2.5 V)

这是中尺度跃迁(从0到1)与理想0v(agnd)的偏差。

单极偏移误差(AD7893-2、AD7893-5)

这是第一个代码转换(00)的偏差。…000到00。…001)从理想的1 LSB。

负满标度误差(AD7893-10)

这是第一个代码转换(10)的偏差。…000至10。…001)调整双极零点误差后,从理想值–4×参考输入+1 LSB(AD7893-10±10 V范围)。

负满标度误差(AD7893-3)

这是第一个代码转换(10)的偏差。…000到10。…001)调整双极零点误差后,从理想值(–ref in+1 lsb)。

跟踪/保持采集时间

跟踪/保持捕获时间是在转换结束后(跟踪/保持返回到跟踪模式的点)跟踪/保持放大器的输出达到其最终值(在±1/2 lsb范围内)所需的时间。它也适用于AD7893的车辆识别号输入上的输入电压有阶跃输入变化的情况。这意味着,用户必须在转换结束后或在步骤输入更改为vin之后等待跟踪/保持采集时间的持续时间,然后才能开始另一个转换,以确保部件按规范运行。

转换器详细信息

AD7893是一种快速的12位单电源A/D转换器。它在单片机上为用户提供信号缩放(ad7893-10)、跟踪/保持、a/d转换器和串行接口逻辑功能。AD7893的A/D转换器部分由基于R-2R梯形结构的传统逐次逼近转换器组成。AD7893-10、AD7893-5和AD7893-3上的信号标度允许部件分别处理±10 V、0 V至+5 V和±2.5 V输入信号,同时从单个+5 V电源操作。AD7893-2接受0 V至+2.5 V的模拟输入范围。该部件需要外部+2.5 V参考电压。零件的参考输入在芯片上缓冲。

AD7893的一个主要优点是它在8针封装中提供了上述所有功能,可以是8针mini-dip或SOIC。与其他解决方案相比,这为用户提供了相当大的节省空间的优势。AD7893通常只消耗25兆瓦,非常适合电池供电的应用。

在AD7893上通过脉冲转换器启动转换输入。在convst的上升沿,片上的track/hold从track切换到hold模式,开始转换序列。该部件的转换时钟是使用激光修剪时钟振荡器电路在内部生成的。AD7893的转换时间为6微秒,跟踪/保持捕获时间为1.5微秒。为了从部件获得最佳性能,在转换期间或在下一次转换之前的600 ns期间不应进行读取操作。这允许部件以高达117 kHz的吞吐量运行,并达到数据表规范。该部件可以在更高的吞吐率(高达133kHz)下工作,性能稍有下降(见定时和控制部分)。

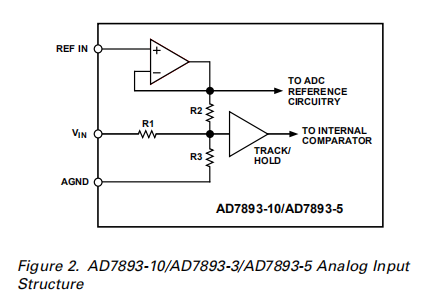

电路描述模拟输入部分

AD7893分为四种类型:AD7893-10,处理±10 V输入电压范围;AD7893-3,处理±2.5 V输入电压范围;AD7893-5,处理0 V至+5 V输入范围;AD7893-2,处理0 V至+2.5 V输入电压范围。

图2显示了AD7893-10、AD7893-5和AD7893-3的模拟输入部分。AD7893-10的模拟输入范围为±10 V,输入电阻通常为33 kΩ。AD7893-3的模拟输入范围为±2.5 V,输入电阻通常为12 kΩ。AD7893-5上的输入范围为0 V至+5 V,输入电阻通常为11 kΩ。该输入是良性的,没有动态充电电流,因为电阻级之后是轨道/保持的高输入阻抗级放大器。对于AD7893-10,r1=30 kΩ;r2=7.5 kΩ,r3=10 kΩ。对于AD7893-3,r1=r2=6.5 kΩ,r3开路。对于AD7893-5,r1和r3=5 kΩ,而r2开路。

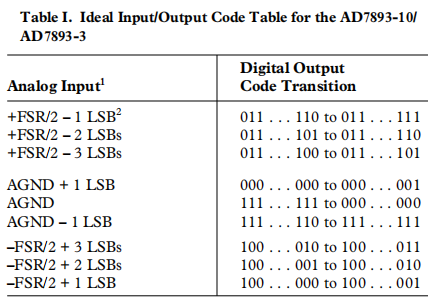

对于ad7893-10和ad7893-3,设计的代码转换发生在连续整数lsb值(即,1 lsb、2 lsb、3 lsb)上。..)输出编码是两个互补二进制,lsb=fs/4096。AD7893-10和AD7893-3的理想输入/输出传递函数如表1所示。

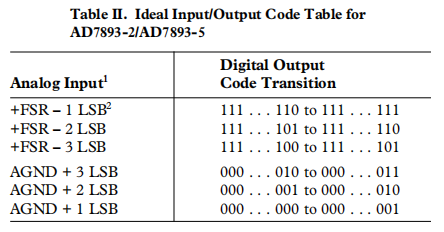

1FSR是满标度范围,为20 V(AD7893-10)和=5 V(AD7893-3),参考电压为+2.5 V;21 LSB=FSR/4096=4.883 mV(AD7893-10)和1.22 mV(AD7893-3),参考电压为+2.5 V;对于ad7893-5,设计的代码转换在连续整数lsb值上再次发生。输出编码为直(自然)二进制,1 lsb=fs/4096=5v/4096=1.22mv。AD7893-5的理想输入/输出传递函数如表二所示。

AD7893-2的模拟输入部分不包含偏置电阻,并且车辆识别号引脚直接驱动输入到跟踪/保持放大器。模拟输入范围为0 V至+2.5 V,进入高阻抗级,输入电流小于500 Na。这个输入是良性的,没有动态充电电流。再次,设计的代码转换发生在连续的整数lsb值上。输出编码为直(自然)二进制,1 lsb=fs/4096=2.5v/4096=0.61mv。表二还显示了AD7893-2的理想输入/输出传递函数。

1FSR是满标度范围,AD7893-5为5 V,AD7893-2为2.5 V,参考电压为+2.5 V;21 LSB=FSR/4096,AD7893-5为1.22 mV,AD7893-2为0.61 mV;参考电压为+2.5 V。

轨道/保持段

AD7893模拟输入端上的跟踪/保持放大器允许ADC将满标度振幅的输入正弦波精确转换为12位精度。跟踪/保持的输入带宽大于adc的奈奎斯特速率,即使adc以其最大吞吐量速率117 kHz(即,轨道/保持可处理超过58 kHz的输入频率)。

跟踪/保持放大器在小于1.5微秒的时间内获得12位精度的输入信号。跟踪/保持的操作对用户基本上是透明的。在转换开始时,跟踪/保持放大器从其跟踪模式转到其保持模式(即康斯特的上升边缘)。光圈时间跟踪/保持(即,外部convst信号和实际进入保持的跟踪/保持之间的延迟时间)通常为15ns。在转换结束时(在convst)部件返回其跟踪模式。跟踪/保持放大器的采集时间从此时开始。

参考输入

AD7893的参考输入是一个缓冲片上输入,最大参考输入电流为1μA。该部件用+2.5V参考输入电压指定。参考源中的错误将导致AD7893传输函数中的增益错误,并将添加到零件上指定的满标度错误中。在AD7893-10上,它还将导致在衰减器级注入偏移误差。AD7893的合适参考源包括AD780和AD680精度+2.5V参考。

定时和控制部分

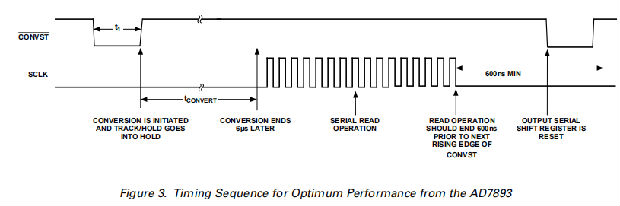

图3显示了从AD7893获得最佳性能所需的时序和控制顺序。按顺序如图所示,转换在convst的上升沿上启动,并且来自该转换的新数据稍后可在ad7893 6微秒的输出寄存器中获得。一旦进行了读取操作,在下一次读取之前,应允许再读取600 ns,在开始下一次转换之前,convst的上升沿优化跟踪/保持放大器的设置。在串行时钟频率最大为8.33 mhz的情况下,该部件的可实现吞吐量为6微秒(转换时间)加1.92微秒(读取时间)加0.6微秒(采集时间)。这导致最小吞吐量时间为8.52微秒(相当于117 kHz的吞吐量速率)。

读取操作包括16个串行时钟脉冲到AD7893的输出移位寄存器。在16个串行时钟脉冲之后,移位寄存器被重置,sdata线被三次声明。如果在第十六个时钟之后有更多的串行时钟脉冲,移位寄存器将在其复位状态之后移动;但是,移位寄存器将在下降沿上再次复位

以确保每个转换周期部件返回到已知状态。因此,输出寄存器的读取操作不应跨越下降convst的边缘作为输出移位寄存器将在读取操作的中间被重置,并且读回微处理器的数据将显示为无效。

通过读取可以提高部件的吞吐量转换期间的数据。如果在转换期间读取数据,则实现6微秒(转换时间)加1.5微秒的吞吐量时间。该最小吞吐量时间为7.5微秒与AD7893相比性能略有下降。当来自部件的代码闪烁也将增加时(参见ad7893性能部分),到(噪声+失真)的信号数可能降低约1.5db。

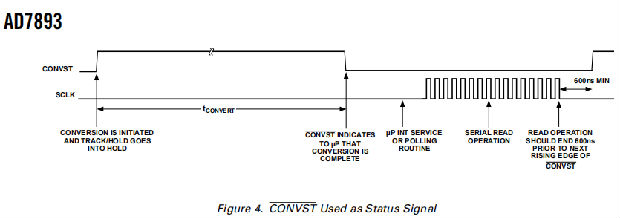

由于AD7893以8针封装的方式提供,以尽量减少板空间,因此可用于接口的针数非常有限。结果,没有从ad7893提供状态信号来指示转换何时完成。在许多应用中,这不会是一个问题,因为可以在转换期间或转换之后从ad7893读取数据;但是,想要从ad7893获得最佳性能的应用必须确保在转换期间或在上升之前的600 ns期间不会发生数据读取。convs的边缘。这可以通过两种方式实现。第一个是确保在软件中,直到convst上升沿后6微秒才开始读取操作。只有当软件知道何时发出convst命令时,才能执行此操作。第二种方案是使用convst信号作为转换开始信号和中断信号。最简单的方法是用6微秒的高低倍为convst产生方波信号(见图4)。转换在convst的上升沿启动。convst的下降沿在6微秒后出现,可以用作激活的低或下降沿触发中断信号,以告诉处理器从ad7893读取数据。如果读取操作在上升前600 ns完成转换器边缘,AD7893将按规格工作。

此方案将吞吐率限制为最小12微秒;但是,根据微处理器对中断信号的响应时间和处理器读取数据所用的时间,这可能是系统运行的最快速度。无论如何,convst信号不必具有50:50占空比。这可以定制以优化给定系统的部件吞吐量。或者,convst信号可以用作正常的窄脉冲宽度。convst的上升沿可用作激活的高或上升沿触发中断。然后,在从部件读取数据之前,可以实现6微秒的软件延迟。

串行接口

AD7893的串行接口仅由两根导线、串行时钟输入(SCLK)和串行数据输出(SData)组成。这使得一个易于使用的接口,大多数微控制器,数字信号处理器和移位寄存器。

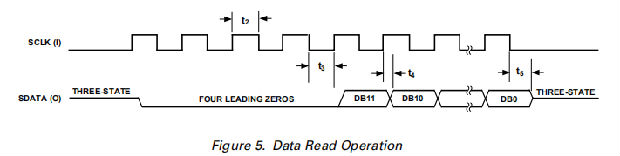

图5显示了AD7893读取操作的时序图。串行时钟输入(SCLK)为串行接口提供时钟源。串行数据从该时钟上升沿上的SData线打卡,在SCLK下降沿上有效。必须为部件提供16个时钟脉冲,以获得完整的转换结果。AD7893提供四个前导零,后跟以msb(db11)开头的12位转换结果。最后一个在最后一个上升时钟边缘上计时的数据位是lsb(db0)。在SCLK的第十六个下降沿上,SData线被禁用(三个状态)。在最后一个位被打卡后,SCLK输入应返回低电平并保持低电平,直到下一个串行数据读取操作。如果在第十六个时钟之后有额外的时钟脉冲,AD7893将从其输出寄存器输出数据重新开始,并且即使时钟停止,数据总线也不再是三个状态。如果串行时钟在convst的下一个下降沿之前停止,则AD7893将继续正常工作,输出移位寄存器将在convst的下降沿上重置;但是,当convst变低时,SCLK线必须为低,以便正确重置输出移位寄存器。

串行时钟输入在串行读取操作期间不必连续。十六位数据(四个前导零和12位转换结果)可以从AD7893中读取若干字节;但是,SCLR输入必须在两个字节之间保持低位。

通常,输出寄存器在转换结束时更新。如果在转换完成时正在从输出寄存器进行串行读取,则延迟输出寄存器的更新。在这种情况下,当串行读取完成时,输出寄存器被更新。如果串行读取在convst的下一个下降沿之前没有完成,则输出寄存器将在convst的下降沿上更新,并且输出移位寄存器计数被重置。在应用程序中,数据读取在下降之前已启动但尚未完成。在convst的边缘,用户必须提供大于1.5微秒的convst脉冲宽度,以确保在开始下一次转换之前正确设置ad7893。在转换结束时或在convst上升沿前1.5μs完成的串行读取结束时进行输出更新的应用中,最小50 ns的正常脉冲宽度适用于convst。

AD7893对串行时钟边缘进行计数,以知道输出寄存器中的哪个位应放在SData输出上。为了确保部件不会失去同步,请串行时钟计数器在convst输入的下降沿上复位,前提是sclr线较低。用户应确保在进行串行数据读取操作时,convst输入不会出现下降沿。

微处理器/微控制器接口

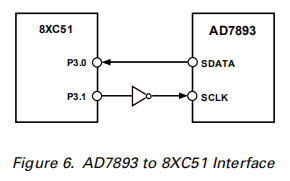

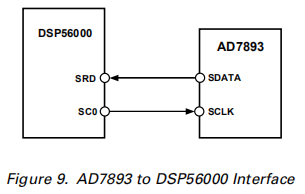

AD7893提供两线串行接口,可用于连接到DSP处理器和微控制器的串行端口。图6到9显示了AD7893与许多不同的微控制器和数字信号处理器的接口。AD7893接受一个外部串行时钟,因此,在这里所示的所有接口中,处理器/控制器被配置为主机,提供串行时钟,而AD7893被配置为系统中的从机。

AD7893-8051接口

图6显示了AD7893和8XC51微控制器。8XC51配置为其模式0串行接口模式。该图显示了接口的最简单形式,其中AD7893是连接到8XC51串行端口的唯一部件,因此不需要对串行读取操作进行解码。它也没有规定在AD7893上完成转换时进行监控。

这两个任务中的任何一个都可以通过对接口的微小修改来轻松完成。要在多个设备连接到8XC51串行端口的系统中芯片选择AD7893,配置为8XC51并行端口之一输出的端口位可用于接通或断开AD7893的串行时钟。此端口位上的一个简单和功能以及8XC51的串行时钟将提供此功能。端口位应高以选择AD7893,未选择时应低。

为了监视ad7893上的转换时间,一个这样的方案如前所述,可以使用convst。这可以以两种方式实现。一种是将convst线连接到另一个配置为输入的并行端口位。然后可以轮询此端口位以确定转换何时完成。另一种方法是使用中断驱动系统,在在这种情况下,convst线应连接到8xc51的int1输入端。

来自8XC51的串行时钟频率被限制为明显低于AD7893可以工作的允许输入串行时钟频率。因此,从这个部分实际上比这个部分的转换时间要长。这意味着AD7893不能以最大值运行与8XC51一起使用时的吞吐量。

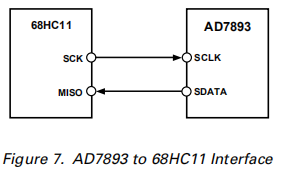

AD7893-68HC11接口

AD7893和68HC11微控制器之间的接口电路如图7所示。对于所示的接口,使用68HC11 SPI端口,并且68HC11以其单片机模式配置。68HC11在主模式下配置,其cpol位设置为逻辑零,其cpha位设置为逻辑一。与前面的接口一样,该图显示了接口的最简单形式,其中ad7893是连接到68hc11的串行端口的唯一部分,因此,不需要对串行读取操作进行解码。它也没有规定在AD7893上完成转换时进行监控。

再一次,这两个任务中的任何一个都可以通过对接口的微小修改来轻松完成。要在多个设备连接到68HC11串行端口的系统中芯片选择AD7893,配置为68HC11并行端口之一的输出的端口位可用于接通或断开AD7893的串行时钟。这个端口位上的一个简单的函数和68HC11的串行时钟将提供这个函数。端口位应高以选择AD7893,未选择时应低。

为了监视ad7893上的转换时间,一个这样的方案。如前一个convst接口中所述,可以使用。这可以通过两种方式实现。一是联系到另一个配置为输入的并行端口位的convst行。然后可以轮询此端口位以确定转换何时完成。另一种方法是使用中断驱动系统,在这种情况下,转换线应连接到68HC11的IRQ输入端。

68HC11的串行时钟速率被限制为明显小于AD7893可以工作的允许输入串行时钟频率。因此,从部件读取数据的时间实际上要比部件的转换时间长。这意味着当AD7893与68HC11一起使用时,它不能以最大吞吐量运行。

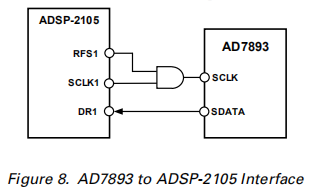

AD7893–ADSP-2105接口

ad7893与adsp-2105的接口电路数字信号处理器如图8所示。在所示的接口中,来自ADSP-2105的SPORT1串行端口的RFS1输出用于在ADSP-2105的串行时钟(SCLK1)应用于AD7893的SCLK输入之前对其进行选通。RFS1输出配置为高电平运行。接口确保AD7893串行时钟输入的时钟不连续,仅提供16个串行时钟脉冲,并且AD7893的串行时钟线在数据传输之间保持低位。来自AD7893的SData线连接到ADSP-2105串行端口的DR1线。

adsp-2105的sclk1和rfs1输出之间的时序关系使得sclk1的上升沿和有源高rfs1的上升沿之间的延迟高达25ns。还要求在SCLK1下降边缘前10 ns设置数据,以便ADSP-2105正确读取。AD7893的数据访问时间是从其SCLK输入的上升沿开始的50ns。假设通过外部和栅极的传输延迟为10ns,则adsp-2105的sclk1输出的高时间必须≥(50+25+10+10)ns,即≥95ns。这意味着图13的接口可以使用的串行时钟频率被限制在5.26mhz。

另一种方案是将adsp-2105配置为接受外部串行时钟。在这种情况下,提供驱动adsp2105和ad7893的串行时钟输入的外部非连续串行时钟。在该方案中,adsp-2105将串行时钟频率限制在5mhz。为了监视ad7893上的转换时间,可以使用与convst的先前接口中概述的方案。这可以通过连接convst线来实现直接到ADSP-2105的IRQ2输入。

AD7893–DSP56000接口

图9显示了AD7893和DSP56000 DSP处理器之间的接口电路。DSP5600配置为带门控时钟的正常模式异步操作。它还设置为16位字,门控串行时钟由DSP56000生成并显示在SC0引脚上。应通过将位scd0设置为1将sc0引脚配置为输出。在此模式下,DSP56000以串行读取操作向AD7893提供16个串行时钟脉冲。DSP56000假设SCK的第一个下降沿上有有效数据,因此接口只是两线制的,如图9所示。

为了监视ad7893上的转换时间,可以使用如前面convst接口示例中概述的方案。这可以通过连接convst来实现直接连接到DSP56000的IRQA输入。

AD7893性能线性

AD7893的线性度由片上12位D/A转换器决定。这是一个分段的dac,它被激光修剪为12位积分线性和微分线性。零件的典型相对数为±1/4 LSB,而典型的DNL误差为±1/2 LSB。

噪声

在a/d转换器中,噪声在直流应用中表现为码的不确定性,在交流应用中表现为噪声地板(例如在fft中)。在像ad7893这样的采样a/d转换器中,从dc到采样频率的1/2,所有关于模拟输入的信息都出现在基带中。磁道/保持的输入带宽超过奈奎斯特带宽;因此,在存在此类信号的应用中,应使用抗混叠滤波器去除输入信号中fs/2以上的不需要信号。

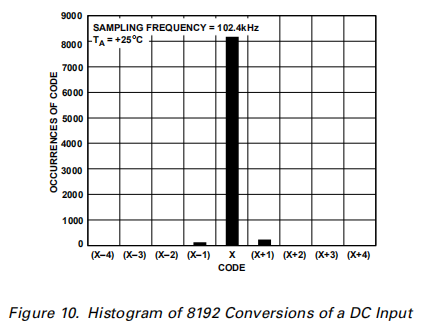

图10显示了使用AD7893进行8192次DC输入转换的直方图。模拟输入设置在代码转换的中心。所用的时序和控制顺序如图3所示,其中ADC的性能达到最佳。可以看出,几乎所有的代码都出现在一个输出箱中,这表明adc具有非常好的噪声性能。上述图中AD7893-2的均方根噪声性能为87μV。由于AD7893-10上的模拟输入范围和LSB大小是AD7893-2的八倍,相同的输出码分布导致AD7893-10的输出均方根噪声为700μV。

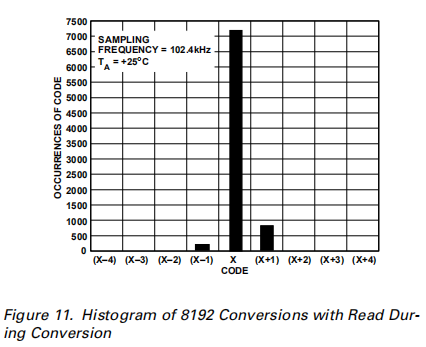

图11中显示的数据与图10中显示的数据相同,只是在这种情况下,为设备读取的输出数据发生在转换期间。这会在进行位决策时将噪声注入模具;这会增加AD7893产生的噪声。同一dc输入的8192次转换的直方图图现在显示,随着ad7893-2的rms噪声增加到210μv,码的更大扩展。此效果将根据转换过程的位试验的串行时钟边缘出现的位置而变化。根据串行基座边缘与位试用点之间的关系,在转换期间读取时可能达到与在转换之后读取时相同的性能水平。

动态性能

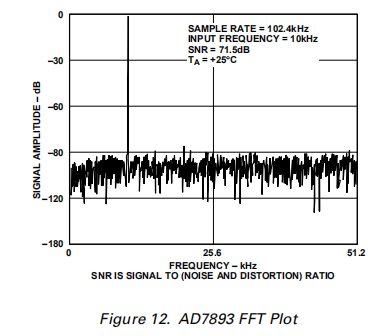

AD7893具有7.5微秒的转换和采集时间,是宽带信号处理应用的理想选择。这些应用需要有关ADC对输入信号光谱含量影响的信息。规定了信噪比、总谐波失真、峰值谐波或杂散噪声、互调失真。图12显示了AD7893-2数字化后,在102.4kHz采样率下工作的10 kHz、0 V至+2.5 V输入的典型FFT图。信噪比为71.5db,总谐波失真为-83db。

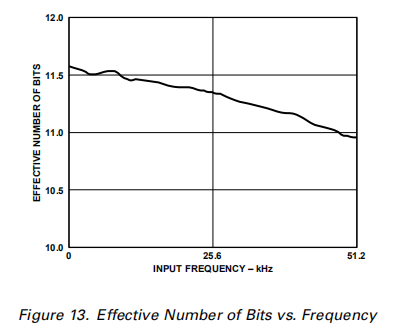

有效位数

信噪比(噪声+失真)的公式(见术语部分)与转换器的分辨率或位数有关。重写公式给出了以有效位数(n)表示的性能度量:n=(信噪比-1.76)/6.02 ; 其中snr是信噪比。

设备的有效比特数可以根据其测量的信号与(噪声+失真)的比率来计算。图13显示了AD7893-2从DC到F采样/2的有效位数与频率的典型关系图。采样频率为102.4khz。该图显示,ad7893将51.2khz的输入正弦波转换为11的有效位数,相当于68分贝的(噪声+失真)电平的信号。