3000点击型号即可查看芯片规格书

4095点击型号即可查看芯片规格书

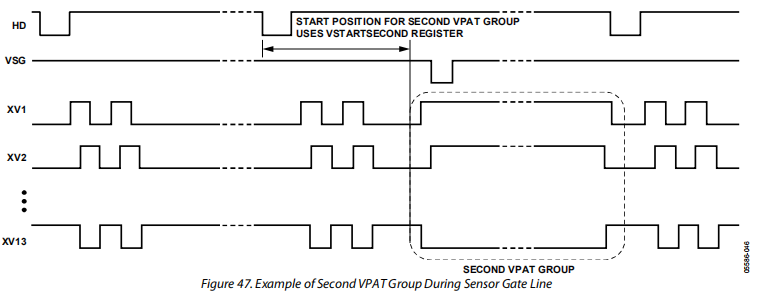

vsg活动线和特殊v型插入时的第二个v型组

大多数ccd在传感器门线期间需要额外的垂直定时。当VSG1至VSG8传感器门激活时,AD9923A可以在线路期间为XV1至XV13输出第二个V型组。图47显示了一条典型的vsg线,其中包括两组v1到v13的v模式组。在vsg行的开头,使用适当的vseqsel寄存器选择v模式组。第二个v型组是vsg线所特有的,使用位于字段寄存器中的vpatsecond寄存器来选择。第二个vpat组的起始位置使用vstartsecond寄存器。

除了在vsg线中插入第二v模式外,ad9923a还可以在每个序列中的任何其他单行中插入第二v模式。要在特定序列中启用此功能,请将相应序列寄存器集中的spxv_en寄存器设置为1。SPXV U ACT寄存器确定特殊第二V模式的激活线。vpatselb和vstartb寄存器控制使用的v模式和特殊的第二v模式的起始像素位置。

为了避免不希望的行为,不要使用特殊的第二个,在vsg行中的v模式;使用现有的vpatsecond和vstartsecond寄存器将第二个v模式插入vsg行。建议使用vpatsecond和vstartsecond寄存器在传感器栅极线而不是groupb寄存器中创建复杂的定时。另外,考虑到特殊的第二v模式插入使用了b组寄存器中的一些,用户不能以相同的顺序使用特殊的第二v模式插入功能和b组。

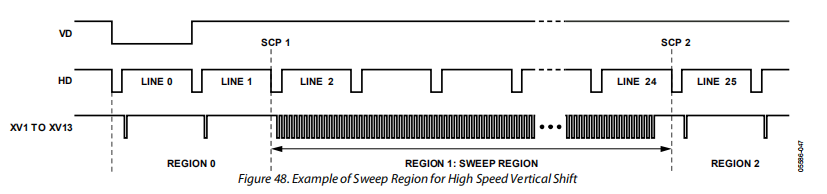

扫描模式操作

AD9923A包含一种称为扫描模式的附加垂直定时操作模式。该模式用于产生跨越多个hd线的大量重复脉冲。通常,ad9923a的垂直定时必须包含在一个hd行长度内,但是当启用扫描模式时,hd边界将被忽略,直到区域完成为止。例如,这在ccd读出操作中是有用的。根据ccd的垂直分辨率,可以要求跨越几个hd线长度的多达3000个时钟周期将电荷移出垂直线间ccd寄存器。在图像传输之前,这些寄存器在图像曝光结束时必须免费。这可以在扫描模式下通过使用从xv1到xv13输出的一系列长脉冲快速转移出任何电荷来实现。要在任何区域启用扫描模式,请将相应的扫描寄存器编程为高。

图48显示了扫描模式操作的示例。所需的垂直脉冲数取决于ccd的垂直分辨率。xv1到xv13的输出信号是使用v型寄存器生成的(如表15所示)。使用极性和切换位置寄存器创建单个脉冲。然后对重复次数进行编程,以匹配ccd所需的垂直位移次数。重复使用vrep寄存器在v序列寄存器中编程。这会产生一个适当长度的脉冲序列。通常,脉冲串在hd线长度的末端被截断,但是在启用扫描模式的情况下,hd边界被忽略。在图48中,扫描区域占据23条高清线。扫描模式区域完成后,在下一个区域恢复正常的序列操作。使用扫描模式时,使用序列改变位置寄存器将区域边界设置到适当的行,以防止扫描操作与下一个V序列重叠。

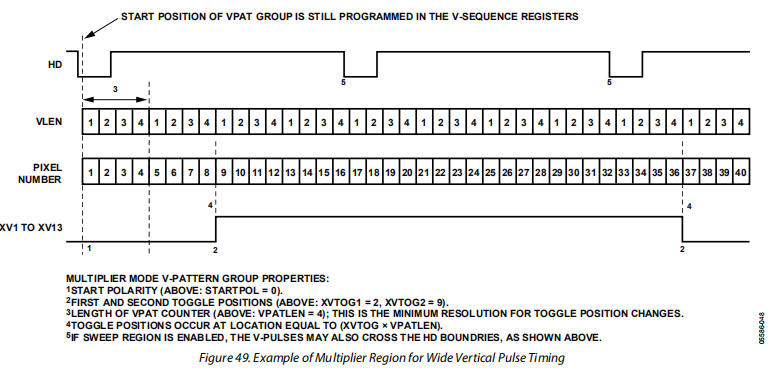

倍增模式

为了产生非常宽的垂直定时脉冲,可以将垂直区域配置成乘法器区域。此模式以稍微不同的方式使用v型寄存器。乘法器模式可用于支持不寻常的ccd定时要求,例如比13位v型切换位置计数器宽的垂直脉冲。起始极性和切换位置的使用方式与标准vpat组编程相同,但vlen寄存器的使用方式不同。而不是使用像素计数器(hd counter)来指定切换位置(xvtog1、xvtog2、xvtog3、xvtog4、xvtog5和xvtog6)在vpat组中,vlen值乘以xvtog值,以生成非常长的脉冲。要计算精确的切换位置(以开始位置后的像素为单位),请使用以下公式:倍增模式切换位置=xvtog×vlen,因为xvtog值乘以vlen值,所以切换位置放置的分辨率降低。如果vlen=4,则切换位置精度将降低为4个像素步,而不是单个像素步。在乘法器模式操作中如何使用vpat组寄存器。在倍增模式下,VREP寄存器应编程为最高切换位置的值。

图49所示的示例说明了此操作。第一个切换位置是2,第二个切换位置是9。在非乘法器模式下,这会导致v序列在单个hd行内的像素2和像素9处切换。然而,在倍增模式中,切换位置乘以vlen=4;因此,第一个切换发生在像素计数=8处,第二个切换发生在像素计数=36处。扫描模式也启用,以允许切换位置跨越高清线边界。多功能仅适用于分配给A组的信号。它不能与两组功能同时使用,或者如果有任何信号分配给B组。

垂直传感器门(换档门)模式

在行间ccd中,垂直传感器栅极(vsg)用于将像素电荷从感光图像区域传输到遮光垂直寄存器中。然后,使用xv1到xv13垂直传输脉冲和高速水平时钟,从遮光垂直寄存器逐行读取图像。

vsg模式寄存器。AD9923A有八个VSG输出,VSG1到VSG8。通过使用SGPATSEL寄存器,可以将每个输出分配给八个编程模式中的一个。每一个图形以与v形图形组相似的方式生成,具有可编程的起始极性(sgpol)、第一拨动位置(sgtog1)和第二拨动位置(sgtog2)。发生VSG1到VSG8脉冲的激活线路可使用SGactLine1进行编程。vsg模式寄存器1和sgactline2寄存器。此外,可以使用sgmask寄存器单独禁用任何vsg1到vsg8脉冲。单独的掩蔽允许对所有sg模式进行预编程,并且可以分别为每个场启用适当的脉冲。为了获得最大的灵活性,sgpatsel、sgmask和sgactline寄存器分别为每个字段编程。在完整的领域中给出了更多的细节:组合v序列部分。

此外,还有sgmask_byp寄存器(地址0x59)重写字段寄存器中的sg mask。sgmask_byp寄存器允许在不修改字段寄存器值的情况下更改传感器门屏蔽。sgmask_byp寄存器被sck更新;因此,新的sg掩码值立即更新。

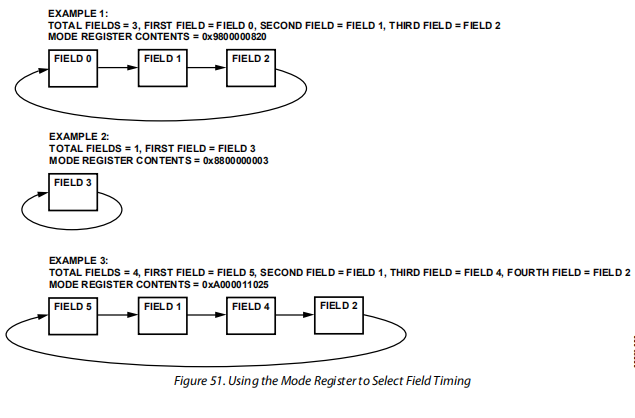

模式寄存器

模式寄存器是一个单独的寄存器,用于选择AD9923A的字段计时。通常,所有字段、V序列和V模式组信息在启动时编程到AD9923A中。在操作过程中,模式寄存器允许用户选择任何现场定时组合,以满足系统的当前要求。将模式寄存器与预编程定时结合使用,大大降低了相机运行期间的系统编程要求。当相机工作模式改变时,只需要少量寄存器写入,而不必在每次相机模式改变时重写垂直定时信息。

一个基本的静态相机应用程序可能需要五个垂直计时字段,一个用于草稿模式操作,一个用于自动对焦,三个用于静态图像读取。五个字段的寄存器计时信息在启动时加载。根据相机的使用方式,模式寄存器选择在相机操作期间激活的场定时。

模式寄存器内容VD已更新

如何使用模式寄存器位。与其他寄存器不同,模式寄存器使用10个地址位作为数据位,将寄存器总大小增加到38位。地址msb a11和a10分别为1和0,用于指定模式寄存器write。三个msb d37、d36和d35用于指定使用的字段数。可以使用这三个位选择1到7之间的值。剩余的寄存器位被分为五个位段,以选择使用哪些编程字段以及使用的顺序。在单模式写入中最多可以使用七个字段。AD9923A从第一个字段位指定的字段定时开始,切换到下一个虚拟磁盘上第二个字段位指定的定时,依此类推。

垂直计时示例

为了更好地理解如何使用AD9923A垂直定时生成,请考虑图52中的示例CCD定时图。它说明了一个使用一般三场读出技术的ccd。如完整字段中所述:组合v序列部分,应将每个读出字段划分为单独的区域以执行读出的每个步骤。序列改变位置(SCP)寄存器决定每个区域的行边界。然后,vseqsel寄存器为每个区域分配一个v序列。每个v序列包含每个区域所需的特定定时信息:xv1到xv6脉冲(使用vpat组)、hblk/clpob定时和sg激活线路的vsg模式。

示例要求为三个字段中的每一个字段提供四个区域,分别标记为区域0、区域1、区域2和区域3。由于AD9923A允许对许多单独的字段进行编程,因此可以创建字段0、字段1和字段2以满足此计时示例的要求。在本例中,每个字段的四个区域非常相似,但是每个字段的单个寄存器允许灵活性以适应更复杂的计时要求。

区域0

区域0是高速垂直移动区域。扫描模式可用于产生该定时操作,所需的高速垂直脉冲数用于清除ccd垂直寄存器中的任何电荷。

区域1

区域1由两条线组成,使用标准、单线、垂直移位计时。该区域的定时与区域3的定时相同。

区域2

区域2是传感器栅极线,其中vsg脉冲将图像传输到垂直ccd寄存器。该区域可能需要使用SG激活线路的第二个V型组。

区域3

区域3还使用标准的、单线的、垂直移位定时,与区域1中使用的定时相同。总之,三个字段中的每个字段都需要四个区域。

区域1和区域3的定时基本相同,降低了寄存器编程的复杂性。其他在读出操作期间,必须使用寄存器,例如模式寄存器、快门控制寄存器(即触发器和控制subck、vsub、mshut和strobe输出的寄存器)以及afe增益寄存器vgaain和cdsgain。这些寄存器在模式寄存器和可变增益放大器部分中进行了说明。

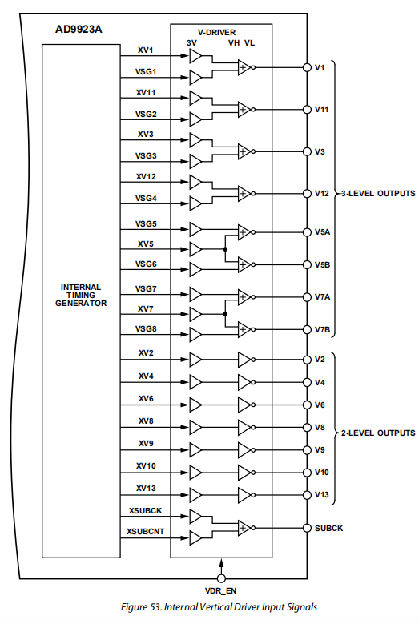

垂直驱动信号配置

如图53所示,XV1到XV13、VSG1到VSG8和Xsubck是内部AD9923A定时发生器的输出,而v1到V13和Subck是AD9923A垂直驱动器的输出。当vdr_en=高时,垂直驱动器将xv和vsg脉冲混合,并将其放大到驱动ccd所需的高电压。表22至表37描述了这些信号的输出极性与输入电平的关系。在确定所需输出电平的寄存器设置时,请参考这些表。注意,当vdr_en=low时,v1到v13被强制设置为vm,subck被强制设置为vll。VDR_en管脚优先于来自正时发生器的XV和VSG信号。

快门定时控制

ccd图像曝光时间由基板时钟信号(subck)控制,该信号脉冲ccd基板以清除累积电荷。AD9923A支持三种类型。电子快门:正常、高精度、低速。AD9923A与SubCK脉冲放置一起,可容纳不同的读出配置,以在多个场读出期间进一步抑制SubCK脉冲。AD9923A还提供可编程输出,以控制外部机械快门(MSHUT)、频闪/闪光(频闪)和CCD偏压选择信号(VSUB)。最多可以对四个常规快门脉冲(shut0到shut3)和两个vsub脉冲(vsub0和vsub1)进行编程并分配给三个快门输出管脚中的任何一个。用户还可以组合以下内容具有逻辑异或操作(符号化)的快门和vsub脉冲通过^)为mshut、strobe和vsub生成更复杂的计时(每行最多四个切换位置):shut0^vsub0、shut0^vsub1、shut0^shut1和shut0^shut2。

subck:三电平输出

AD9923A支持从subck缓冲区输出三级:vh、vmm和vll。vh电源与v驱动器输出共享,但vmm和vll是subck缓冲区的专用中低压电源。subck缓冲区有两个输入:xsubck和xsubcnt。XSBCNT是由一个内部多路复用器创建的,该多路复用器可从xv1到xv13、vsg1到vsg8、mshut、strobe、vsub、shut0到shut3、fg_trig、high和low进行选择。

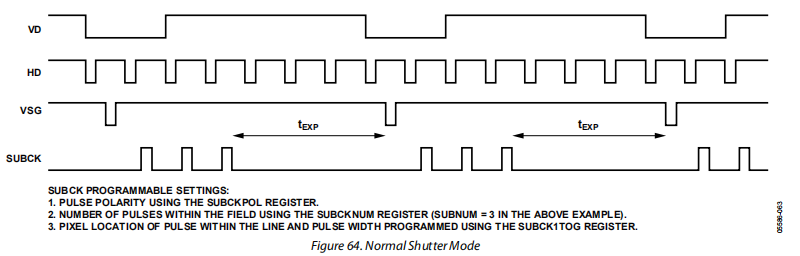

默认情况下,AD9923A以正常的SUBCK配置运行,SUBCK信号在每个VD字段中脉冲(见图64)。每行发生一次次次亚光速脉冲,场中的总重复次数决定曝光时间。使用subckpol和subck1tog寄存器,线路内的subck脉冲极性和切换位置是可编程的。每个字段的subck脉冲数在subcknum寄存器(地址0x64)中编程。

如图64所示,subck脉冲总是从sg active行之后的行开始(在每个字段的sgactline寄存器中指定)。subckpol、subck1tog、subck2tog、subcknum和subcksuppress寄存器,如更新新寄存器值部分所述,在传感器门线之后的线的开始处更新。

subck:高精度操作

高精度的模板使用与普通模板相同的方式,但使用额外的寄存器来控制最后的subck脉冲。在该模式下,每行一次subck脉冲,但字段中的最后一个subck有一个额外的subck脉冲,其位置由subck2togx寄存器确定,如图65所示。使用此模式可以获得更高的曝光时间分辨率。将subck2togx寄存器设置为其最大值(0xffffff)将禁用最后一个subck脉冲(默认设置)。

Subck:低速运行

当曝光时间小于一个场长时,使用常规和高精度快门操作。对于超过一个场间隔的曝光时间,使用低速快门操作。AD9923A使用单独的曝光计数器来实现长曝光时间。低速快门操作的字段数在exposurenum寄存器(地址0x63)中指定。如图66所示,该快门模式抑制0场以上的subck和vsg输出到4095个字段(虚拟磁盘周期)。VD和HD输出可以是在曝光期间通过编程vdhdoff寄存器设置为1。

为了产生低速快门操作,通过写入触发寄存器位d3来触发长曝光。当该位设置为高时,ad9923a在下一vd边缘开始曝光操作。如果在exposurenum寄存器中指定了大于0的值,则AD9923A会抑制后续字段上的subck输出。

如果使用触发寄存器生成曝光,并且exposurenum寄存器设置为0,则subck的行为与正常快门操作或高精度快门操作(其中不使用触发寄存器)期间的行为相同。

subck:抑制

通常,subck开始在传感器栅极线(vsg)之后的线上脉冲。一些ccd需要抑制vsg线之后的一条或多条线路的子k脉冲。subcksuppress寄存器启用这种抑制。

曝光后读数

曝光后,从传感器栅极(vsg)操作开始读取ccd数据。默认情况下,AD9923A在每个字段中生成VSG脉冲。当只需要一个曝光和读出帧时,就像在ccd预览模式中一样,vsg和subck脉冲可以在每个场中工作。

然而,通常在读出期间,必须抑制subck输出直到读出完成。readoutnum寄存器指定曝光后的附加字段数,以继续抑制subck。readoutnum可以编程为0到7个字段,并且应该在启动时预编程,而不是在曝光写入的同时。典型的隔行扫描ccd帧读出模式在读出过程中通常需要两个抑制亚光速的场(readoutnum=2)。三场六相ccd在读出开始后需要三个抑制亚光速的场(readoutnum=3)。如果在最后一个读出字段期间需要subck输出来启动备份,则将readoutnum寄存器编程为小于ccd读出字段总数的一个。与曝光操作类似,读出操作必须使用触发寄存器触发。

subck:附加掩蔽

subckmask寄存器(地址0x65)允许更复杂的subck掩蔽。如果subckmask=1,它将开始屏蔽在下一个虚拟磁盘边缘执行Subck。如果subckmask=2,它允许用户选择内部shut3信号并创建跨多个字段的自定义subck掩蔽模式。

如先前在曝光后读出部分中所述,当使用触发寄存器生成曝光时,ad9923a默认地在每个场上输出subck和vsg信号。这对于连续的单场曝光和读出操作(如ccd实时预览模式下的操作)很有效。然而,如果ccd需要更长的曝光时间,或者如果需要多个读出场,则需要触发寄存器来启动特定的曝光和读出序列。

通常,触发寄存器中的曝光和读出位一起使用。这将启动一个完整的曝光加读出操作。曝光后,读数自动发生。exposure和readoutnum寄存器中的值决定每个操作的长度。

可以在不触发曝光操作的情况下独立地触发读出操作。这导致在下一个vd处发生读出,并且根据在readoutnum寄存器中设置的值抑制subck输出。

触发器寄存器还控制shut和vsub信号。每个信号单独控制,但取决于曝光和读出操作的触发。有关触发曝光和读出操作的完整示例。

或者,可以通过在每个vd字段上小心地更新subcksuppress和vsg掩蔽寄存器来手动控制曝光和读出操作。如以下各节所述,可以对快门信号进行部分或全部手动控制。这样可以在生成自定义曝光/读出/快门信号定时。

快门输出

AD9923A包含三个快门输出管脚:vsub、mshut和频闪。在内部,有六种可能的快门信号可用:vsub0、vsub1、shut0、shut1、shut2和shut3。这些信号中的任何一个,以及以下组合:shut0 ^vsub0,shut0 ^vsub1,shut0 ^shut1,shut0 ^shut2,可以使用vsub_ctrl、mshut_ctrl和strobe_ctrl寄存器映射到任何输出管脚。vsub信号的行为与关闭信号不同,通常用于vsub输出管脚。如果对快门信号需要更通用的方法,则可以将关闭信号用于vsub输出管脚。也可以将同步管脚配置为输出,并使用testo_ctrl register函数将内部快门信号之一或以上列出的组合发送到同步管脚。这提供了在不需要外部同步输入功能的情况下最多输出四个快门输出的灵活性。

vsub信号操作

ccd读出偏置(vsub)可以编程以适应不同的ccd。图67显示了两种可用的模式。在模式0中,当曝光在最后一个子帧的场中开始时,vsub变为活动状态。开启位置(图67中的上升沿)可编程为现场内的任何线路。在图像读出结束之前,vsub一直处于活动状态。在模式1中,直到读出开始,vsub才被激活。还有一个名为vsub_keepon的函数。当适当的vsub_keepon位设置为高时,vsub输出保持激活,即使在读出完成之后。要在以后禁用vsub,请将此位返回低位。

AD9923A包含两个可编程的VSUB信号:VSUB0和VSUB1。这些信号可以映射到vsub输出管脚、mshut管脚或选通管脚。

关闭信号操作

关闭信号操作:关闭信号有三种不同的使用方法:自动触发、单次触发和手动控制。

自动触发器

通常,关闭信号与曝光或读出操作一起使用触发寄存器触发。使用现场,关闭和关闭位置可完全编程到曝光期内的任何地方(关机/关机)、线路(关机/关机)和像素(关机/关机)寄存器。

字段寄存器根据曝光计数器的值定义使用行和像素值的字段。打开和关闭位置可以在该字段包含最后一个subck(曝光字段0)时出现,或者在读出开始之前最迟出现在最后一个曝光字段。单独的字段寄存器允许在不同的曝光字段中出现打开和关闭位置。

单触发器

关闭信号可以在不触发曝光或读出操作的情况下触发。在这种情况下,使用触发寄存器触发关闭信号,但不触发曝光位。关闭和打开位置都出现在下一个字段中,并且忽略关闭/关闭寄存器值。如果在下一个场中立即需要脉冲而不发生曝光或读出操作,则单触发操作是有用的。此外,当在不使用触发寄存器的情况下手动生成曝光或读出操作,并且手动控制subck和vsg掩蔽时,单触发操作是有用的。

请注意,如果已触发曝光操作,则不能执行单触发操作。自动关闭信号;触发模式,如果它们和曝光操作已被触发。

手动控制

任何关闭信号都可以在手动控制模式下控制,而不是使用触发寄存器来激活它。在该模式下,根据手动信号控制寄存器的状态,单独的开、关线和像素位置被单独使用。注意,在VD间隔中只能使用一个开关位置,无论是关闭还是打开。与单触发操作一样,当启用手动控制时,将忽略shut_on_fd/shut_off_fd寄存器值。

由于有一个单独的位可以对关闭信号启用手动控制,因此无论触发曝光操作的状态如何,都可以使用此操作。

注意:(1)、手动控制可与自动或单触发操作一起使用。如果使用手动控制打开关闭信号,然后禁用手动控制,则关闭信号保持打开。如果发生后续触发操作,则忽略“打开位置”切换,因为信号已打开。在这种情况下,只能触发关闭位置。(2)、AD9923A上关闭信号的触发机制与AD9923不同。在AD9923上,触发信号在写入触发寄存器(寄存器0x61)的字段的更新行(寄存器0x18)上更新。如果关闭信号的触发位在给定字段中被停用,这将导致忽略更新行之后发生的关闭信号的任何切换位置。在AD9923A中,在写入触发寄存器之后,内部触发信号在整行中保持激活状态。在这种情况下,处理更新行后编程的任何切换位置。

触发操作

AD9923A包含一个附加信号,可与快门操作或一般系统操作一起使用。fg_触发信号是一个内部产生的脉冲,可以在快门或其他系统功能的同步管脚上输出。fg_trig信号的一个独特特征是,它是相对于模式寄存器字段状态输出的。

fg_trig信号是使用shut1起始极性和切换位置寄存器生成的,可编程为线和像素分辨率。SHUT1的字段寄存器被忽略,因为fg_触发脉冲的字段位置与模式寄存器操作指定的字段计数相匹配。fg_trigen寄存器包含一个三位值,指定哪个字段计数包含fg_trigen脉冲。图72显示了如何使用这些寄存器生成fg_触发脉冲。指定fg_trig信号后,可以使用fg_trigen寄存器的位3启用它。如果同步管脚配置为输出(syncenable=0),则fg_trig信号映射到同步输出。

模拟前端描述/操作

AD9923A信号处理链如图73所示。每一步都是从原始ccd像素数据中获得高质量图像的关键。

直流恢复

为了减小ccd输出信号的大直流偏移,采用外接0.1μf串联耦合电容的直流恢复电路。这将使ccd信号的直流电平恢复到大约1.5v。ADC满标度范围为2V的信号。与1V满标度系统相比,等效增益范围为0dB至36dB。

vga增益曲线遵循线性in-db特性。可使用以下公式计算任何增益寄存器值的精确VGA增益

增益(分贝)=(0.0358×编码)+5.5分贝,其中编码范围为0至1023。

相关双采样器

cds电路对每个ccd像素进行两次采样,提取视频信息,抑制低频噪声。图20所示的定时说明了如何使用两个内部生成的cds时钟shp和shd分别对ccd信号的基准电平和数据电平进行采样。SHP和SHD采样边的位置由位于地址0x37的SHPLOC和SHDLOC寄存器的设置确定。这些时钟信号的放置是获得最佳ccd性能的关键。

cds增益可以设置为−3db、0db(默认)、+3db或+6db

在cdsgain寄存器中,地址0x04。+3分贝和+6分贝的设置提高了噪声性能,但减少了输入范围。

可变增益放大器

VGA级提供6分贝至42分贝的增益,可通过串行数字接口以10位分辨率编程。需要最小6分贝的增益来匹配1伏的输入。

模数转换器

AD9923A采用高速低功耗优化的高性能ADC架构。差分非线性(dnl)性能通常优于1lsb。ADC使用2 V输入范围。典型线性和噪声性能曲线见图6和图8。

光学黑夹

光学黑钳位环路消除了信号链中的残余偏移,并跟踪ccd黑电平的低频变化。在每条线上的光学黑(屏蔽)像素间隔期间,adc输出与用户在clamplevel寄存器中选择的固定黑电平基准进行比较。该值可以在0 lsb和255 lsb之间编程,共1023步。产生的误差信号经过滤波以降低噪声,并且校正值通过dac应用于adc输入。通常情况下,每一条水平线都会打开一次光学黑夹环路,但此环路可以更新得更慢,以适应特定的应用。如果在后处理期间使用外部数字钳位,则可以使用可编程寄存器(地址0x00,位D2)禁用AD9923A光学黑钳位。即使环路被禁用,钳位寄存器仍然可以用来提供可编程的偏移调整。clpob脉冲应放置在ccd光学黑像素期间。建议clpob脉冲持续时间至少为20像素宽,以最小化箝位噪声。可以使用较短的脉冲宽度,但钳位噪声可能会增加,从而降低跟踪黑电平中低频变化的能力。有关计时示例,请参见水平夹紧和下料部分。

数字数据输出

数字输出数据使用双相寄存器值锁存,如图73所示。输出数据定时如图21和图22所示。也可以使输出锁存透明,以便adc的数据输出立即有效。对doutlatch寄存器进行编程,位d1到1将输出锁存设置为透明。也可以通过将双禁用寄存器0x01的位d0设置为1来禁用数据输出(三个状态)。

dclk输出可用于数据输出的外部锁存。默认情况下,dclk输出跟踪双相寄存器的值。通过改变dclkmode寄存器,dclk输出可以保持在固定相位,而双相寄存器值被忽略。

为了优化dclk上升沿和数据输出转换之间的延迟,使用了双延迟寄存器。默认情况下,从dclk的上升沿到数据输出的转换大约有8ns的延迟。有关更多信息,请参阅高速正时生成部分。

切换数据输出可以将噪声耦合到模拟信号路径中。若要最小化开关噪声,请将双相寄存器设置为与SHP采样位置相同的边,或在SHP采样位置之后最多设置11条边。其他设置可以产生良好的效果,但需要实验。建议不要在SHD采样位置和SHD位置后的11条边之间出现双相位置。例如,如果shdloc=0,则将doutphase设置为12或更大的边位置。如果数据输出不需要可调相位,则可以使用寄存器0x01,位d1使输出锁存保持透明。

数据输出编码通常是直接二进制编码,但可以通过将灰度寄存器0x01、位d2设置为1而更改为灰度编码。

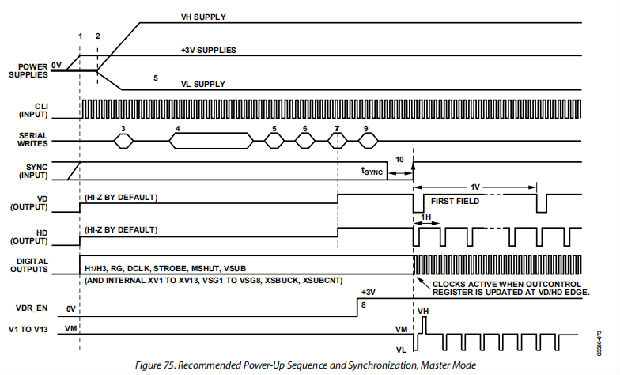

主模式的建议通电顺序

当AD9923A通电时,建议按以下顺序操作(见图75):

1、打开AD9923A的+3 V电源,并启动主时钟(CLI)。

2、打开V驱动电源(VH和VL)。vh和vl的开启顺序没有限制。

3、通过将1写入sw-rst寄存器(地址0x10)来重置内部AD9923A寄存器。

4、加载所需寄存器以配置所需的vpat组、v序列、场定时信息、高速定时、水平定时和快门定时信息。

5、要将部件置于正常电源操作,请将0x04写入AFE备用寄存器(位[1:0],地址0x00),将0x60写入TEST3寄存器0xEA。如果CLO输出用于驱动晶体,也可以通过将1写入寄存器0x16来通电CLO振荡器。

6、默认情况下,内部计时核心保持在重置状态,tgcore_rstb register=0。将1写入tgcore_rstb寄存器(地址0x15)以启动内部计时核心操作。如果2×时钟用于cli输入,则在重置计时核心之前,将clidivide寄存器(地址0x30)设置为1。启动主时钟(cli)后至少等待500μs,然后重置计时核心是很重要的,特别是在使用晶体或晶体振荡器的情况下。

7、通过将1写入主寄存器(地址0x20),为主模式计时配置AD9923A。

8、将VDR_en信号调高至+3 V,以启用V驱动器输出。如果vdr_en=0 V,则所有V驱动程序输出=vm,subck=vll。

9、将1写入outcontrol寄存器(地址0x11)。这允许输出在下一个同步上升沿之后变为活动状态。

10、生成同步事件。如果通电时同步高,则将同步输入调低至少100 ns。然后,把同步调高。这将导致内部计数器重置并启动VD/HD操作。第一个VD/HD边缘允许进行VD寄存器更新,包括VH电源OutControl以启用所有输出。如果外部同步脉冲不可用,则通过写入syncpol寄存器来生成内部同步脉冲,如生成无外部同步信号的软件同步部分所述。