W5500点击型号即可查看芯片规格书

W5500

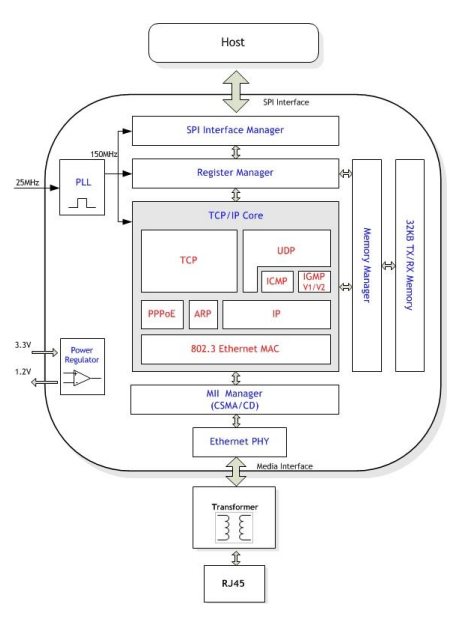

W5500芯片是一个硬连线TCP/IP嵌入式以太网控制器,提供更容易连接到嵌入式系统。W5500允许用户拥有在他们的应用程序中通过使用TCP/IP栈,10/100以太网MAC和PHY嵌入式。

Wiznet的硬连线TCP/IP是一种经市场验证的技术,支持TCP、UDP和IPv4、ICMP、ARP、IGMP和PPPoE协议。W5500嵌入32kbyte内部用于以太网数据包处理的内存缓冲区。如果你使用W5500,你可以只需添加简单的socket程序即可实现以太网应用程序。它的比使用其他嵌入式以太网解决方案更快、更简单。用户可同时使用8个独立的硬件插座。提供SPI(串行外围接口)以便于与外部集成。

单片机。W5500的SPI支持80 MHz的速度和新的高效SPI协议高速网络通信。为了降低系统,W5500提供WOL(唤醒局域网)和断电模式。

特征

-支持硬连线TCP/IP协议:TCP、UDP、ICMP、IPv4、ARP、IGMP、PPPoE

-同时支持8个独立插座

-支持断电模式

-支持通过udp唤醒局域网

-支持高速串行外围接口(SPI模式0,3)

-内部32kbytes内存,用于发送/接收缓冲区

-嵌入10BaseT/100BaseTX以太网物理层

-支持自动协商(全双工和半双工,基于10和100)

-不支持IP碎片

-3.3V操作,5 V I/O信号公差

-LED输出(全/半双工、链路、速度、激活)-48针LQFP无铅封装(7x7mm,0.5mm间距)

目标应用程序

W5500适用于以下嵌入式应用:

-家庭网络设备:机顶盒、PVR、数字媒体适配器

-串行到以太网:访问控制、LED显示屏、无线AP继电器等。

-与以太网并行:POS/微型打印机、复印机

-USB到以太网:存储设备、网络打印机

-从GPIO到以太网:家庭网络传感器

-安全系统:DVR、网络摄像机、信息亭

-工厂和建筑自动化

-医疗监护设备

-嵌入式服务器

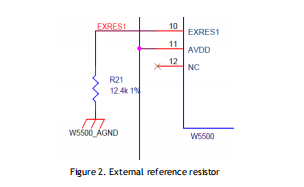

12.4kΩ(1%)电阻器应连接在Exres1引脚和模拟接地(Agnd)之间如下所示。

图2.外部参考电阻

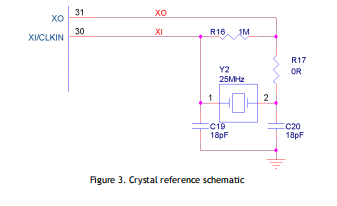

晶体参考示意图如下所示。

主机接口

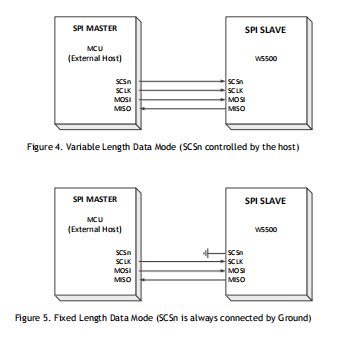

W5500为SPI(串行外围接口)总线接口提供4个信号(SCSN,sclk,mosi,miso)用于外部主机接口,并作为spi从机运行。W5500SPI可以连接到MCU,如图4和图5所示根据其运行模式(变长数据/定长数据模式)这将在第2.3章和第2.4章中解释。

在图4中,spi总线可以与其他spi设备共享。因为SPI总线是专用于W5500的SPI总线不能与其他SPI设备共享。

在可变长度数据模式下(如图4所示),可以共享与其他spi设备连接的spi总线。但是,在固定长度数据模式下(如图5),SPI总线专用于W5500,不能与其他设备共享。

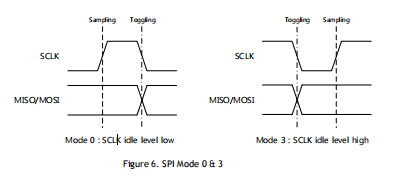

spi协议为其操作定义了四种模式(模式0、1、2、3)。

根据SCLK极性和相位的不同而不同。SPI之间的唯一区别模式0和spi模式3是处于非活动状态的sclk信号的极性。

在SPI模式0和3下,数据始终锁定在SCLK的上升沿上,并且总是在SCLK的下降沿上输出。

W5500支持SPI模式0和模式3。mosi和miso信号都使用从最高有效位(msb)到最低有效位(lsb)的传输序列mosi信号发射和miso信号接收。mosi和miso信号总是传输或按顺序从最高有效位(msb)接收到最低有效位(LSB)。

SPI操作模式

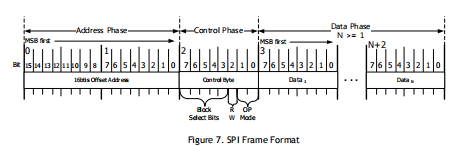

W5500由SPI框架控制(参见第2.2章SPI框架),SPI框架与外部主机通信。W5500 SPI帧包含3个相位,地址阶段,控制阶段和数据阶段。

地址阶段指定W5500寄存器或TX/RX存储器的16位偏移地址。

控制阶段指定偏移(由地址阶段设置)所属的块,以及指定读/写访问模式和SPI操作模式(可变长度数据/固定长度数据模式)。

数据阶段指定随机长度(n字节,1≤n)数据或1字节,2字节和4字节数据。

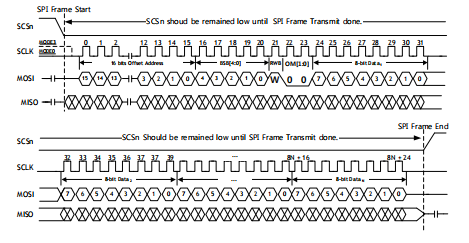

如果SPI操作模式设置为可变长度数据模式(VDM),则SPI总线信号SCSN必须由具有SPI帧步进的外部主机控制。

在可变长度数据模式下,SCSN控制启动(assert(high to low))通知spi帧开始(地址阶段)的w5500和scsn控制端(去断言(低到高))通知w5500 spi帧结束(随机n字节的数据阶段结束)。

W5500 SPI帧由地址阶段的16位偏移地址组成,8位控制阶段和n字节数据阶段如图7所示。

8位控制相位用块选择位(bsb[4:0])进行重新配置,读/写访问模式位(rwb)和spi操作模式(om[1:0])。

块选择位选择偏移地址所属的块。

W5500支持顺序数据读/写。它处理来自数据库的数据(为2/4/n字节顺序数据处理设置的偏移地址)和按地址阶段增加偏移地址(自动增量寻址)的下一个数据此地址阶段指定W5500寄存器和TX/RX缓冲块。

16位偏移地址值按顺序从msb传输到lsb。具有2/4/n字节数据相位的spi帧支持顺序数据读/写,其中偏移地址每1字节数据自动增加数据阶段通过spi操作模式位om[1:0]设置控制相位,数据相位由两种长度类型设置,一种是n字节长度(VDM模式)和其他类型是1/2/4字节(FDM模式)。

此时,1字节数据通过mosi或miso信号从msb传输到可变长度数据模式(VDM)在VDM模式下,SPI帧数据相位长度由外部主机。这意味着数据相位长度可以有随机值(从1字节到n字节的任何长度)根据scsn控制。在VDM模式下,控制阶段的OM[1:0]应为“00”值。

图8显示了外部主机访问W5500进行写入时的SPI帧。在VDM模式下,在SPI帧控制中,RWB信号为“1”(写入),OM[1:0]为“00”相位。此时外部主机断言(从高到低)scsn信号然后主机通过mosi信号将spi帧的所有位发送到w5500。所有位与SCLK的下降沿同步。完成spi帧传输后,主机解除对scsn信号(从低到高)的断言。当SCSN低且数据相位继续时,顺序数据写入可以得到支持。

在VDM模式下,在SPI帧控制中,RWB信号为“0”(写入),OM[1:0]为“00”相位。

此时,外部主机在发送前断言(从高到低)scsn信号

然后主机通过mosi将地址和控制相位的所有位发送到w5500信号。所有位都与SCLK的下降沿同步。

然后主机接收数据相位的所有位,并同步通过miso信号采样sclk。在完成数据相位接收之后,主机解除对scsn信号(从低到高)的asserts。当scsn低并且数据相位继续接收时,序列数据可支持读取。

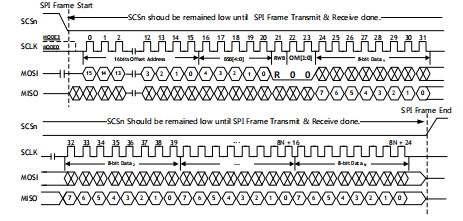

定长数据模式(FDM)

当外部主机无法控制SCSN信号时,可以使用FDM模式。SCSN信号应连接到低电平(始终连接到GND),而不是可以与其他spi设备共享spi总线。在vdm模式下,数据相位长度由scsn控制。但在FDM模式下,数据相位长度由OM[1:0]值('01'/'10'/'11')控制。

这是控制阶段的spi操作模式位。