W181点击型号即可查看芯片规格书

1000点击型号即可查看芯片规格书

特征

·Cypress Premis8482;系列产品

·在输出端生成一个EMI优化的时钟信号

·可选输入输出频率

·单1.25%或3.75%向下或中心排列输出

峰值降低EMI溶液

·集成回路滤波器组件

·使用3.3V或5V电源工作

·低功耗CMOS设计

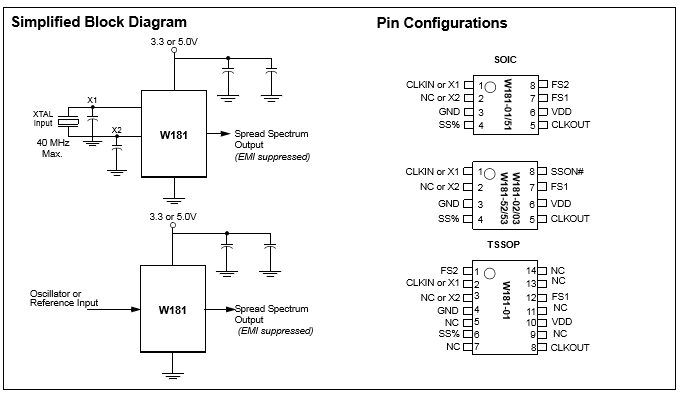

·提供8针小外形集成电路

(SOIC)或14针薄收缩小外形封装(TSSOP仅选择选项)

概述

W181产品是柏树预混料系列中的一系列设备。premis系列融合了pll扩频合成器技术的最新进展。利用低频载波对输出进行调频,大大降低了峰值电磁干扰。使用这种技术,系统可以通过越来越困难的电磁干扰测试,而无需借助昂贵的屏蔽或重新设计。

在一个系统中,不仅在不同的时钟线中减少了电磁干扰,而且在所有与时钟同步的信号中也减少了电磁干扰。因此,使用该技术的好处随着系统中地址和数据行的数量而增加。

功能描述

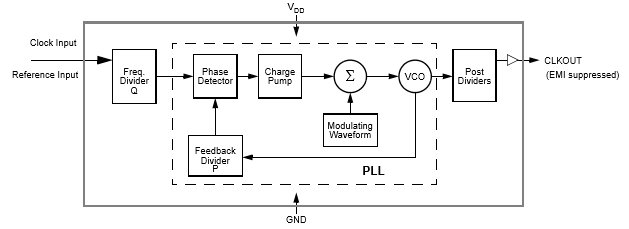

W181使用锁相环(PLL)对输入时钟进行频率调制。其结果是一个输出时钟,其频率缓慢地扫过输入信号附近的窄带。基本电路拓扑如图1所示。输入参考信号除以Q,然后送入相位检测器。来自VCO的信号除以P,再反馈给相位检测器。锁相环将强制VCO输出信号的频率改变,直到分相输出信号和分相参考信号在鉴相器输入处匹配。输出频率等于p/q乘以参考频率的比值。(注:对于W181,输出频率等于输入频率。)扩频频率定时发生器的独特特点是调制波形叠加在VCO的输入端。这会导致VCO输出缓慢地扫过预定的频段。

由于调制频率通常比基本时钟慢1000倍,扩频过程对系统性能的影响很小。

在扩频定时产生中,EMI的降低取决于调制波形的形状、调制百分比和频率。当使用频率选择位(fs1:2引脚)为给定值固定调制波形的形状和频率时,可以设置频率范围。摊铺百分比设置为1.25%或3.75%(见表1)。

较大的扩展百分比可提高EMI降低。但是,较大的扩展百分比可能超过系统最大频率额定值,或者将平均频率降低到影响性能的程度。由于这些原因,在0.5%和2.5%之间的分摊比例最为常见。

扩频定时产生

该装置产生一个频率调制的时钟,以增加其占用的带宽。通过增加基波及其谐波的带宽,降低了电磁辐射的振幅。

被调制时钟的谐波振幅比未调制信号的振幅低得多。振幅的减小取决于谐波数和频率偏差或扩展。换算公式为:db=6.5+9*log10(p)+9×log10(f)其中p是偏差百分比,f是测量减少量的频率,单位为兆赫。

输出时钟通过波形进行调制。正如布什、费斯勒和哈丁在“为减少辐射发射而产生的扩频时钟”中所讨论的那样,这种波形可以最大限度地降低辐射电磁发射的振幅。柏树确实提供了更多的传播和更大的EMI减少选择。

应用程序信息

推荐的电路配置为了在系统应用中获得最佳性能VDD去耦对减小相位抖动和EMI辐射都很重要。0.1-微F去耦电容器应尽可能靠近VDD引脚,否则增加的跟踪电感将抵消其去耦能力。所示的10-μF去耦电容器应为钽型。为了进一步的EMI保护,可以通过铁氧体珠进行VDD连接推荐的电路板布局显示建议的两层电路板布局。

推荐的电路配置

笔记:

4. 频率偏移(偏移)是相对于理想峰值给出的,该理想峰值与仅针对W180-01、-02和-03产品的向下扩展情况下的输入参考频率相同。

5. 对于w180-51、-52和-53产品,中心排列没有偏移(移位)。

C1=高频电源去耦电容器(推荐0.1-微F)。

c2=公共电源低频去耦电容器(建议使用10-μf钽)。

R1=线路阻抗匹