AD7714点击型号即可查看芯片规格书

140点击型号即可查看芯片规格书

265点击型号即可查看芯片规格书

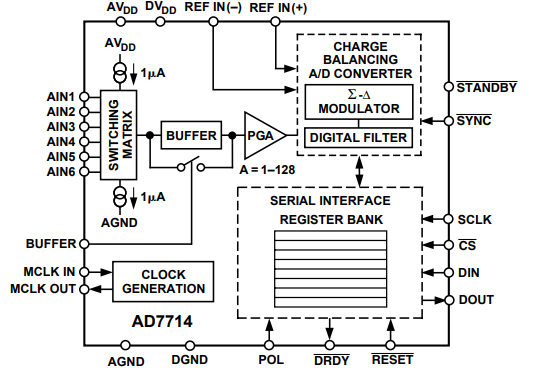

AD7714是一款适用于低频的完整模拟前端测量应用设备。该设备接受低电平信号直接来自换能器并输出一个串行数字字。它采用sigma-delta转换技术实现最多24个没有丢失代码性能的位。应用输入信号以专有的可编程增益前端为基础模拟调制器。调制器输出由片上数字滤波器处理。这个数字滤波器的第一个凹口可以是通过片内控制寄存器编程,允许调整滤波器截止和建立时间。该器件具有三个差分模拟输入(也可以被配置为五个伪差分模拟输入)以及a差分参考输入。它采用单电源供电(+39251;V或+5␣V)。因此,AD7714可执行所有信号调理最多包含五个通道的系统的转换。

AD7714非常适合用于基于智能,微控制器或DSP的系统。它具有可配置的串行接口用于三线操作。增益设置,信号极性和通道可以使用串行端口在软件中配置选择。该AD7714提供自校准,系统校准和后台校准选项,并允许用户读取和写入片内校准寄存器。

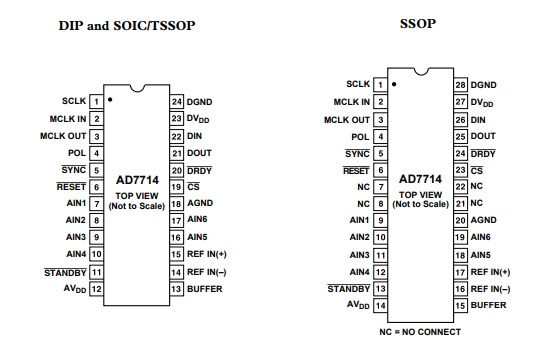

CMOS结构可确保极低的功耗省电模式可将待机功耗降低至15␣μW典型值。该器件采用24引脚,0.3英寸宽的塑料制成双列直插式封装(DIP); 24引脚小外形(SOIC)封装,28引脚收缩小外形封装(SSOP)和a24引脚薄收缩小外形封装(TSSOP)。

产品亮点

1.除了之外,AD7714Y还提供以下功能标准AD7714:更宽的温度范围,施密特触发器在SCLK和DIN上,工作电压低至2.7 V,功耗更低消耗,更好的线性度和24导联的可用性TSSOP包。

2.AD7714的功耗低于500μA(fCLK IN =1␣MHz)或总电源电流为1 mA(fCLK IN =2.5␣MHz)它非常适合用于回路供电系统。

3.可编程增益通道允许AD7714直接从应变计或传感器接受输入信号消除了大量的信号调节。

4.AD7714是微控制器或DSP处理器的理想选择

具有三线串行接口的应用减少了互连线的数量,减少了隔离系统中所需的光耦合器数量。该部分包含片内寄存器,允许控制滤波器截止,输入增益,通道选择,信号极性和校准模式。

5.该部件具有出色的静态性能规格

具有24位无失码,±0.0015%精度和低均方根噪声(140 nV)。通过片上自校准消除了端点误差和温度漂移的影响,它可以消除零电平和满量程的错误。

PIN配置图

AD7714-5输出噪声

表1a列出了AD7714-5的典型陷波和-3␣dB频率的输出均方根噪声和有效分辨率

fCLK␣IN=2.4576␣MHz,而表1b给出fCLK IN =1␣MHz的信息。给出的数字是双极输入范围。VREF为+2.5␣V且BUFFER = 0时这些数字是典型值,在模拟输入电压0␣V时产生。

每个表格中括号内的数字用于表示部件的有效分辨率(四舍五入到最接近的0.5␣LSB)。器件的有效分辨率定义为输出均方根噪声与输入满量程的比值(即2×VREF / GAIN)。当指出的是它不是使用峰峰值输出噪声数计算的。峰峰值噪声数可高达均方根数的6.6倍而基于峰峰值噪声的有效分辨率数字可以比基于均方根噪声的有效分辨率低2.5位在表格中引用。

该部件的输出噪声来自两个来源。第一个是用于半导体器件的电噪声调制器的实现(设备噪声)。其次,当模拟输入信号被转换为数字域时,增加了量化噪声。器件噪声处于较低水平,并且很大程度上与频率无关。量化噪声始于甚至更低的水平但随着频率的增加而迅速上升,成为主要的噪声源。因此,降低过滤器陷波设置(对于fCLK IN =2.4576␣MHz约低于100␣Hz,对于fCLK IN =1␣MHz约低于40␣Hz)倾向于设备噪声占主导地位,而较高的陷波设置主要是量化噪声。改变滤波器陷波和截止量化噪声主导区域中的频率导致噪声性能比其中更显着的改善如表I所示,器件噪声占优势的区域。此外,在PGA之后增加量化噪声,因此有效分辨率在很大程度上与较高滤波器陷波频率的增益无关。同时,在PGA中增加了器件噪声,因此,对于较低陷波频率,有效分辨率会在高增益时降低。此外,在器件噪声主导区域,输出噪声(以μV为单位)在很大程度上与参考电压无关,而在量化噪声主导区域中,噪声与参考值成比例。可以对设备进行后置滤波,以提高给定的输出数据速率-3␣dB频率也可进一步降低输出噪声。

在较低的滤波器陷波设置(fCLK IN =2.4576␣MHz低于60␣Hz,fCLK IN =1␣MHz低于25␣Hz),无失踪代码的性能是24位。在较高的设置下,在1␣kHz陷波设置之前将丢失更多代码对于fCLK␣IN=2.4576␣MHz(对于fCLK IN =1␣MHz为400␣Hz),没有丢失码性能仅保证为12位电平。

AD7714-3输出噪声

表IIa显示了AD7714-3的一些典型陷波和-3␣dB频率的输出均方根噪声和有效分辨率

fCLK␣IN=2.4576␣MHz,而表IIb给出fCLK IN =1␣MHz的信息。给出的数字是双极输入

VREF为+1.25␣V且BUFFER = 0的范围。这些数字是典型值,是在0␣V的模拟输入电压下产生的。

每个表格中括号内的数字代表零件的有效分辨率(四舍五入到最接近的0.5␣LSB)。有效

器件的分辨率定义为输出均方根噪声与输入满量程的比率(即2×VREF / GAIN)。它应该是注意到它不是使用峰峰值输出噪声数来计算的。峰峰值噪声数可高达均方根的6.6倍

数字,而基于峰峰值噪声的有效分辨率数字可以比基于均方根的有效分辨率低2.5位表中引用的噪音。

该部件的输出噪声来自两个来源。第一个是用于半导体器件的电噪声调制器的实现(设备噪声)。其次,当模拟输入信号被转换为数字域时,增加了量化噪声。器件噪声处于较低水平,并且很大程度上与频率无关。量化噪声始于甚至更低的水平但随着频率的增加而迅速上升,成为主要的噪声源。因此,降低过滤器陷波设置(对于fCLK IN =2.4576␣MHz约低于100␣Hz,对于fCLK IN =1␣MHz约低于40␣Hz)倾向于设备噪声占主导地位,而较高的陷波设置主要是量化噪声。改变滤波器陷波和截止量化噪声主导区域中的频率导致噪声性能比其中更显着的改善器件噪声主导区域如表II所示。此外,在PGA之后添加量化噪声,因此有效分辨率在很大程度上与较高滤波器陷波频率的增益无关。同时,在PGA中增加了器件噪声,因此,对于较低的陷波频率,有效分辨率会在高增益下受到一点影响。此外,在器件噪声主导区域,输出噪声(以μV为单位)在很大程度上与参考电压无关,而在量化噪声主导区域,噪声为与参考值成比例。可以对设备进行后置滤波,以提高给定的输出数据速率-3␣dB频率也可进一步降低输出噪声。在较低的滤波器陷波设置(fCLK IN =2.4576␣MHz低于60␣Hz,fCLK IN =1␣MHz低于25␣Hz),无失踪代码的性能是24位。在较高的设置下,在1␣kHz陷波设置之前将丢失更多代码对于fCLK␣IN=2.4576␣MHz(对于fCLK IN =1␣MHz为400␣Hz),没有丢失码性能仅保证为12位电平。

缓冲模式噪音

表III列出了AD7714的典型输出均方根噪声和一些典型陷波和-3␣dB频率的有效分辨率 -

5,fCLK␣IN=2.4576␣MHz,BUFFER = + 5V。表IV给出了AD7714-3的信息,fCLK IN = 2.4576

MHz和BUFFER = +5␣V。给出的数字是双极性输入范围,由差分模拟输入产生电压为0␣V。对于AD7714-5,VREF电压为+2.5␣V;而对于AD7714,VREF电压为+1.25␣V。每个表中的括号用于有效分辨零件(四舍五入到最接近的0.5 LSB)。有效的解决方案器件定义为输出均方根噪声与输入满量程之比(即2×VREF / GAIN)。应该指出的是,它不是使用峰峰值输出噪声数计算。峰峰值噪声数可高达有效值数的6.6倍基于峰峰值噪声的有效分辨率数字可以比基于引用的均方根噪声的有效分辨率低2.5位在表格中。

片上寄存器

AD7714包含8个片内寄存器,可通过器件的串行端口访问。第一个是通信寄存器,它控制通道选择,决定下一个操作是读操作还是写操作,还决定它注册下一个读或写操作访问。与器件的所有通信都必须从对器件的写操作开始通讯注册。上电或复位后,器件需要写入通信寄存器。写的数据该寄存器确定对器件的下一个操作是读操作还是写操作,并确定哪个寄存器发生此读取或写入操作。因此,对器件上任何其他寄存器的写访问开始于对该器件的写操作通信寄存器后写入所选寄存器。从器件上的任何其他寄存器读取操作(包括

输出数据寄存器)以对通信寄存器的写操作开始,然后从所选的读操作开始寄存器。通信寄存器还控制通道选择,DRDY状态也可通过读取来获得通讯注册。第二个寄存器是模式寄存器,用于确定校准模式和增益设置。第三寄存器标记为滤波器高位寄存器,它确定字长,双极/单极操作并包含高4滤波器选择字的位。第四个寄存器标记为滤波器低位寄存器,包含滤波器选择字的低8位。第五个寄存器是测试寄存器,在测试器件时可以访问。第六个寄存器是数据寄存器访问部件的输出数据。最终寄存器允许访问器件的校准寄存器。零刻度校准寄存器允许访问所选输入通道的零电平校准系数,而满量程校准寄存器允许访问所选输入通道的满量程校准系数。寄存器将在更多内容中讨论以下部分的详细信息。

通讯寄存器(RS2-RS0 = 0,0,0)

通信寄存器是一个8位寄存器,可以从中读取数据或写入数据。与器件的所有通信都必须以对通信寄存器的写操作开始。写入通信寄存器的数据确定下一个操作是读操作还是写操作以及该操作发生在哪个寄存器中。一旦对所选寄存器的后续读或写操作完成后,接口返回到它期望写操作的位置通讯登记册。这是接口的默认状态,在上电或复位后,AD7714在此状态默认状态等待对通信寄存器的写操作。在接口序列丢失的情况下,如果a在DIN高电平下进行足够持续时间(包含至少32个串行时钟周期)的写操作,AD7714返回这个默认状态。表V概述了通信寄存器的位指定。

电路描述

AD7714是一款带有片内数字滤波的sigma-delta A / D转换器,用于测量宽动态范围,频信号,例如称重秤,压力传感器,工业控制或过程控制应用中的信号。它包含一个sigma-delta(或电荷平衡)ADC,a校准微控制器,带有片上静态RAM,一个时钟振荡器,数字滤波器和双向串行通信端口。该器件仅消耗500μA电源电流和待机模式,仅需10μA,使其成为电池供电或回路供电仪器的理想选择。该器件有两个版本,AD7714-5,它是指定用于标称+5␣V模拟电源的操作(AVDD)和AD7714-3,指定用于操作来自标称+3.3␣V模拟电源。两个版本都可以使用+3.3␣V的数字电源(DVDD)电压工作或+5␣V.AD7714Y等级部件采用标称AVDD工作3 V或5 V,可以使用数字电源供电3 V或5 V该器件包含三个可编程增益全差分模拟输入通道,可以重新配置为五个伪差分输入。所有通道的增益范围均为1至128,允许该部分接受其间的单极信号0 mV至+20␣mV和0 V至+2.5␣V。在双极性模式下,该部件处理±20 mV和准双极性的正常双极信号当参考输入电压等于时,信号高达±2.5 V.+2.5␣V。参考电压为+1.25␣V,输入范围在单极模式下,从0 mV到+10 mV到0 V到+1.25␣V,在双极模式下,该器件可处理真正的双极性信号±10 mV和准双极性信号,最高±1.25 V.该部分采用sigma-delta转换技术来实现高达24位无失码性能。 sigma-delta

调制器将采样的输入信号转换为数字脉冲其职责周期包含数字信息的火车。该模拟输入上的可编程增益功能也是结合在这个sigma-delta调制器中,调制器的输入采样频率被修改以得到收益更高。一个sinc3数字低通滤波器处理输出sigma-delta调制器并更新输出寄存器由该滤波器的第一陷波频率确定的速率。该输出数据可以随机地或周期性地从串行端口读取,直到输出寄存器更新速率。该该数字滤波器的第一个陷波,其-3␣dB频率及其输出速率可通过滤波器高电平和滤波器低电平进行编程寄存器。主时钟频率为2.4576 MHz,

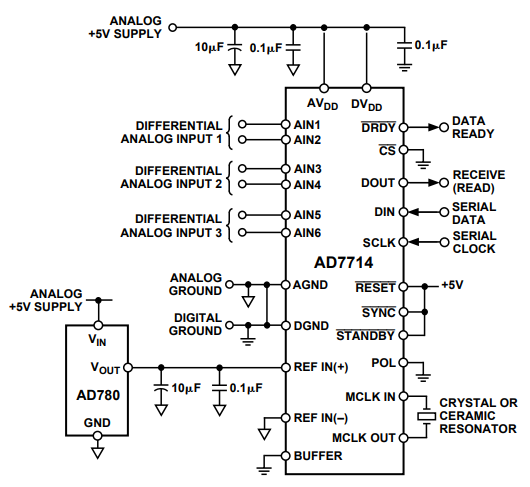

第一个陷波频率和输出的可编程范围速率从4.8␣Hz到1.01 kHz,给出了可编程范围对于-3␣dB频率为1.26 Hz至265␣Hz。该器件的基本连接图如下图所示。这表明AD7714的AVDD和DVDD引脚均为由模拟+3␣V或+5␣V电源驱动。一些应用将使用独立的耗材驱动AVDD和DVDD。在里面如图所示,AD7714的模拟输入为配置为三个全差分输入。该部分已设置

对于这些模拟输入的无缓冲模式。一个AD780,精度+2.5 V参考,提供参考源部分。在数字方面,该部件配置为三线CS连接到DGND的操作。石英晶体或陶瓷谐振器为器件提供主时钟源。有可能必须将晶体或谐振器上的电容器连接到确保它不会在其基础的泛音中振荡运行频率。电容器的值将根据制造商的规格而变化。

模拟输入

模拟输入范围

AD7714包含六个模拟输入引脚(标记为AIN1至AIN6)可配置为三个全差分输入通道或五个伪差分输入通道。位通信寄存器的CH0,CH1和CH2配置模拟输入排列和通道选择如下先前在表VII中概述。输入对(差分或伪差分)提供可编程增益输入可以处理单极或双极输入的通道信号。应该注意,双极性输入信号是参考输入对的相应AIN( - )输入。在无缓冲模式下,这些输入的共模范围是从AGND到AVDD提供了模拟的绝对值输入电压介于AGND␣-␣30␣mV和AVDD +30␣mV之间。这意味着在无缓冲模式下,该部件可以处理两者

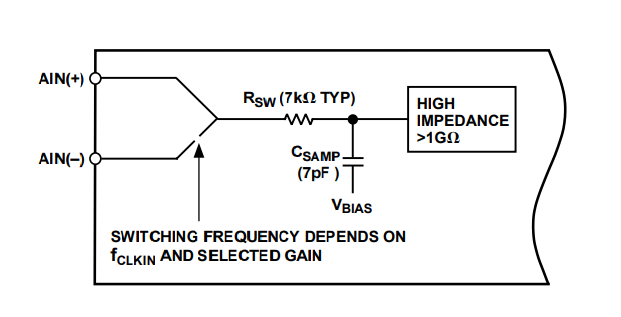

所有增益的单极和双极输入范围。在缓冲模式,模拟输入可以处理更大的源阻抗,但绝对输入电压范围限制在AGND␣+50␣mV到AVDD - 1.5␣V之间,这也是模范围的限制。这意味着缓冲模式对允许增益有一些限制用于双极输入范围。设置时必须小心共模电压和输入电压范围使不超过上限,否则线性性能会下降。在无缓冲模式下,模拟输入直接进入

7␣pF输入采样电容,CSAMP。直流输入泄漏此无缓冲模式下的电流最大为1␣nA。结果是,模拟输入参见动态负载,该动态负载在输入采样率(见图3)。此采样率取决于主时钟频率和所选增益。 CSAMP被指控AIN(+)并在每个输入采样周期放电到AIN( - )。开关的有效导通电阻RSW通常为7␣kΩ。

无缓冲模拟输入结构图