135点击型号即可查看芯片规格书

8226点击型号即可查看芯片规格书

560点击型号即可查看芯片规格书

640点击型号即可查看芯片规格书

ADC0805器件是CMOS 8位连续接口逻辑 - 使用差分的访问时间135 ns近似转换器(ADC)作为独立设备这些转换器旨在允许操作具有三态输出锁存器的总线直接驱动8226;逻辑输入和输满足MOS和数据总线。这些ADC看起来像存储器位置TTL电压电平规范或微处理器的I / O端口,没有接口单5V电源零输入电压值。另外,电压任何较小的模拟电压都可以达到全0位•0.3英寸标准宽度20引脚DIP封装分辨率。

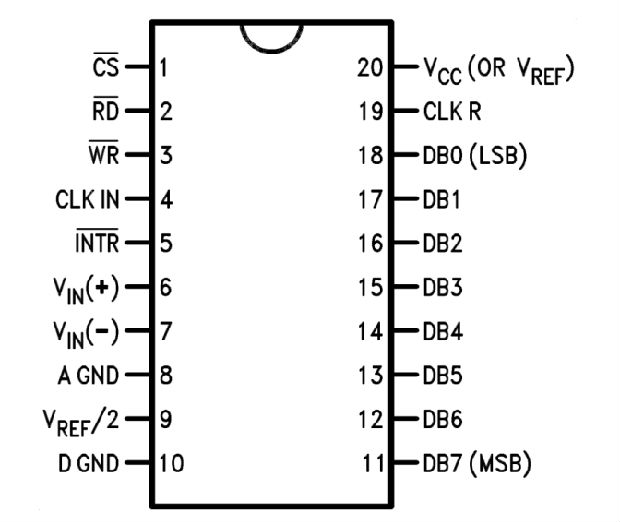

引脚配置和功能图

特点

易于连接所有微处理器,或操作电位梯 - 类似于256R产品。

带有NSC800和INS8080A微分控制的差分模拟电压输入

需要2.5 V(LM336)电压参考逻辑。

片上时钟发生器差分模拟电压输入允许增加

0 V至5 V模拟输入电压范围具有共模抑制和偏移模拟

无零点调整可以调整所需的参考输入以允许编码

20针模塑芯片载体或小外形封装器件信息(1)

采用比例式或5 VDC,2.5 VDC,零件号包装体尺寸(NOM)

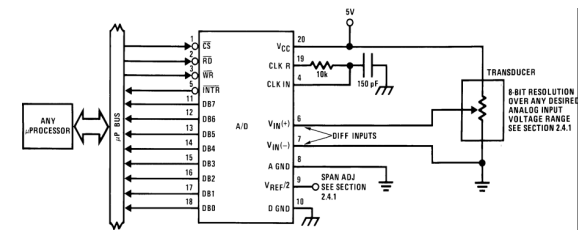

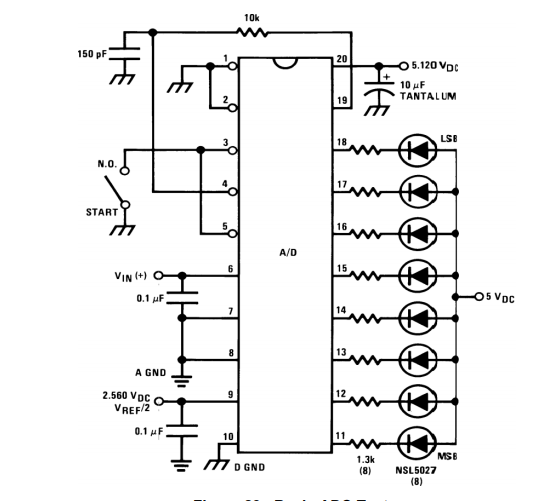

典型应用原理图

ADC0801具有±¼LSB精度图

详细说明

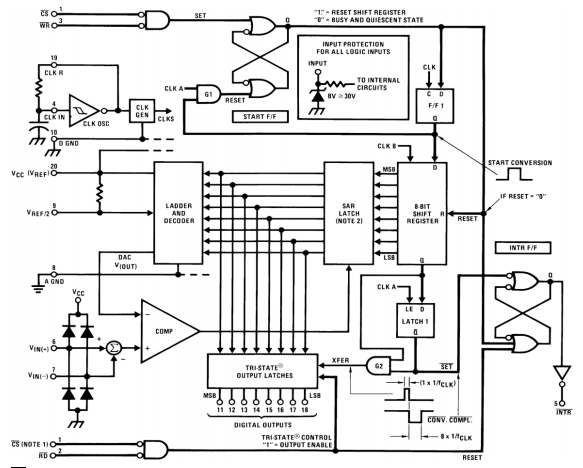

ADC0801系列是通用的8位μP兼容通用ADC转换器,采用单5V工作模式供应。这些设备被视为存储器位置或微处理器系统的I / O端口额外的接口逻辑。输出为三态锁存,便于与微处理器控制接口总线。该转换器采用差分电位梯设计,相当于256R网络的电路。它包含由次逼近逻辑排序的模拟开关。ADC的功能图转换器显示在功能框图中。显示所有封装引脚分布和主要逻辑控制路径以较重的线条绘制。差分模拟电压输入具有良好的共模抑制性能并允许偏移模拟零输入电压值。而且,可以调节输入参考电压允许将小模拟电压范围编码为完整的8位分辨率。确保在所有可能的情况下启动在第一次上电循环期间,需要外部WR脉冲。使用SAR逻辑,首先测试最高有效位,然后在8个比较(64个时钟周期)后测试数字8位二代码(1111 1111 =满量程)被传送到输出锁存器,然后中断被置位(INTR从高到低的转变)。可以通过发出第二个启动命令来中断正在进行的转换。通过将INTR连接到CS输入且CS = 0,可以在自由运行模式下操作该设备。在WR输入从高到低的转换时,内部SAR锁存器和移位寄存器级复位。如只要CS输入和WR输入保持低电平,ADC就会保持复位状态。转换将从1开始在这些输入中的至少一个输入产生从低到高的转变之后的8个时钟周期。通过使CS和WR同时为低来启动转换器。这设置了启动触发器(F / F)和结果“1”电平复位8位移位寄存器,复位中断(INTR)F / F并向D触发器输入“1”,F / F1,位于8位移位寄存器的输入端。然后内部时钟信号将此“1”传送到Q.输出F / F1。与门G1将这个“1”输出与时钟信号组合在一起,为其提供一个复位信号开始F / F.如果设定信号不再存在(WR或CS为“1”),则启动F / F复位,8位移位然后寄存器可以输入“1”,从而启动转换过程。如果设定信号仍然是目前,此复位脉冲无效(启动F / F的两个输出暂时处于“1”电平)并且8位移位寄存器将继续保持在复位模式。因此,该逻辑允许宽CS在这些信号中的至少一个返回高电平和内部时钟之后,WR信号和转换器将启动再次为起始F / F提供复位信号。在“1”通过8位移位寄存器(完成SAR搜索)的时钟后,它显示为输入到D型锁存器,LATCH 1.一旦从移位寄存器输出“1”,AND门G2就会导致新的数字字转移到三态输出锁存器。随后启用LATCH 1时,Q输出进行从高到低的转换,使INTR F / F置位。然后,反相缓冲器提供INTR输入信号。

注意INTR F / F的SET控制在8个外部时钟周期内保持低电平(随着内部时钟运行)在外部时钟频率的1/8处)。如果数据输出持续启用(CS和RD都保持不变低),INTR输出仍然会发出转换结束信号(通过高到低的转换),因为SET输入即使RESET输入始终处于M“1M”电平,也能控制INTR F / F的Q输出操作模式。因此,该INTR输出将在SET信号的持续时间内保持低电平,该信号为8个周期外部时钟频率(假设在此间隔期间ADC未启动)。在自由运或连续转换模式下工作时(INTR引脚连接到WR,CS连接到低电平 - 连续转换),START F / F由INTR信号从高到低的转换设置。这重置了SHIFT REGISTER导致D型锁存器LATCH 1的输入变为低电平。由于锁存器使能输入是仍然存在,Q输出将变高,然后允许INTR F / F复位。这减少了宽度得到的INTR输出脉冲仅为几个传播延迟(约300 ns)。当要读取数据时,CS和RD的组合均为低电平将导致INTR F / F复位将启用三态输出锁存器以提供8位数字输出。

功能框图

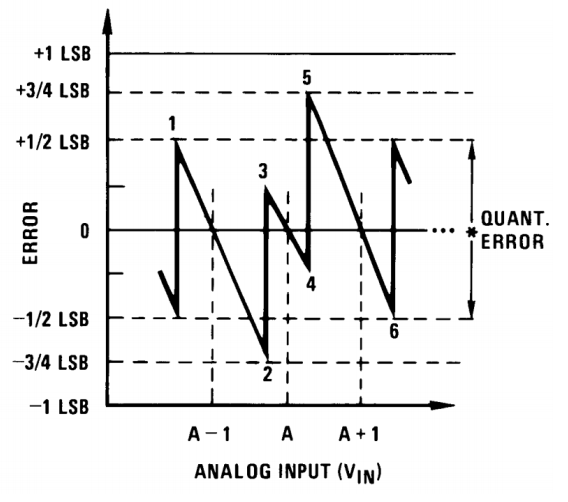

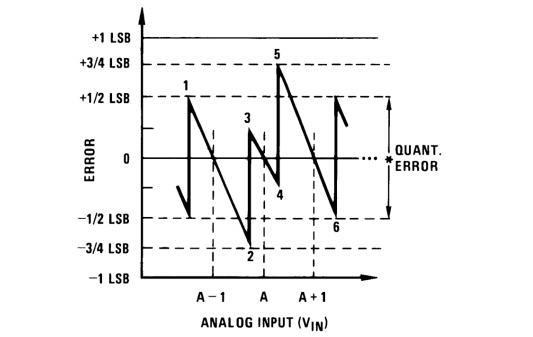

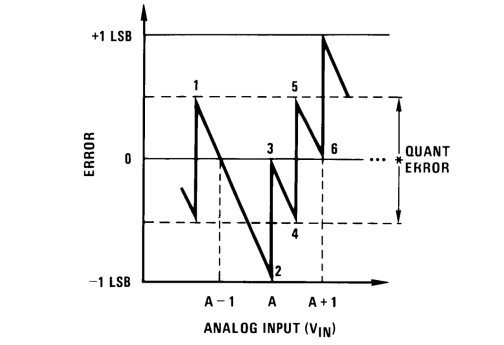

完美的ADC传输特性(阶梯波形)如图16和图17所示。水平标度是模拟输入电压,标记的特定点以1 LSB为步长(19.53 mV,2.5V连接到VREF / 2引脚)。与这些输入对应的数字输出代码显示为D-1,D和D + 1。对于完美的ADC,不仅中心值(A-1,A,A + 1,...)模拟输入产生正确的数字输出代码,但每个立管(相邻输出代码之间的过渡)将位于±1/2 LSB之外每个中心值。如图所示,立管是理想的并且没有宽度。将提供正确的数字输出代码对于一系列模拟输入电压,它们从理想中心值延伸±1/2 LSB。每个胎面(范围)因此,提供相同数字输出代码的模拟输入电压为1 LSB宽。下图1显示了ADC0801的最坏情况误差图。所有中心值输入都保证产生正确的输出代码和相邻的立管被指定为不比±1/4更接近中心值点

LSB。换句话说,如果我们应用等于中心值±1/4 LSB的模拟输入,我们保证ADC将生成正确的数字代码。代码转换位置的最大范围由水平箭头,指定不超过1/2 LSB。下图2的误差曲线显示了ADC0802的最坏情况误差图。如果我们申请,我们保证在这里模拟输入等于LSB模拟电压中心值,ADC将产生正确的数字代码。

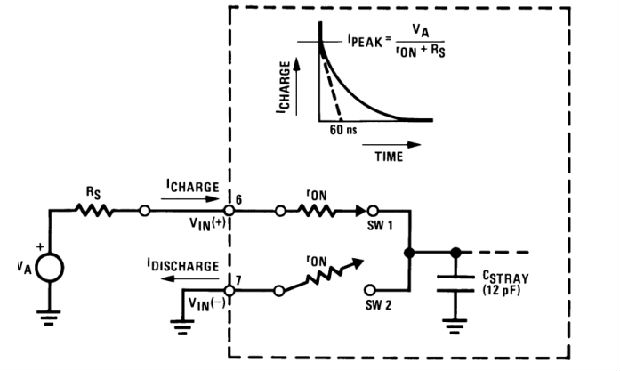

数字控制输入(CS,RD和WR)满足标准TLL逻辑电压电平。这些信号已经存在与标准ADC启动和输出启用标签相比时重命名。另外,这些输入是低电平有效,可轻松连接微处理器控制总线。适用于非微处理器应用中,CS输入(引脚1)可以接地,标准ADC启动功能通过激活获得WR输入(引脚3)施加低脉冲,输出使能功能由低电平有效拉低引起RD输入(引脚2)。由于内部开关动作,位移电流将流向模拟输入。这是由于片上对地的杂散电容如下图所示。

测试ADC转换器有很多复杂程度。最简单的测试之一是将已知的模拟输入电压施加到转换器,并使用LED将显示的结果数字输出代码显示为如下图所示。为便于测试,VREF / 2(引脚9)应提供2.560 VDC和VCC电源电压5.12 VDC应该使用。这提供了20 mV的LSB值。如果要进行全面调整,则应施加5.090 VDC(5.120-1 / / LSB)的模拟输入电压VIN(+)引脚与VIN( - )引脚接地。然后应调整VREF / 2输入电压的值,直到数字输出代码正在从1111 1110变为1111 1111.然后应使用此VREF / 2值对于所有的测试。数字输出LED显示可以通过将8位分成2个十六进制字符来解码,其中4位是最重要的(MS)和4最不重要(LS)。表1显示了这两个4位组的小数二进制等值。通过添加从表1中的“VM”和“VLS”列获得的电压,数字的标称值显示(当VREF / 2 = 2.560V时)可以确定。例如,输出LED显示为1011 0110或B6(以十六进制表示),表中的电压值为3.520 + 0.120或3.640 VDC。这些电压值代表

完美ADC转换器的中心值。量化误差的影响必须考虑在内解释测试结果。

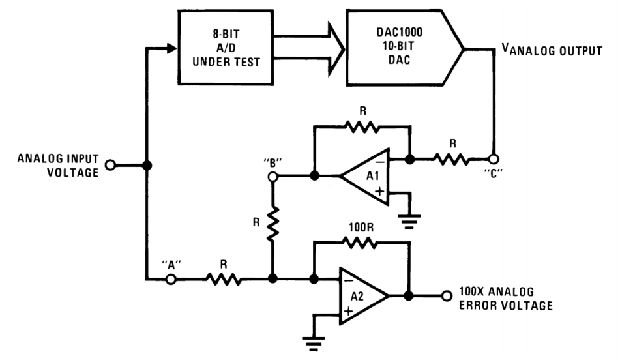

对于更高速度的测试系统或获得绘图数据,测试设置需要数模转换器。精确的10位DAC可作ADC的精密电压源。被测ADC的错误可以表示为模拟电压或2个数字字的差异。误差作为模拟如果具有数字减法功能的实验室DVM可用于读取,则可以消除2个运算放大器差分压,“A-C”,直接。模拟输入电压可由低频斜坡发生器提供并且X-Y绘图仪可用于提供模拟误差(Y轴)与模拟输入(X轴)。对于使用微处理器或基于计算机的测试系统的操作,呈现错误更方便数字。这可以通过下图的电路来完成,其中输出代码转换可以被检测为10位DAC递增。这为8位被测ADC提供了1/4 LSB步长。如果这个测试的结果是自动绘制X轴上的模拟输入和错误(以LSB为单位)作为Y轴,这是一种有用的传输测试结果中ADC的功能。对于验收测试,绘图不是必需的和测试速度可以通过为每个代码的允许错误建立内部限制来增加。

为了讨论与8080A和6800微处理器的接口,使用了一个通用的样本子程序结构。微处理器启动ADC,读取并存储16次连续转换的结果,然后返回用户的程序。 16个数据字节存储在16个连续的存储单元中。所有数据和地址将以十六进制形式给出。软件和硬件详细信息分别针对每种类型提供微处理器。