DAC8830点击型号即可查看芯片规格书

DAC8831点击型号即可查看芯片规格书

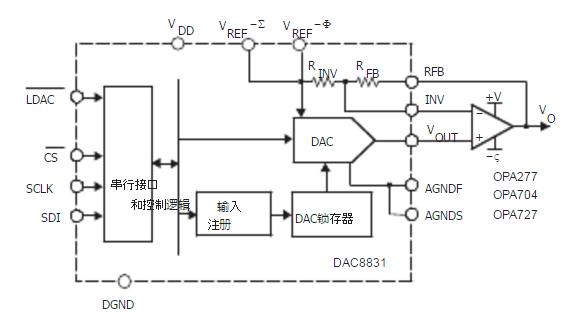

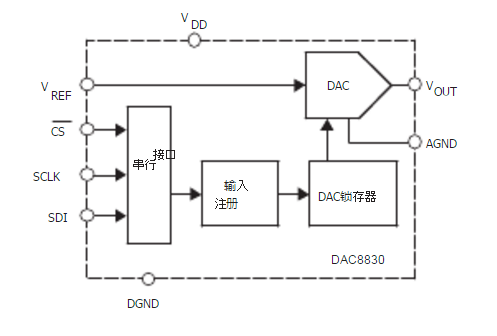

DAC8830与DAC8831是单通道,16位,串行输入,电压输出数字-模拟转换器(DAC),从单一的3V至5V工作电源。这些转换器可提供卓越的线性度(1LSBINL),低干扰,低噪声和快速稳定(1.0μS1/2LSB的满量程输出)过在规定的温度范围为-40°C至+85°C。输出缓冲,从而降低了功率消耗和由缓冲器引入的误差。这些部件配有标准的高速(最高时钟到50兆赫),3V或5VSPI串行接口与DSP或微处理器进行通信。该DAC8830输出为0V至VREF。然而,该DAC8831提供双极性输出(±VREF)时,正在与外部缓冲器。该DAC8830和DAC8831都复位到电源后,零码了。为了获得最佳性能,一组的开尔文连接到外部参考和模拟地设置在DAC8831输入。该DAC8830是采用SO-8封装,该DAC8831采用SO-14封装。两者都有工业标准引脚。该DAC8831同时有采用QFN-14封装。

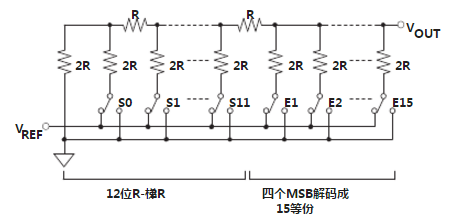

数字到模拟部分的DAC结构为两个设备包含两个匹配的DAC部分和被分段。简化电路图中示出下图。所得的4位的16位数据字的解码用于驱动15个开关,E1至E15。每个交换机连接的15个匹配电阻要么AGND或V1REF。其余12位的数据字驱动器的开关12位电压模式R-2R梯形网络的S0至S11。

输出范围在DAC的输出是VOUT=(VREF×Code)/65536.哪里CODE是载入DAC锁存器中的十进制数据字。

上电复位这两个设备有一个上电复位功能,以确保该输出在上电时被一个已知的状态。在DAC8830与DAC8831,上电时,DAC锁存器和输入寄存器包含全部为0,直到新的数据加载从输入串行移位寄存器。因此,上电后,从该引脚V输出OUT该DAC8830的是0V。从引脚V输出OUT该DAC8831是0V单极性模式和-VREF双极性模式。然而,DAC8830和DAC8831的串行寄存器不清零上电,因此,其内容是未定义。当最初装载到设备的数据,16位或更多位应该被加载,以防止错误的数据出现在输出端。如果加载了超过16位,在过去的16保持;如果小于16装载,位将继续从以前的字。如果必须将设备接口与数据长度小于16位,则数据应可以用0填充的位。

串行接口数字接口与SPI,QSPI?,MICROWIRE?和TIDSP标准的3线连接兼容接口,运行速度可运行在高达50M比特/秒。的数据传输是通过CS框架,芯片选择信号。该DAC工作作为总线从设备。总线主机产生同步时钟SCLK,并启动传输。当CS为高电平时,DAC不被访问,并且在时钟SCLK和串行输入数据SDI是忽略不计。总线主机访问DAC通过驱动引脚CS为低电平。紧跟在从高至低CS的过渡,引脚SDI串行输入数据从总线主站移出同步上落SCLK的边缘,并锁定在SCLK的上升沿输入移位寄存器,MSB优先。低到高的连拍的过渡转移的输入移位寄存器的内容传送到所述输入寄存器。所有数据寄存器是16位。这需要SCLK的16个时钟一个数据字传送到的部分。要完成整个数据字,CS必须去高后16个SCLK时钟输入。如果在CS的低电平状态被应用于超过16个SCLK,最后的16位被传输到输入寄存器在CS的上升沿。但是,如果CS不保持在较低水平在整个16个SCLK周期,数据被破坏。在这种情况下,重新装入DAC,带有一个新的16位字。在DAC8830,输入寄存器的内容被传输到DAC锁存器紧接在输入寄存器被加载,并且在DAC输出同时被更新。该DAC8831有一个LDAC引脚,允许DAC锁存器必须通过将LDAC低异步更新CS后变为高电平。在这种情况下,LDAC必须保持高而CS为低。如果LDAC永久绑低,被装入输入寄存器后DAC锁存器被立即更新(由低到高的跳变引起的CS的)。

DAC8830框图

DAC8831框图