486点击型号即可查看芯片规格书

CY2291是第三代时钟发生器系列。该CY2291向上兼容行业标准ICD2023和ICD2028通过提供继续其传统高水平的可定制功能,以满足不同的时钟同步系统。所有部件都为PC提供了一组高度可配置的关闭功能主板应用。四个可配置时钟中的每一个输出(CLKA-CLKD)可以分配30个频率中的1个任何组合。多个输出配置为相同或相关的[3]频率具有低(<500 ps)偏斜,实际上为重负载信号提供片上缓冲。

CY2291可配置为5 V或3.3 V操作。内部ROM表使用EPROM技术,允许完整定制输出频率。参考振荡器有专为10 MHz至25 MHz晶体而设计额外的灵活性无需外部组件这个水晶。或者,外部参考时钟可以使用1MHz至30MHz之间的频率。顾客使用32 kHz振荡器必须连接一个10MΩ电阻

与32 kHz晶振平行。

特征

三个集成锁相环

EPROM可编程性

工厂可编程(CY2291)或现场可编程(CY2291F)设备选项

低偏移,低抖动,高精度输出

电源管理选项(关机,OE,挂起)

频率选择选项

CPUCLK平滑回转

可配置3.3 V或5 V操作

20引脚SOIC封装

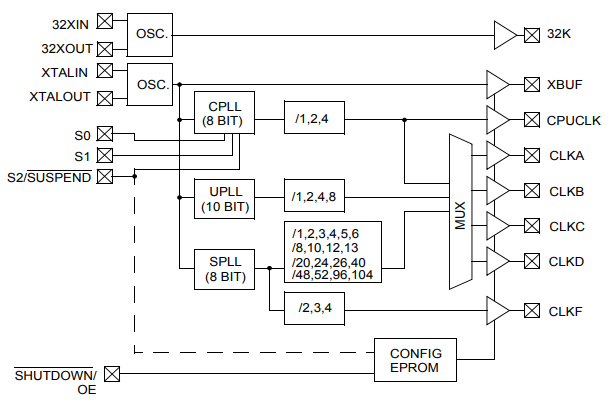

逻辑框图

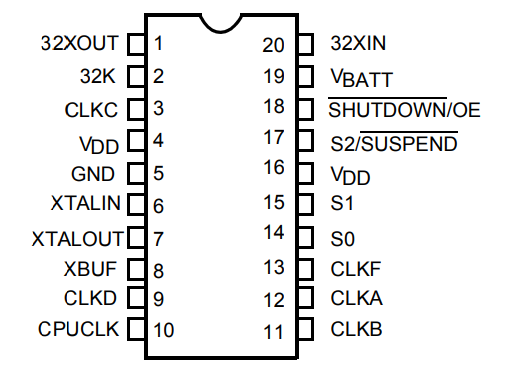

插脚引线图

20引脚SOIC引脚排列

功能概述,输出配置:

CY2291在片上有五个独立的频率源。这些是32kHz振荡器,参考振荡器和三个锁相环(PLL)。每个PLL都有一个特定的功能。系统PLL(SPLL)驱动CLKF输出和在可配置输出上提供固定输出频率。SPLL提供最多输出分频器选项。该CPU PLL(CPLL)由选择输入(S0-S2)控制提供八个用户可选择的频率和平滑的回转频率之间。 Utility PLL(UPLL)提供最多准确的时钟。它通常用于杂项频率由其他频率源提供。所有配置均为EPROM可编程,提供短路样品和生产提前期。

省电功能:

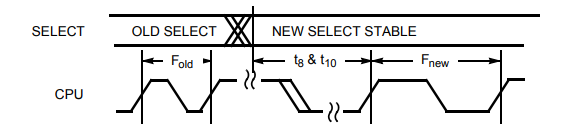

拉出时,SHUTDOWN / OE输入三态输出LOW(32 kHz时钟输出不受影响)。如果系统关断使能,此引脚上的低电平也会关闭PLL,计数器,参考振荡器和所有其他有效的组件。VDD引脚上产生的电流小于50A加15 15A最大值对于32-kHz子系统而言通常是10A。离开关闭模式后,PLL必须重新锁定。除32K外的所有输出都具有弱下拉输出三说时不要漂浮。S2 / SUSPEND输入可配置为关闭a低电平时可定制的输出和/或PLL组。所有PLL除了32K之外的任何输出几乎都可以关闭组合。唯一的限制是,如果PLL被关闭,全部从中得出的输出也必须关闭。暂停PLL关闭所有相关逻辑,同时简单地暂停输出强迫三态条件[3]。CPUCLK可以在8 MHz和8 MHz之间平滑地转换(转换)最大输出频率(5V时为100 MHz / 3.3 V时为80 MHz适用于商业温度部分)。此功能非常有用“绿色”PC和笔记本电脑应用程序,减少了操作频率可以节省相当多的电力。此功能可满足所有486和奔腾®处理器的回转要求。

CyClocks是一个易于使用的应用程序,允许您配置所提供的任何一个EPROM可编程时钟赛普拉斯您可以指定输入频率,PLL和输出频率和不同的功能选项。请注意指定时,此数据表中的输出频率范围在CyClocks中确保您保持在限制范围内。CyClocks还有一个功率计算功能,可以让你看到特定配置的功耗。CyClocks是一个CyberClocks8482;软件中的子应用程序。

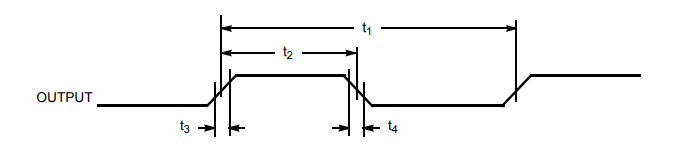

切换波形图

所有输出,占空比和上升/下降时间

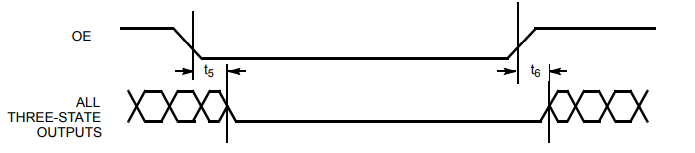

输出三态定时[21]

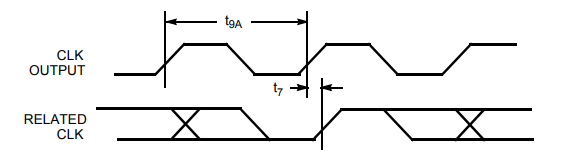

CLK输出抖动和偏移

CPU频率变化