USBN9602点击型号即可查看芯片规格书

一般说明

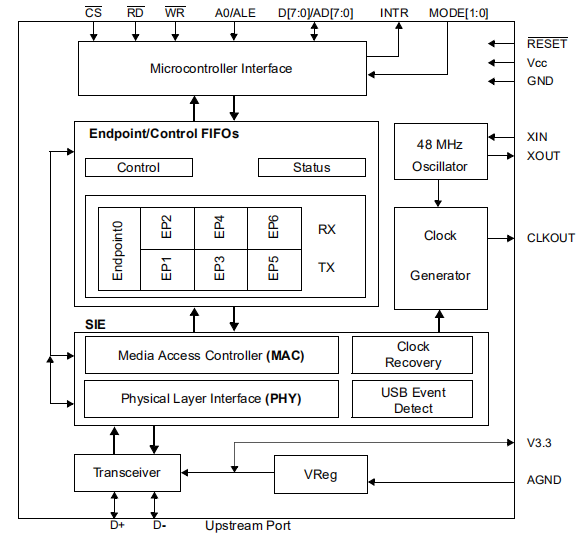

USBN9602是一个集成的USB节点控制器控制端点EP0和六个FIFOS,另外六个是USB规范版本1.0和1.1无法识别的。支持USB中断、批量和集成到单个IC上的是所需的USB传输同步数据传输。具有3.3V调节器、媒体访问控制器、端口多路复用和非多路复用式CPU的8位并行接口接收器USB端点(EP)FIFOS,一种通用的8位并行地址/数据总线。可编程中断输出Face Microwire/Plus接口和时钟生成方案允许设备配置不同的中断托尔。共有七个FIFO缓冲区支持不同的USB信号要求。

一个用于强制配置的双向FIFO

特点

全速USB节点设备USB收发器3.3V信号电压调节器48兆赫振荡器电路可编程时钟发生器由物理层接口(PHY)和媒体访问控制器(MAC)、USB组成的串行接口引擎符合规范1.0控制/状态寄存器文件带七个基于FIFO的端点的USB功能控制器:

–一个双向控制端点0(8字节)

–三个传输端点(2*32和1*64字节)

–三个接收端点(2*32和1*64字节)具有两种可选模式的8位并行接口

–非多路复用

–多路复用(英特尔兼容)支持并行接口的DMAMicrowire/Plus8482;接口28针SO包装

设备概述

USBN9602是一个集成的USB节点控制器。USB标准规定位填充和卸载为数据表第1页的方框图显示了MA-A方法,以确保在线路上充分过渡到设备的芯片组件。接收端时钟恢复正常。无论何时遇到连续1s的收发器串,位填充逻辑在数据流中的每六分之一后面插入0。这个USBN9602包含一个高速收发器,它的位去缓冲逻辑颠倒了这个过程。由三个主要功能块组成:时钟恢复块使用传入的nrzi数据–差分接收器从衍生的输入时钟中提取数据时钟(12兆赫)–单端接收器,具有来自晶体或晶体振荡器(48兆赫频率)的片上电压基准。–带片上电流源的发射机,该时钟用于数据恢复电路。输出该收发器满足的性能要求是该数据块的二进制数据(从NRZI解码在通用串行总线规范流第7章中进行了描述),可以使用验证版本1.0对其进行适当的采样。牵引12兆赫时钟。抖动性能和定时特性满足第章的要求为了最小化信号偏差,差分输出摆动为USB规格的7。发射机平衡良好。回转速率控制是用于驱动程序,以最小化辐射噪声并跨越3.4端点/控制FIFO说话。驱动程序支持Tri-State操作,以允许端点管道控制器(EPC)提供接口收发器的双向半双工操作。用于USB功能端点。终点是最终的差分接收器在完整的数据源或接收器上工作。端点管道为MON模式范围,保证大于USB和内存之间的数据移动,以及单端接收器的COMOF,以避免USB主机和功能之间的路径出现潜在故障。

单端Ze-端点后的串行接口引擎(SIE)。根据USB规格,最多31个活性氧此类端点管道在任何给定时间都有支撑,每个都有相同的功能地址。USBN9602,但是,两个接收器上都有单端接收器,最多支持七个端点管道。数据线。除了差分接收器外,这些都是为了通过开关检测绝对电压。USB功能是一种能够传输数据的USB设备。

阈值介于0.8V和2.0V之间(TTL输入)。在总线上接收外部信息。函数可能具有NAL 1.5±5%千瓦电阻,连接到一个或多个配置之间的电压源,每个配置定义了-3.0V和3.6V参考本地接地,是构成设备的接口。每个接口依次,在D+上表示这是一个高速节点。由一个或多个端点组成。电压调节器(VREG)每个端点都是USB上的可寻址实体,需要响应来自USB的输入和输出令牌。电压调节器从主机(通常是PC)提供3.3V电压。In标记表示主机集成收发器的5.0V设备电源。这已请求从终结点接收信息,V输出可用于向1.5KW供电,输出令牌表示主机即将发送上拉电阻。可以在端点的软件控制信息下禁用它。

允许在3.3V系统中使用该设备。这个输出必须使用10 mF钽电容器去耦,以在检测到指向端点的IN令牌时,地面。端点负责用数据响应小包裹。如果端点当前停止,则停止手-串行接口引擎(SIE)震动包在软件控制下发送。如果结束USB串行接口引擎(SIE)由一个物理点组成,则启用,但不存在任何数据,则为NAK(负自动发送iCal层接口(PHY)级和媒体访问确认)握手包。控制器(Mac)级别。PHY级别包括数字-如果端点是等时且已启用,但没有数据时钟恢复电路,一个数字故障滤波器,存在数据包的结束,数据包结束后的一个比特错误是检测电路,以及位填充和卸载逻辑。在公共汽车上发的。

MAC层包括数据包格式、CRC Genera——同样,在检测到一个发往操作和检查、端点地址检测和pro-an端点,端点负责接收

提供必要的控制,以提供由主机发送的NAK、ACK和数据包,并将其存储在缓冲区中。如果由端点控制确定的暂停响应-端点管道当前暂停,暂停握手指定端点管道的LER。SIE也是响应包,在数据传输结束时发送。如果用于检测和报告端点管道检测事件的Sible当前被禁用,没有握手数据包在数据传输结束时发送USB特定事件,如重置、挂起和重新连接。如果端点苏美。模块至传输管的发送器输出已启用,但不存在要存储的缓冲区。接收端匹配良好(小于1ns),以尽量减少数据上的偏差,即NAK(否定确认)握手USB信号。发送数据包。如果端点是等时且已启用但无法处理数据,数据会丢失。

禁用的终结点不响应In、Out或4.0连接图设置令牌。

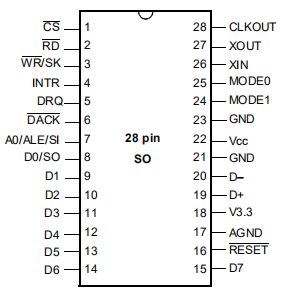

端点管道控制器保持独立状态以及每个端点管道的控制信息。CS 1 28 CLKOUT对于IN令牌,端点管道控制器负责用于将数据从定义的缓冲区传输到主机。路2 27 Xout对于out令牌,端点管道控制器是responsi-wr/sk 3 26 xin用于将数据从主机传输到定义的缓冲区。INTR 4 25模式微控制器接口DRQ 5 24模式1CPU或微控制器可通过8位DACK 6 23 GND连接。

并行接口或微线接口。对于par-a0/ale/si 7 28针22 VCC allel接口,有两种寻址模式(多路或非多路)。这些模式由D0/SO 8 SO 21 GND选择在模式1和d1 9 20 d上硬接线正确的二进制代码-模式0针。D2 10 19天+此外,还提供了中断输出。D3 11 18 v3.3的类型高或低输出激活,或开路漏极低输出中断可编程为推拉激活-D4 12 17 AGND

PIN描述

The following tables briefly describe the USBN9602 pins.关于PIN函数的简介。每个表格列表一组相关设备,并显示不需要输入或双向设备的注释。设备编号,信号方向(“I”用于输入,O“Up or down as appropriate.”这是最重要的减少。For output“I/O”for bidirectional,or n.a.for not applica-overall power consumption and limit emi.电力供应标签功能描述数字电源(VCC)

23 N.A.GND Digital Power Supply(GND)N.A.Agnd Analog Power Supply(Agnd)

N.A.V3.3.收发器3.3V电压供应。本PIN可以用作内部电压调节器输出。所述调节器仅限于内部收发器和一个外部脉冲。年外部1毫米耦合电容器需要在这一点上。电压调节器输出在硬件复位上是无损的。如果内电压调节器是左损坏,则可以使用此松。作为一个3.3V输入收发器。振荡器、时钟和复位标签功能描述N.A.Xin Input for Internal 48 MHz晶体振荡器电路.第三谐波水晶48兆赫可以使用。N.A.XOUT输出用于内部晶体振荡器电路。秒时钟输出本品提供可编程时钟源。上硬件复位资料来源:A 4 MHz Clock(可能是一个初步的不连续阶段)。它可能被编程为通过时钟配置寄存器的不同速度或衰减是同步的,并将平滑地出现。复位激活低复位输入在本销上提供信号调节以允许使用简单电源复位电路

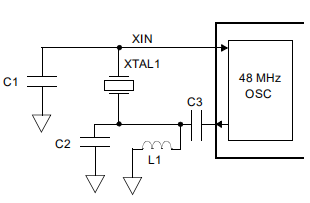

振荡器电路

Xin和Xout插脚可以连接到48MHz闭环晶体振荡器。或者,可以输入一个xin外部48兆赫时钟源来对设备。内部晶体振荡器使用48兆赫第3 xTAL1谐波晶体。显示Crystal选项的电路。如果使用外部时钟源,则将其连接到XIN。Xout未连接。杂散电容和电感应保持在在振荡器电路中是可能的。跟踪长度应为通过定位晶体和外部组件来最小化C2尽可能靠近Xin和Xout销。

注意:所示电路已使用来自仅限ECS公司(例如零件号ECS-480-S-1-3OT)。为了其他晶体,请向制造商咨询推荐的电路和元件值。

三次谐波晶体振荡器连接

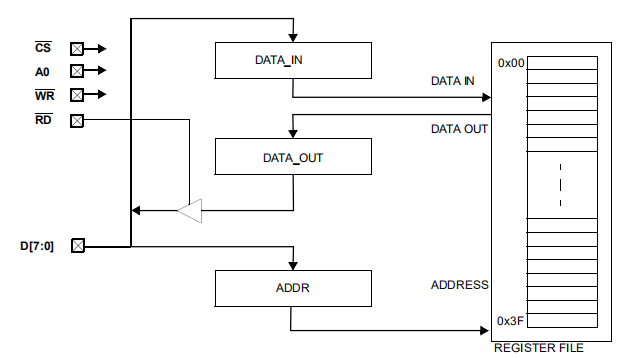

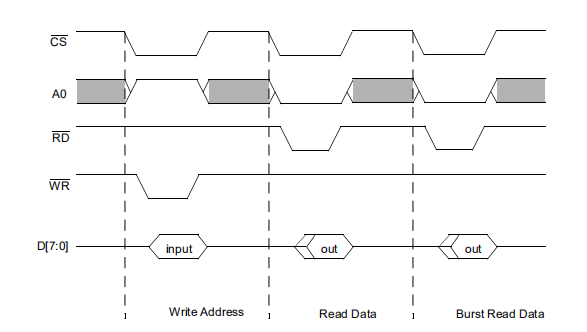

6.0并行接口

并行接口允许USBN9602作为6.1非多路复用模式工作。CPU或微控制器外围设备。两个接口之一,非多路复用模式使用控制针CS,RD,模式可以通过mode0 pin选择,而wr、地址pin a0和双向数据总线mode1引脚被拉低。此模式由Ty选择-–将模式1和模式0引脚连接到GND的非多路复用模式。–多路复用模式CPU直接访问寄存器数据,数据输出和地址读写数据USBN9602可以在标准模式或突发模式下完成有关中信号定时的定时信息非复用模式。

标准访问模式地址非地址寄存器(addr)的标准usbn9602访问序列用作指向inmultiplexed接口模式的指针,即将地址写入内部存储器。此寄存器是只写的,已清除地址寄存器,然后在复位时读取或写入数据。寄存器中的数据输出/数据输出。数据数据输出寄存器发生在地址寄存器。地址寄存器之间的选择数据输出寄存器(数据输出)用数据输出/数据输入寄存器通过地址寄存器指向的a0内存寄存器完成。输入。更新发生在以下条件下:突发模式1。地址寄存器写入后在突发模式下,地址寄存器用2写入一次。从数据寄存器读取后所需片上寄存器的存储器地址。然后是3。写入寄存器中的数据后对该寄存器执行的连续读/写是只读的,并在之后保存未定义的数据。数据输出/数据输入寄存器,无需写入新的AD-重置。穿着。读操作的数据输出寄存器内容-6.1.6数据输入每次读取后更新一次选项。数据输入寄存器(data_in)保存的数据是写入usbn9602地址地址的用户寄存器指向。下表概述了并行内部-此寄存器仅写,重置时清除。非多路模式的面寄存器。在桌子上,保留位在读取时返回未定义的数据,应为6.2多路复用模式。写零。多路复用模式使用控制针cs、rd、wr,地址锁存启用信号ALE和双向

访问寄存器位号地址数据总线这个通过将模式1连接到GND和将模式0连接到VCC。读取数据\地址在ALE时锁存到地址寄存器中写入数据输入高,数据输出/输入与下一个激活的RD或WR信号。所有寄存器都可以在中直接访问。读取保留的界面模式。图7显示了基本的计时。

USBN9602支持DMA传输,外部图8显示了基本的DMA读取时间,从端点1到6的DMA控制器。其中显示了基本的DMA写入时间。模式下,除了并行接口插脚rd或wr和数据外,还使用设备插脚drq和dack。DMA模式只能与DRQ一起使用并行接口模式(模式1与GND相连)。阅读或在内部生成写入地址,并且在DMA循环期间,a0/ale引脚被忽略。达克DMA支持逻辑的优先级低于并行接口。在DMA cy-wr期间,CS需要保持非活动状态。CLE如果cs变为活动状态,则忽略dack,并且执行读/写操作。只有一个端点可以当d[7:0]输入时,在给定时间启用以发出DMA请求接收或传输数据。

要启用DMA传输,必须执行以下步骤:DMA写入USBN9602本地CPU对DMA控制器进行编程,以便快速通过需求模式转移。在此模式下,发生传输仅当USBN9602通过DRQ请求时引脚。数据从USBN9602接收/传输FIFO读取/写入/写入,并从本地写入/读取。同一总线事务期间的内存。

DMA地址计数器编程为指向DRQ本地共享内存中的目标内存块,字节计数寄存器用待传输块中的字节数进行编程。达克设置了DMA请求启用位和DMA源位。在USBN9602中。此外,软件必须设置RD各自的端点启用位。

USB主机现在可以执行USB大容量或同步通过USB总线向接收FIFO或D[7:0]输出传输数据来自USBN9602中的传输FIFO。如果达到FIFO的警告限制或传输/接收完成,则会出现DMA请求/确认从USBN9602读取DMA对预定数量开始边缘序列字节数。发出DMA请求的时间取决于所选的DMA模式(由dmacntrl.dmod位)、端点FIFO的当前状态和FIFO警告启用位。可以立即发出DMA请求。

在DMA控制器被授予总线控制权后,它驱动有效的内存地址并断言dack和rd或wr,因此从usbn9602传输一个字节接收FIFO到存储器或从存储器到传输先进先出法。这个过程一直持续到dma字节计数,在DMA控制器内,达到零。

在传输编程的数据量后,固件需要执行以下操作之一(取决于传输方向和模式):将新数据排队通过设置txcx.tx_en位进行传输,设置通过设置txcx.tx_最后一位结束数据包标记,通过设置rxcx.rx en位重新启用接收,或检查是否接收到数据包的最后一个字节通过重置,可以随时停止DMA传输USBN9602 DMA请求启用位。如果USBN9602DMA请求启用位在DMA循环,当前循环在DMA请求被终止。

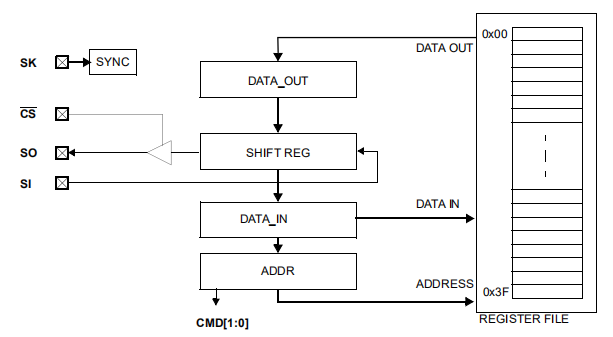

Microwire/Plus接口允许USBN9602 IRE/PLUS模式使用称为芯片选择(CS)的串行管脚。通过时钟(sk)、串行数据输入(si)和串行数据输出(so)作为CPU或微控制器的外围设备工作,如串行接口。通过拉动图的来选择此模式。模式1针脚高,模式0针脚低。微薄的

微线接口由并用cs的上升沿重置。在sk上升沿之后,si上的数据被移入,数据被移出。所以在sk的下降边缘之后。从和到的数据传输移位寄存器在第八个的下降沿之后完成。SK时钟。用最高有效位传输数据第一

注:对任何寄存器的写操作总是读取在写入发生后进行注册,并在下一个周期中移出该数据。这个读不清除各自寄存器中的位,即使在读时清除也是如此。(cor)型钻头。写入TXDX(传输数据)寄存器时出现异常,这会导致在下一个循环中读取未定义的数据。

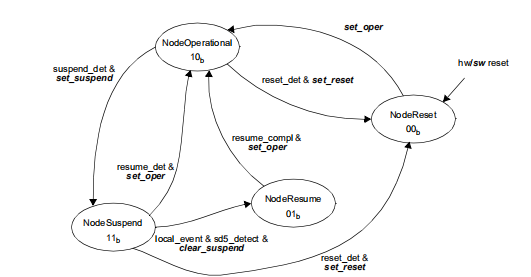

设备功能状态

在任何给定的时间,USBN9602在其中一个USB规范中运行要求设备必须准备就绪。以下状态:唤醒后10 ms内响应USB令牌或“nodereset”设备重置重置。“nodeoperation”(设备运行时的“nodeoperation”)或-9.4功能状态转换Mally设备状态的状态图“nodesuspend”当设备因和转换而暂停时。触发每次转换的条件USB不活动如图所示。需要固件的条件noderesume”当设备从操作中唤醒时,以斜体显示。注意,所有USBN9602挂起状态状态转换由固件启动。挂起、恢复或重置行条件会导致从一个操作状态转换到另一个操作状态。这些情况由专门的硬件检测并报告通过备用事件(Altev)寄存器。如果中断是启用,发生时生成中断任何指定的条件。

暂停运行USB设备应在对暂停事件的响应,该事件在3 ms时发生已经过去,没有任何可检测的总线活动。这个USBN9602查找此事件并通过设置向其发送信号altev.sd3位,导致产生中断。固件应通过将USBN9602处于挂起状态。

在暂停状态下,收发器进入特殊的低功耗模式。所有已注册的状态和FIFO缓冲区保持静态,以便在恢复活动时不需要额外的操作。USBN9602可以从挂起恢复操作在固件控制下作为对本地的响应的状态主机控制器上的事件,它可以依次唤醒通过远程恢复操作的USB总线,或在检测到USB总线上的恢复命令时发出信号主机控制器的中断。

远程恢复如果主机已启用远程唤醒这个节点,USBN9602可以启动远程唤醒。一旦固件检测到应该唤醒总线,它通过使用NFSR寄存器在USB上启动远程恢复,将USBN9602从暂停状态释放。节点固件必须确保USB上至少存在5毫秒的空闲时间。当处于恢复状态时,一个常数“k”被信号打开USB。这应该持续至少1 ms,之后USB主机继续发送恢复信号至少再加20毫秒,然后通过发出结束数据包(EOP)序列来完成恢复操作。要成功检测EOP,固件必须输入通过设置nfsr寄存器的“nodeOperation”状态。如果没有收到来自主机的结束数据包在100毫秒内,应启动远程恢复。再次通过软件。

USB恢复操作当在暂停状态下检测到恢复或重置信号时,USBN9602可以将此信号发送给主系统。通过生成中断来控制。

由固件启动的转换

节点功能状态图以下注释适用于状态图:–当节点不在nodeOperation状态时,所有端口寄存器和内部端点状态都将重置。–在noderesume状态下,恢复信号向上游传播。–在nodesuspend状态下,节点可能进入低功耗状态,能够检测到恢复信号。描述了触发状态转换的各个条件。

终结点操作

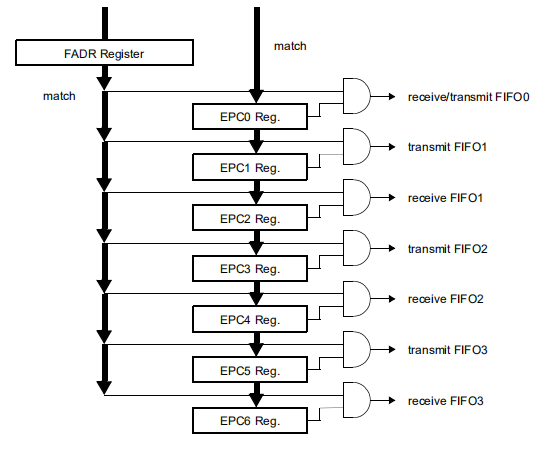

数据包从根集线器广播到所有节点、传入的USB数据包地址字段和端点。在USB网络上。地址检测是在从输入比特流中提取的字段中实现的。然后硬件允许有选择地接收数据包和到地址字段,并与功能地址寄存器进行比较,以达到微控制器带宽的最佳使用。一个ter(fadr),如果检测到匹配,则端点字段将具有七个不同端点组合的函数地址与所有端点控制寄存器进行比较。操作被并行解码。如果找到匹配项,则该匹配项(epcx)是并行的。匹配将导致有效载荷特定数据包被接收到FIFO中;否则,它是使用各自的忽略。终结点FIFO。

终结点0操作

如果对同一方向的两个端点进行编程,请注意,实际的当前操作状态不是直接的具有相同的端点号,并且两个都启用,固件可见。然后,数据将被接收或传输使用结束-写入FIFO的数据包将被传输如果一个在用较小的数字指向,直到接收到该端点的dis-token。如果出现错误能够进行大容量或中断传输,或检测到数据包已满,数据包仍保留在FIFO中。或ISO传输为空。例如,如果使用next-in令牌重试接收EP2和传输。

和接收EP4都使用5号端点,并且可以刷新FIFO内容以允许响应都是等时的,那么第一个输出包是重出令牌,或者为下一个将新数据写入FIFO接收到EP2,第二个输出包接收到令牌。进入EP4,如果两者之间没有固件交互。对于ISO端点,这允许实现一个乒乓球如果接收到一个用于FIFO的out令牌,固件将缓冲方案和帧号匹配日志-只有在集成电路。没有错误条件(crc或stuff错误)。错误的接收被自动丢弃。不同方向的端点用相同的端点号仍然独立运行。10.3发送端点FIFO操作(热膨胀系数1、热膨胀系数2、热膨胀系数3)双向控制端点FIFO0操作端点1、3和5支持的传输FIFOS数据包的批量、中断和同步USB传输FIFO0用于大于FIFO大小的双向控制。因此,firmEndpoint为零。它可以配置为接收发送到软件的数据,必须在USB数据包的同时更新FIFO内容通过设置EPC0 ET的DEF位在总线上传输默认地址传输FIFO的操作不支持等时传输。

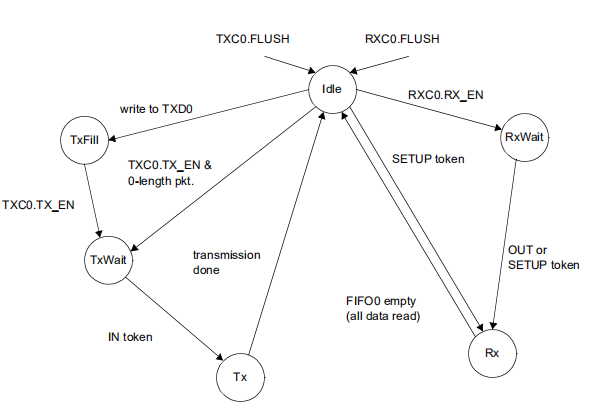

控制终结点。端点0 FIFO可以保持单个接收或发送最多包含8个字节数据的数据包。一个状态显示终结点0的基本操作的图表接收和发送方向均采用FIFO。

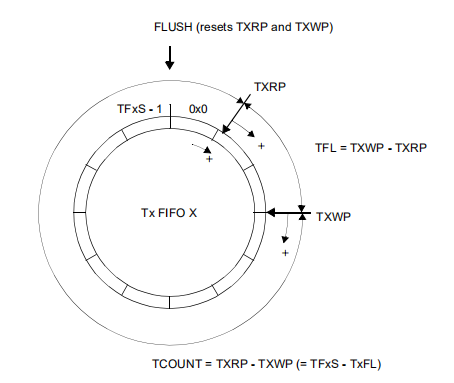

TX FIFO操作中使用的图表标签解释为。低。传输FIFO电平。此值表示字节数未传输的tfx在欠载运行前保留在fifo中。传输FIFO x大小。这是下次读取FIFO时发生的字节总数。在FIFO中可用。如果txfl下降到 TxRP特定值。设置相应的fvev.txwarnx位如果txfl等于或小于传输读取指针。此指针在每个txcx.tfwl中递增。端点控制器从传输读取数据的时间先进先出法。如果tfx为10.3.5 t计数,则此指针将换行为零。达到。TxRP的增量永远不会超过传输FIFO计数的值。这个值表示有多少写入指针txwp。可在传输中填充空字节如果txrp等于txwp和fifo,则会出现欠载情况。固件可通过试图用tx-txsx寄存器传输更多字节。cx.未设置最后一位。10.4接收端点FIFO操作(RXFIFO1,10.3.3热湿性粉剂RxFIFO2、RxFIFO3)传输写入指针。对于支持端点2、4和6的每个接收FIFO,此指针都递增。固件写入发送FIFO的时间。此指针批量、中断和数据包的同步USB传输如果达到tfx,则换行到零。大于FIFO大小。如果数据包长度超过FIFO大小,固件必须读取FIFO如果在接收USB数据包时尝试向FIFO内容写入更多字节,比实际空间可用(FIFO溢出),写入总线忽略FIFO。因此,您应该检查t计数FIFOS。以获得剩余空字节数的指示。

RX FIFO操作

如果RXFL降至A,则可以发出FIFO警告。接收FIFO x大小。这是特定字节值的总数。设置相应的fvev.rxwarnx位在FIFO中可用。如果RXFL等于或小于rxcx.rfwl.文件。RXRP重新计数接收读取指针。此指针每递增一次固件从接收FIFO读取的时间。此接收FIFO计数。这个值表示有多少如果达到RfXs,指针将换行到零。RxRP是可从接收FIFO中读取的字节。永远不要超过RXWP的值。固件可以通过rfsx访问该值。注册。

如果试图读取的字节数超过实际可用的字节数(FIFO欠载),则最后一个字节为read repeti-10.5编程模型主动。因此,您应该检查rcount以获得图19所示的寄存器层次结构。它显示了对剩余接收字节数的重新指示。端点寄存器和事件寄存器之间的关系-Rxwp-ters.接收写入指针。此指针每递增一次端点控制器写入接收FIFO的时间。如果达到Rfx,则此指针将换行到零。如果rxrp等于rxwp且试图接收更多字节。接收FIFO电平。此值表示还有多少在发生溢出情况之前,可以接收字节下一次写入FIFO。