CY2309SXC-1点击型号即可查看芯片规格书

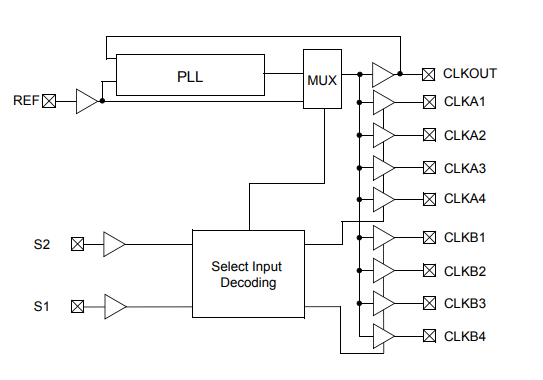

CY2309SXC-1是一款低成本3.3V零延迟缓冲器,设计用于分配高速时钟,采用16引脚SOIC或TSSOP包。CY2305SXC-1是一款8引脚版本CY2309。它接受一个参考输入,并输出五个低电平歪斜的时钟。每个设备的-1H版本最高可运行频率为100- / 133 MHz,驱动器比-1高设备。所有器件都具有锁定输入时钟的片上PLL在REF引脚上。 PLL反馈在片上并获得来自CLKOUT焊盘。CY2309有两组,每组四个输出,可以是由选择输入控制,如果不需要所有输出时钟,BankB可以三态。选择输入也允许输入时钟直接应用于芯片和系统测试的输出目的。

CY2305和CY2309 PLL进入掉电模式时REF输入没有上升沿。在这种状态下,输出是三态的PLL关闭,导致小于25.0?这些部件的电流消耗。 CY2309 PLL如选择输入中所示,在另一个案例中关闭多个CY2305和CY2309器件可以接受相同的输入时钟并分发它。在这种情况下,输出之间的偏差保证两个器件的功率小于700 ps。CY2305 / CY2309有两种或三种不同的产品配置,CY2305-1 / CY2309-1是基础部件。 CY2305-1H /CY2309-1H是-1的高驱动版本,它的上升和下降时间比-1快得多。

特征

10 MHz至100/133 MHz工作范围,与CPU兼容和PCI总线频率

零输入输出传播延迟

60 ps典型的周期间抖动(高驱动)

多个低偏斜输出

85ps典型输出至输出偏斜

一个输入驱动五个输出(CY2305)

一个输入驱动九个输出,分组为4 + 4 + 1(CY2309)

与基于Pentium的系统兼容

测试模式绕过锁相环(PLL)(CY2309)

包装:

8引脚,150 mil SOIC封装(CY2305)

16引脚150 mil SOIC或4.4 mm TSSOP(CY2309)

3.3 V操作

商业和工业温度范围

逻辑框图

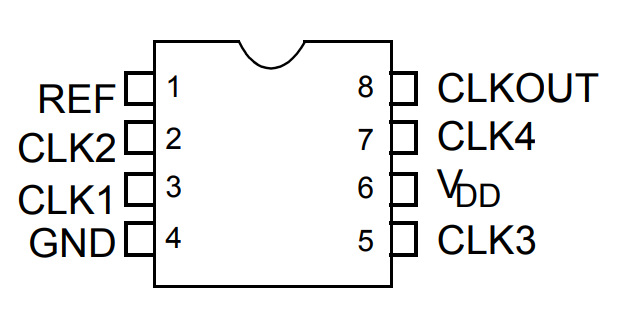

8引脚SOIC引脚排列图

引脚说明

适用于CY2305引脚信号说明

1 REF [1]输入参考频率,5 V容差输入

2 CLK2 [2]缓冲时钟输出

3 CLK1 [2]缓冲时钟输出

4 GND地

5 CLK3 [2]缓冲时钟输出

6 VDD 3.3 V电源

7 CLK4 [2]缓冲时钟输出

8 CLKOUT [2]缓冲时钟输出,该引脚的内部反馈

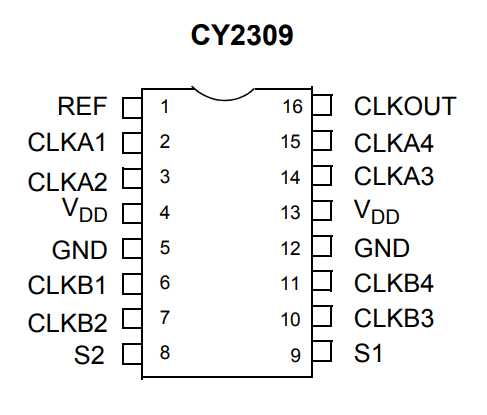

16引脚SOIC / TSSOP引脚排列图

引脚说明

适用于CY2309引脚信号说明

1 REF [3]输入参考频率,5 V容差输入

2 CLKA1 [4]缓冲时钟输出,Bank A.

3 CLKA2 [4]缓冲时钟输出,Bank A.

4 VDD 3.3 V电源

5 GND地

6 CLKB1 [4]缓冲时钟输出,Bank B.

7 CLKB2 [4]缓冲时钟输出,Bank B.

8 S2 [5]选择输入,位2

9 S1 [5]选择输入,位1

10 CLKB3 [4]缓冲时钟输出,Bank B.

11 CLKB4 [4]缓冲时钟输出,Bank B.

12 GND接地

13 VDD 3.3 V电源

14 CLKA3 [4]缓冲时钟输出,Bank A.

15 CLKA4 [4]缓冲时钟输出,Bank A.

16 CLKOUT [4]缓冲输出,该引脚的内部反馈

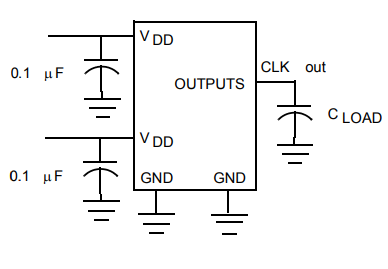

测试电路#1

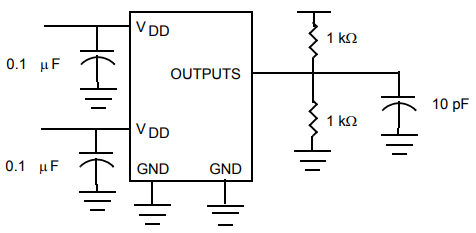

测试电路#2

开关特性

适用于CY2305SI-1H和CY2309SI-1H工业温度装置参数[28]描述条件最小值典型值最大值单位

t1输出频率30 pF负载10 - 100 MHz10 pF负载10 - 133.33 MHz

tDC占空比[29] =t2?t1在1.4 V时测量,Fout = 66.67 MHz 40.0 50.0 60.0%

tDC占空比[29] =t2?t1在1.4 V时测量,Fout <50 MHz 45.0 50.0 55.0%

t3上升时间[29]在0.8 V和2.0 V之间测量 - - 1.50 ns

t4下降时间[29]在0.8 V和2.0 V之间测量 - - 1.50 ns

t5输出到输出偏斜[29]所有输出均等负载 - 85 250 ps

t6A延迟,REF上升沿到CLKOUT上升沿[29]在VDD / 2 - - ±350 ps下测量

t6B延迟,REF上升沿到CLKOUT上升沿[29]在VDD / 2下测量。测量中PLL旁路模式,CY2309器件只要。1587ns

t7器件到器件的偏斜[29]在CLKOUT上以VDD / 2测量设备的引脚- - 700 ps

t8输出压摆率[29]在0.8 V和2.0 V之间测量使用测试电路#21 - - V / ns

tJ周期间抖动[29]测量为66.67 MHz,负载输出- 60200ps

tLOCK PLL锁定时间[29,30,31]稳定的电源,有效时钟在REF引脚上显示- - 1.0毫秒

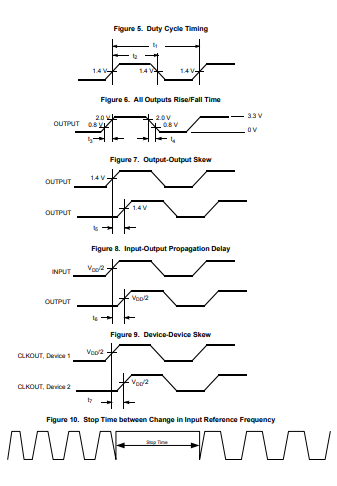

切换波形图