功能描述

低功耗CMOS技术Microchip Technology Inc.93XX86A/B/C设备

为“86C”版本选择字大小的ORG引脚为16K位低压串行电可擦除

2048 x 8位组织“A”设备(无组织)PROM(EEPROM)。字可选设备,如

1024 x 16位组织“B”设备(无组织)93XX86C依赖于外部逻辑驱动组织pin设置单词大小的级别。对于8226;程序使能管脚写入保护整个专用8位通信,93XX86A设备阵列可用,而93XX86B设备提供

自定时擦除/写入周期(包括专用16位通信,可在SOT-23上使用)仅自动擦除)设备。程序启用(PE)引脚允许

在wral用户之前自动生成一个General,以对整个内存阵列进行写保护。

电源开/关数据保护电路先进的CMOS技术使这些设备

工业标准3线串行I/O,适用于低功耗、非易失性内存应用。整个93xx系列在标准包中提供-•设备状态信号(就绪/忙碌),包括8线PDIP和SOIC,以及高级

顺序读取功能包装,包括8导联MSOP、6导联SOT-23,

1000000个E/W循环和8导联TSSOP。无铅(纯哑光锡)饰面

数据保留期>200年。

支持的温度范围:

-工业(I)-40°C至+85°C包装类型(不按比例)

-汽车(E)-40°C至+125°C PDIP/SOIC

电气特性

绝对最大额定值)VCC 7.0V所有输入和输出w.r.t.vss-0.6V至VCC+1.0V储存温度-65°C至+150°C通电环境温度所有插脚的静电放电保护

注意:超过“绝对最大额定值”的应力可能对设备。这只是一个应力额定值和设备在上述条件或任何其他条件下的功能操作。

本规范的操作清单中所示的内容并不暗示。暴露在最大额定条件下延长时间可能会影响设备的可靠性。

功能描述数据的数据(di /暂停/ DO)

当牛津引脚连接*冰的VCC(X16),它是可能的两个连接的数据和数据的出销组织选定的冰。当它被连接在一起。然而,和这是可能的配置信息地面的冰(X8)选定的组织。指令,一个“两occur总线冲突”在“虚拟零。”地址和数据写入到底是clocked………precedes引脚的读操作,如果是一个逻辑高A0The rising edge of the时钟(CLK)。在DO引脚的冰的水平。在这样一种状态的电压电平来看到normally成功地在一个高阻抗状态,当我阅读了undefined和冰的数据将在《depend相对数据从设备,或检查的时候准备/阻抗数据的时间和信号源驱动忙碌的状态,在一个程序的操作。《a0。在更高的电流能力的采购就绪/忙状态的验证可以在擦/驱动器的电压,高出的数据引脚。在写操作的城市轮询的DO引脚;低阶indicates做这两个限流电阻,A应该是conthat编程仍然在进步,虽然不高nected之间的DI和DO。

《冰indicates设备的准备。你将进入“高Z州立大学对边缘降的CS。2.3数据保护典型空调一启动电压(1.5V的93aa’的93lc器件所有的操作模式时,VCC是抑制冰的下面《冰detected起始位的装置,如果CS和底或是3.8V的93C的器件。

高登都在积极边缘的时钟的艾文和EWDS commands提供额外的第一次。对意外的编程,在保护在一开始detected空调冰、CS、CLK、二、正常操作。

在任何可能的变化(除了这两个组合的一个注:加保护,EWDS命令启动空调),没有在任何设备resulting应该performed售后的每一个写操作(读、写、擦、打,EWDS的操作。eral或wral)。只要CS高冰,冰的装置没有语言,在待机模式。上电后,冰的自动装置

EWDS的模式。因此,即使指令必须下面的一个指令启动空调将是只读的performed之前的初始擦或写指令如果executed所需的操作码,地址和数据位可以executed。

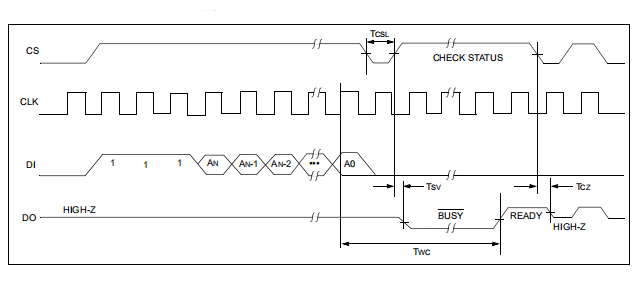

擦除do-pin指示

如果CS在至少250 ns后升高,则为设备擦除指令强制低(TCSL)的所有数据位。逻辑“0”处的do表示编程逻辑“1”状态的指定地址。上升仍在进行中。Do at逻辑“1”表示CLK的边缘在最后一个地址位开始之前,在指定地址的寄存器已被擦除,并且写入周期。设备已准备好接受另一条指令。

注:发出一个起始位,然后使cs低将从清除就绪/忙碌状态

全部清除(通用)DO引脚指示

设备,如果CS在至少250 ns后变高,则全部清除(ERAL)指令将清除整个低(TCSL)。内存数组处于逻辑“1”状态。肠外循环是与擦除周期相同,但不同的注释除外:发出一个起始位,然后使cs低操作码。全自动循环是完全自动定时的。将从清除就绪/忙碌状态在最后一个数据位启动DO之前CLK的上升沿。

写入周期。CLK管脚的时钟不需要VCC必须大于等于4.5 V才能正常运行。

RASE/WRITE禁用和启用(EWDS/EWEN)

93XX86A/B/C在擦除/写入过程中通电,以防止意外数据干扰,禁用(EWDS)状态。所有编程模式必须是EWDS指令,可用于禁用所有擦除/前面有一个擦除/写入启用(EWEN)指令-写入函数,应遵循所有编程tion. 一旦执行EWEN指令,程序操作。读取指令的执行是在EWDS指令独立于EWN和EWDS指令之前,Ming保持启用状态。

已执行或VCC已从设备中删除。

读取设备)输出字符串。输出数据位将打开

CLK的上升沿在规范后稳定,读指令输出化时间延迟(TPD)的串行数据。在DO引脚上寻址存储器位置时,可以进行顺序读取。一个虚拟的CS被高举着。内存数据将自动循环0位在8位之前(如果ORG管脚低或A版本到下一个寄存器并按顺序输出)。设备)或16位(如果Org Pin为高或B版本

写入do-pin指示

设备,如果cs在至少250 ns后变高,则写指令后接8位(如果org低(tcsl)。逻辑“0”处的do表示编程低或A版本设备)或16位(如果org pin为高,则仍在进行中。逻辑“1”上的do表示在指定地址写入寄存器的数据的或b版本设备已使用指定地址写入。由CLK指令的上升沿启动自定时自动擦除和指定的数据以及设备准备好进行另一个编程循环。

在最后一个数据位上。

注:发出一个起始位,然后使cs低将从清除就绪/忙碌状态

全部写入(wral)do pin指示

设备如果cs在至少250 ns后变为高位,则write all(wral)指令将写入整个低位(tcsl)。具有命令中指定的数据的内存数组。自动定时自动擦除和编程周期为:发出一个起始位,然后使cs低在最后一个数据位上由CLK的上升沿启动。将从清除就绪/忙碌状态完成后无需对CLK销进行计时。

设备已进入wral循环。Wral VCC必须大于等于4.5 V才能正常运行。命令包括自动的通用循环设备。因此,wral指令不需要通用指令

芯片选择(CS)3.3数据输入(DI)高电平选择设备;低电平取消选择(DI)中的数据用于在起始位、操作码中时钟。设备并强制其进入待机模式。但是,地址和数据与CLK输入同步。

正在进行的编程周期将是

完成,不考虑芯片选择(CS)输入3.4数据输出(DO)信号。如果在一个程序周期内使cs变低,则一旦在读取模式下使用数据输出(DO)输出数据,设备将进入待机模式。编程循环完成。与CLK输入同步(POSIC后的TPD必须在CLK的活动边缘之间低250 ns(TCSL))。

连续指令。如果cs低,则内部该pin还提供就绪/忙碌状态信息控制逻辑保持在重置状态。擦除和写入周期中的操作。就绪/忙碌状态信息可在do-pin上找到,如果cs是

串行时钟(CLK)在最低芯片选择低后变高低时间(TCSL)和擦除或写入操作串行时钟用于同步已启动的通信。

主设备和93xx系列之间的阳离子,如果CS被保持,则状态信号在DO上不可用。在整个擦除或写入周期中,操作码、地址和数据位的时钟都处于低位。在这里,在CLK的正边缘。数据位也是时钟情况下,do是在高z模式。如果在CLK的正边缘签出状态。在擦除/写入循环后,数据线将变高

CLK可以在传输中的任何位置停止,以指示设备已就绪。顺序(在高或低水平)并可继续注意:发出一个起始位,然后在时钟高时间(tckh)的任何时间将cs设为低,并将从时钟低时间(TCKL)。这使控制主机可以执行。

自由准备操作码,地址和数据。

CLK是一个“不关心”如果CS是低(设备取消选择)。如果组织(Organization,Organization,Organization,Organization,Organization)cs高,但启动条件尚未达到

检测到(di=0),当ORG引脚连接到VCC或逻辑HI时,任何时钟周期数都可以是由设备接收而不改变其状态(即选择(x16)内存组织)。当组织等待启动条件)。引脚与(x8)存储器的VSS或逻辑LO相连。自定时期间不需要CLK循环写入(即,自动擦除/写入)周期。已选择组织。为了正确操作,组织必须绑定到有效的逻辑级别。

在检测到启动条件后,指定的数字时钟周期数(分别为93XX86A设备始终是X8组织和93XX86B设备始终是x16组织。必须提供CLK)。这些时钟周期是需要在所有要求的操作码、地址和执行指令前的数据位。CLK和DI然后变成不在乎输入等待新的开始要检测条件。

程序启用(PE)

此PIN允许用户启用或禁用此功能将数据写入存储器阵列。如果PE销系好了对于VCC,可以对设备进行编程。如果PE针是绑定到VSS后,编程将被禁止。体育不是在93XX86A或93XX86B上提供。在这些设备上,编程始终启用。这个别针不能浮动,必须绑定到VCC或VSS