CDCVF2510点击型号即可查看芯片规格书

CDCVF2510是一款高性能,低偏移,低抖动,锁相环(PLL)时钟驱动器。它使用了锁相环(PLL)可在频率和相位上精确对齐反馈(FBOUT)输出到时钟(CLK)输入信号。它专门设计用于同步DRAM。 CDCVF2510运行于3.3V VCC。它还提供集成的串联阻尼电阻,使其成为驱动点对点负载的理想选择。一组10个输出提供10个低偏移,低抖动的CLK副本。输出信号占空比调整为50%,与CLK的占空比无关。通过控制(G)输入启用或禁用输出。G输入为高电平,输出与CLK同相和频率切换;当G输入为低电平时,输出为禁用逻辑低状态。与许多包含PLL的产品不同CDCVF2510不需要外部RC网络。环路滤波器PLL封装在片内,最大限度地减少了元件数量,电板空间和成本。因为它基于PLL电路,所以CDCVF2510需要一个稳定时间来实现相位锁定反馈信到参考信号。上电和应用a后需要此稳定时间固定频率,CLK的固定相位信号,或PLL参考或反馈信号的任何变化。通过将AVCC捆绑到地,可以绕过PLL用于测试目的。CDCVF2510的特点是工作温度范围为0°C至85°C。

特征

扩频时钟兼容

工作频率50 MHz至175 MHz

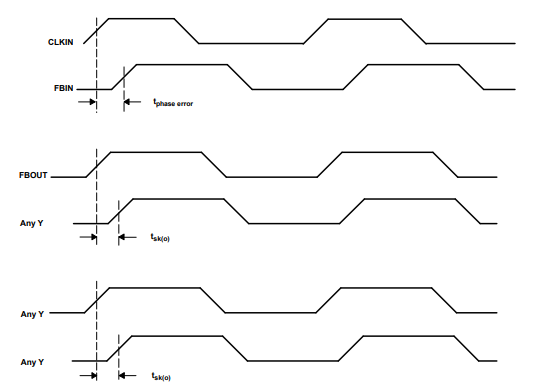

66 MHz至66 MHz的静态相位误差分布166 MHz是±125 ps

66 MHz至166 MHz的抖动(cyc-cyc)是| 70 |PS

高级深亚微米工艺结果功耗降低40%以上与当代PC133器件相对应

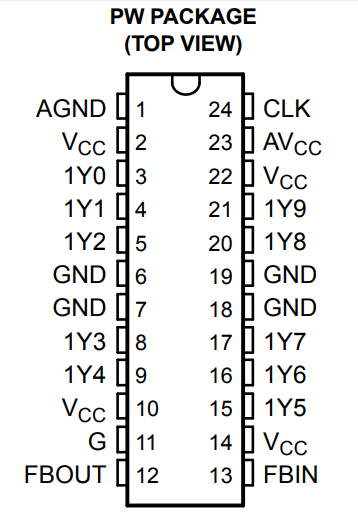

采用塑料24引脚TSSOP封装

锁相环时钟分配同步DRAM应用

将一个时钟输入分配给一个Bank10项产出

外部反馈(FBIN)端子用于将输出同步到时钟输入

25Ω片上系列阻尼电阻器

无需外部RC网络

工作电压为3.3 V.

PW PACKAGE

(顶视图)

终端功能:

CLK提供由CDCVF2510时钟驱动器分配的时钟信号。CLK是用于向产生时钟输出信号的集成PLL提供参考信号。

CLK 24 I CLK必须具有固定频率和固定相位,以便PLL获得锁相。一旦电路上电并施加有效的CLK信号,PLL需要稳定时间将反馈信号锁相至其参考信号。反馈输入。 FBIN为内部PLL提供反馈信号。 FBIN必须硬接线FBIN 13 I FBOUT完成PLL。集成的PLL同步CLK和FBIN以便存在名义上CLK和FBIN之间的零相位误差。输出库启用。 G是输出1Y(0:9)的输出使能。当G为低时,输出1Y(0:9)G 11我禁用了逻辑低状态。当G为高电平时,所有输出1Y(0:9)都被使能并切换到与CLK相同的频率。反馈输出。 FBOUT致力于外部反馈。它以与频率相同的频率切换

FBOUT 12 O CLK。当外部连接到FBIN时,FBOUT完成PLL的反馈环路。FBOUT有集成的25Ω串联阻尼电阻。

3,4,5,8,9,时钟输出。这些输出提供CLK的低偏斜副本。输出bank 1Y(0:9)通过

1Y(0:9)15,16,17,20,G输入。通过置低G控制输入,可以将这些输出禁用为逻辑低状态。

21每个输出都有一个集成的25Ω串联阻尼电阻。模拟电源。AVCC为模拟电路提供电源参考。外,AVCC、AVCC 23 Power可用于绕过PLL进行测试。当AVCC接地时,PLL就是旁路,CLK直接缓冲到器件输出。AGND 1接地模拟地。AGND为模拟电路提供接地参考。

绝对最大额定值:

(2)电源电压范围AVCC <VCC +0.7 V.VCC电源电压范围-0.5 V至4.3 V.VI

(3)输入电压范围-0.5 V至4.6 V.VO

(4)适用于高或低状态-0.5 V至VCC + 0.5 V的任何输出的电压范围一世IK(VI <0)输入钳位电流-50 mAIOK(VO <0或VO> VCC)输出钳位电流±50 mAIO(VO = 0至VCC)连续输出电流±50 mAVCC或GND每个±100 mA的连续电流TA = 55°C(静止空气中)

(5)最大功耗0.7 WTstg存储温度范围为-65°C至150°C

(1)超出“绝对最大额定值”列出的应力可能会对器件造成永久性损坏。这些是应力额定值只有在这些或任何其他条件下,器件的功能操作超出了“推荐操作”中指出的条件条件“并不暗示。 长时间暴露在绝对最大额定条件下可能会影响器件的可靠性。

(2)AVCC不得超过VCC + 0.7 V.

(3)如果观察到输入和输出钳位电流额定值,则可能超过输入和输出负电压额定值。

(4)该值最大限制为4.6 V.

(5)最大封装功耗是使用150°C的结温和750 mils的电路板走线长度计算的。对于更多信息,请参阅ABT高级BiCMOS技术数据手册中的封装散热考虑因素应用说明。

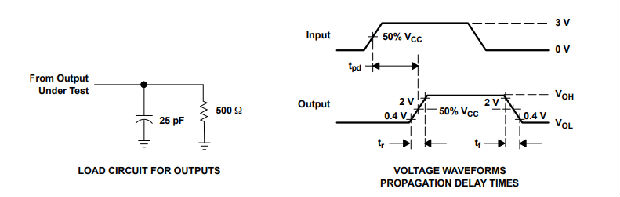

参数测量信息

A:CL包括探头和夹具电容。

B:所有输入脉冲由具有以下特性的发电机供电:PRR≤133MHz,ZO =50Ωtr≤1.2nstf≤1.2ns。

C:一次一个地测量输出,每次测量一次转换。

负载电路和电压波形