设备结构

总线接口模块位于外部总线插脚和与其他功能模块互连的片上16位数据总线之间。它包括几个由总线配置寄存器(BCR)控制的灵活总线接口选项。重置后,BCR自动成为从主机处理器到USC的第一个写入周期的目标。之后,主机软件将无法再访问它。

传输数据路径

主机处理器或外部DMA通道都可以将传输数据写入通道的发送先进先出(FIFO)内存。在任何时候,传输FIFO可以为空,也可以包含1到32个要传输的字符。写入txfifo的字符按写入顺序对发送器可用。

虽然主机处理器本身可以将数据写入发送FIFOS,但使用外部传输DMA通道来获取数据的效率更高。主机可以对USC信道进行编程,使其发送器触发其DMA控制器,以在不同程度的FIFO“空”状态下填充其FIFO。选择这一点涉及到平衡“欠载”发送器的概率和后果,以及更频繁地获取主机总线控制的DMA通道的开销。

串行发送器从发送FIFO中提取字符,并将其转换为TXD管脚上的串行数据。虽然这个功能在概念上很简单,但是USC支持许多复杂的串行协议,这大大增加了发送器的复杂性。根据所选的串行模式,除了并行串行转换之外,发送器还可以执行以下任何操作:开始、停止和奇偶校验位生成、计算和发送CRC、自动生成打开和关闭标志、将串行数据编码为几种格式中的任何一种,以保证转换和携带时钟WI。数据和/或基于CTS引脚控制传输。

接收数据路径

一般来说,接收器的功能与发送器的功能相反:它们监控RxD管脚上的串行数据,根据软件选择的串行模式对其进行组织,并将数据转换为放置在接收FIFO中的并行字符。同样,还有更多的过程,而不仅仅是串行并行转换。根据串行模式,接收器可以

必须检测和同步起始位、检查奇偶校验位和停止位、计算和检查CRC、检测标志、中止和空闲序列、识别控制字符(包括透明度考虑)、使用几种编码方案中的任何一种解码串行数据和时钟提取,和/或基于DCD输入引脚启用和禁用接收。.接收器的检查功能生成与每个字符相关联的几个状态位,这些位伴随着字符通过接收FIFO。

接收FIFO最多可容纳32个字符及其相关的状态位。当接收器将条目写入FIFO时,这些条目对主机处理器或外部接收DMA通道可用。与传输端一样,接收FIFO包括不同程度“满度”的检测逻辑。单独的阈值控制信道开始请求其DMA信道开始重新填充FIFO的点,以及信道请求中断的点。除了主接收FIFO之外,每个通道还有一个4条RCC FIFO,它可以保存指示最多4个接收帧长度的值。

虽然主机处理器可以从接收FIFO访问数据,但使用外部接收DMA通道将数据直接传输到内存中的缓冲区更有效。USC可以在帧的最后一个字符之后,提供串行数据流中每个帧的状态(以及可选的末尾RCC值)。

时钟

每个通道包括一个串行时钟逻辑部分,该部分为通道的发送器和接收器创建时钟信号。软件可以根据每个通道的一个或两个外部时钟对时钟逻辑进行编程,以各种方式实现这一点。每个通道还包括一个数字锁相环(DPLL)电路,可以从RxD上的编码数据恢复时钟。

中断

每个通道中还有一个中断控制部分,它从发送器和接收器收集各种“请求”线路,并负责请求主机中断和响应主机中断确认周期或软件等效周期。中断操作取决于写入总线配置寄存器的数据以及接收器和发送器中的几个寄存器。每个通道都有一组单独的中断插脚,这样外部逻辑就可以控制它们的相对优先级。

总线接口

USC可用于具有各种微处理器或背板总线的系统。它在主机总线接口方面的灵活性源于它的总线配置寄存器(BCR),来自于监视总线的芯片逻辑

在软件写入BCR之前的活动,以及从串行通道中的某些其他寄存器。本节介绍如何使用这些设施将USC与各种主机微处理器和总线连接起来。

多路/非多路操作(续)

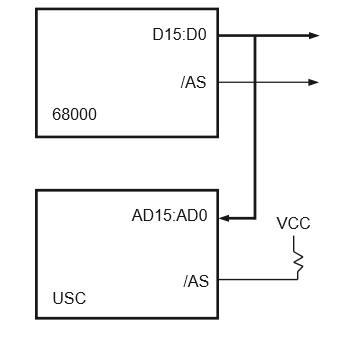

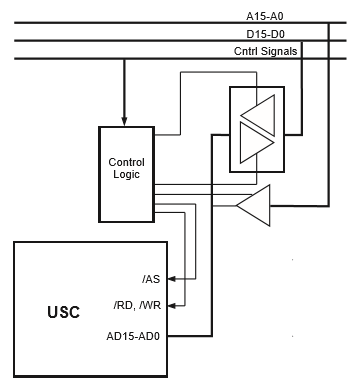

用户友好的非多路总线接口

基于80x86的系统的不同之处在于,处理器的ALE信号必须反转才能为USC生成/AS。

将USC连接到非多路复用主机总线的两种方法。包括最小硬件,但要求软件在每次访问寄存器时将寄存器地址写入USC。在该模式下,应向上拉USC/AS引脚,以确保高逻辑电平恒定。包括将主机地址的低阶位排序到USC的广告行的驱动程序,以及在/AS管脚上合成脉冲的逻辑。这种接口方法的优点是软件可以直接寻址USC的寄存器。

从/复位引脚变高到软件写入总线配置寄存器,USC监控/AS引脚。如果在这段时间内的任何一点上看到/显示为低,那么在软件写入BCR后,USC将在/显示的每个上升边缘捕获低阶广告行、A//B、C//D和/C的状态。如果/as保持高位,软件可能必须在读写寄存器之前将每个寄存器地址写入通道命令/地址寄存器(CCAR)。(如果主机总线仅包括8条数据线,AD13-AD8可以携带寄存器地址。)

读/写数据选通

主机总线之间的另一个区别是读写周期的信号发送和区分方式。USC支持的两种标准方法。总线包括用于读写周期的单独选通线路,通常称为/rd和/wr。总线包括一条数据选通线/ds(读写周期都会变低),以及一条r/w线(区分读写周期)。USC包括所有四个信号的管脚。与主机总线信号匹配的两个信号应连接到这些信号上。应将两个未使用的销拉到较高的水平。

没有可编程选项来区分/rd-/w r和r//w-/ds操作。USC只对任何一对线作出响应,这就是为什么拔出未使用的线对很重要的原因。此外,USC不要求R//W行在/DS断言期间保持有效。它在/ds的前缘/后缘捕获r//w的状态,因此r//w只需要满足与该边缘相关的设置和保持时间。

一次只能激活总线信号/ds、/rd、/wr和/pitack中的一个。当这些管脚用作DMA确认信号时,此禁止还括/rxacka、/rxackb、/txacka和/txackb。(包括“ACK”信号的DMA接口如果USC同时检测到一个以上的输入处于激活状态,它将进入一个非激活状态,唯一的逃逸是通过/复位引脚。

总线宽度

主机总线之间的另一个主要区别是可以在一个周期内传输的数据位的数量。软件可以配置USC一次传输16位,在这种情况下,当需要或需要时,仍然可以传输8位。或者,软件可以限制操作在AD7-AD0引脚上一次仅传输8位。

这使得AD15-AD8引脚没有使用:另一个BCR选项允许它们携带寄存器地址。后一个选项允许软件直接寻址USC寄存器,即使是在非多路复用总线上,也不必在访问寄存器之前将地址写入USC。

ACK与WAIT握手主机总线之间的最后一个主要区别在于握手信号的性质,从属设备使用该信号与主设备进行速度匹配。图2-6说明了常用的三种变体。首先,我们称之为等待信号,如果主设备选择从设备,而从设备无法在允许的时间内捕获写入数据或提供读取数据,使主设备以全速运行,它会快速(组合地)驱动等待输出低,然后在准备完成循环时返回高。一些外围设备具有OpenCollector或开放式漏极的等待输出,这些输出可以连接在一起以实现负逻辑接线或功能。由于USC以全时方式驱动其/wait//rdy输出高或低,逻辑门必须用于负逻辑或(正逻辑和)其/wait//rdy输出,并带有其他从设备的/wait信号,以产生对主设备(如处理器)的/wait输入。

在第二种方案中,“确认”信令,当主设备向所有从设备发送一个周期时,所有从设备必须作出响应,通过将确认信号(有时称为/dtack)降低到允许主设备完成传输,并保持低信号直到主设备完成传输。与前面的方案一样,一些外围设备提供了从机ACK输出,这些输出是开放式收集器或开放式漏极,可以连接在一起以实现负逻辑接线或功能。由于USC以全时方式驱动其/wait//rdy输出高或低,逻辑门必须用于负逻辑或其/wait//rdy输出,并带有其他从站的/ack信号,以产生对主站的确认输入。

在第三种方案中,“准备就绪”信号,当主设备向所有从设备发送一个循环时,所有从设备都必须做出响应,将准备就绪信号驱动到较高位置,以允许主设备完成传输,并保持较高位置,直到主设备完成传输。此方案不同于在循环之间握手信号的默认状态下的等待信号(等待信号高,准备就绪信号低)。它具有与ACK信号相似的定时,但握手信号的极性不同。有了就绪的信令,电路板设计者必须包括一个逻辑门到正逻辑或各种从设备的就绪线路,以产生一个总线主设备的复合就绪输入。

USC支持所有周期的确认和就绪信号,并等待中断确认周期的信号。USC寄存器的访问时间应该足够短,以避免除了最快的处理器以外的所有处理器都需要等待信号。Board Designer可以通过一个外部逻辑门或(用于确认和等待)一个外部三态或开放收集器驱动程序,将USC的/wait//rdy输出与来自其他从系统的类似信号相结合。

如果软件将总线配置寄存器(BCR)写入使A//B引脚低的地址,则USC驱动器/wait//rdy低作为“确认”信号,而如果软件将BCR写入A//B高,则USC驱动器/wait//rdy作为“等待”信号。

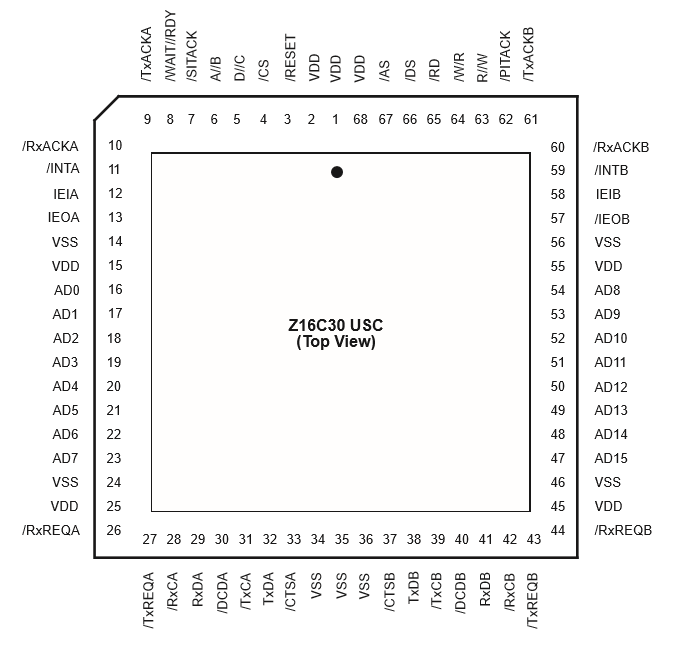

Pin描述

重置。重置(输入,低激活)。这条线路上的低电平使USC处于已知的非活动状态,并对其进行条件调整,使来自下一个断言/cs管脚的写入操作的数据进入总线配置寄存器(BCR),而不考虑寄存器地址。/在通电期间,应尽快将重置降低,并在重新启动整个系统或通信子系统时根据需要将重置降低。

AD15 AD0。地址/数据总线(输入/三态输出)。这些线路在控制微处理器和USC之间传输数据,也可以在USC内传输寄存器的多路复用地址。如果USC与外部DMA控制器一起使用,这些线路也在USC和系统存储器或DMA控制器之间传输数据。AD15-AD0可根据USC在重置后是否感知活动开/关以及写入总线配置寄存器(BCR)的数据以多种方式使用。

/CS。芯片选择(输入,低激活)。这条线上的低值表示控制微处理器的当前总线周期指的是USC中的寄存器。当LOW ON/SITACK或/PITACK指示当前总线操作是中断确认循环时,USC忽略/CS。在多路复用总线上,usc在/as上的上升沿锁定该管脚的状态,而在非多路复用总线上,它在/ds、/rd或/wr上的上升沿/下降沿锁定/cs。

A//B.通道选择(输入,高表示“通道A”)。与/cs low和/sitack、/pitack和此pin一起循环通道A的高访问寄存器。与/sitack和/pitack high一起循环通道B的低访问寄存器和/cs和此pin一起循环通道B的低访问寄存器。写入总线配置寄存器时此行的状态决定“等待”

与确认操作,如本章后面所述。在多路复用总线上,usc在/as上的上升沿锁定该管脚的状态,而在非多路复用总线上,它在/ds、/rd或/wr上的上升沿/下降沿锁定该状态。

D//C.数据/控制(输入,高表示数据)。具有/cs low和/sitack、/pitack和此pin high的读取循环通过其接收数据寄存器(RDR)从A//B选择的通道的接收FIFO中获取数据。具有相同条件的写入周期通过其发送数据寄存器(TDR)将数据写入该通道的发送FIFO。使用/sitack和/pitack high以及/cs和此pin low读取或写入USC寄存器的循环。在多路总线上,USC决定从/AS上升沿的低阶AD线路访问哪个寄存器。在非多路复用总线上,它通常根据串行控制器信道命令/地址寄存器的LSBits选择寄存器。在多路复用总线上,usc在/as上的上升沿锁定该管脚的状态,而在非多路复用总线上,它在/ds、/rd或/wr上的上升沿/下降沿锁定该状态。

。地址选通(输入,低有效)。复位后,USC的总线接口逻辑监控该信号,以查看主机总线是否在AD15-AD0上复用地址和数据。如果逻辑在(或as)软件写入总线配置寄存器之前看到活动,那么在随后指向USC的循环中,它从AD行、A//B和D//C中捕获寄存器选择(位于/as的上升边缘)。

对于非多路复用总线,该管脚应拉高至+5 V。如果处理器使用非多路复用总线,但输出名为地址选通(如680X0设备),则该管脚不应与输出相连。

管脚说明(续)

读/写控制(输入,低表示“写”)。r//w和/ds表示总线上的读写周期,用于具有此类信号的主机处理器/总线。usc在/ds上的每个前缘/后缘处采样r//w。

/DS。数据选通(输入,低激活)。r//w和/ds表示总线上的读写周期,用于具有此类信号的主机处理器/总线。它由/cs low或/sitack low限定。USC在这条线上的每一个前缘/后缘处采样r//w。对于写入周期,USC在该行的上升(后缘)边缘捕获数据。在读取周期中,USC在该线路变低后的指定访问时间内提供AD线路上的有效数据,并且该数据在主设备将该线路变高之前保持有效。

/读频闪灯(输入,低激活)。这一行表示总线上的读周期,用于具有这种信号的主机处理器/总线。它由/cs low或/sitack low限定。在读取周期中,USC在该线路变低后的指定访问时间内提供AD线路上的有效数据,并且该数据在主设备将该线路驱动回高位之前保持有效。

/WR。写入频闪灯(输入,低激活)。这一行表示总线上的写入周期,用于具有这种信号的主机处理器/总线。它是由/cs low限定的。USC捕获该行上升(后缘)的写入数据。

在每个总线周期中,只能将/ds、/rd、/wr或/pitack中的一个驱动低。此限制还包括/txack和/或/rxack(如果它们被用作“flyby”DMA确认信号)。

等待。等待、准备或确认握手(输出、低激活)。这一行可以携带“等待”或“确认”信号,这取决于A//B输入在初始BCR写入期间的状态。如果在写BCR时a//b很高,则此行在此后作为Zilog和某些Intel处理器的就绪/等待行运行。在此模式下,USC将该行断言为低,直到它准备好完成中断确认循环,但当主机访问其中一个USC寄存器时,它从不断言该行。

如果写BCR时A//B很低,则该行随后作为摩托罗拉和某些Intel处理器的确认行运行。在此模式下,USC为寄存器读写周期以及准备完成中断确认周期时断言该行为低。

在任何情况下,这是一个全时输出。Board Designer可以通过外部逻辑门或三态或开放式收集器驱动程序,将此信号与其他从系统的类似信号结合起来。

/INTA,B.中断请求(输出,低激活)。当(1)其IEI管脚高,(2)其一个或多个中断类型被启用和挂起,以及(3)服务中断标志未设置为其最高优先级启用/挂起类型,或通道内的任何高优先级类型时,通道驱动其/int管脚低。USC始终驱动这些管脚高或低-它们既不是三态管脚,也不是开漏管脚。

/坐姿,/坐姿。中断确认(输入,低激活)。其中一行的低值表示主机处理器正在执行中断确认周期。在某些系统中,其中一条线路上的低值可能进一步表明外部逻辑已选择该USC作为要确认的设备,或作为要确认的潜在设备。这两个信号的不同之处在于/sitack应用于水平敏感的“状态”信号,USC应在/as或/ds的前沿采样,而/pitack应用于单脉冲或双脉冲协议。另一个未使用的销应拉到较高的水平。通道将根据其/int和iei行以各种方式响应中断确认循环,如第7章所述。

IEIA,B.中断使能输入(输入,高激活)。这些信号和IEO引脚可以是中断确认菊花链的一部分,与其他可能请求中断的设备一起使用。如果一个通道的IEI管脚在中断确认周期之外很高,并且该通道的一个或多个中断类型被启用并挂起,并且服务标志下的中断没有设置为(最高优先级此类)类型,也没有设置为通道内的任何更高优先级类型,那么该通道通过驱动它来请求中断。S/INT引脚低。如果通道的IEI管脚在IACK循环期间处于高位,则该通道中的一个或多个中断类型被启用并挂起,并且“服务中断”标志未设置为(最高优先级此类)类型或通道中的任何更高优先级类型,则通道强制其IEO线处于低位并响应该循环。

中断使能输出(输出,高电平有效)。这些信号和IEI管脚可以是中断确认菊花链的一部分,与其他可能请求中断的设备一起使用。一个通道在其IEI管脚低的时候驱动其IEO管脚低,和/或每当为通道内的任何类型的中断设置了服务标志下的中断时。在中断确认周期内,这些信号的操作略有不同,因为如果一个通道正在(已经)请求中断,它也会强制其IEO引脚低。

VCC,VSS。电源和接地。每个电源轨包含七个插脚,确保了良好的信号完整性,防止输出瞬态,并提高了输入的噪声裕度。USC的内部配电网络要求所有这些插脚都正确连接。

上拉电阻和未使用的插脚所有未使用的输入插脚都应上拉,要么直接连接到VCC上,要么使用电阻。这可能包括/pitack、/sitack、iei和/abort。

双向插脚通常应该用一个大约10千欧姆的电阻向上拉,以允许USC作为输出驱动它们。这可能包括/txreq、/rxreq、/txc、/rxc、/cts和/dcd。

可能需要向上拉三态输出引脚,以保护外部逻辑不受浮动输入的影响。同样,建议使用大约10千欧姆的电阻。这可能包括/txreq、/rxreq、txd和/int。

总线配置寄存器(BCR)BCR是一个16位寄存器,BCR中的所有位都重置为零。软件在硬件重置后首次访问USC™必须是对BCR的写入。如果主机处理器处理16位数据,并且它与USC之间的数据总线至少16位宽,那么软件对USC的初始访问应该是16位写。此写入可以是到任何激活/cs管脚的地址;数据将放在BCR中。如果主机只能向USC写入字节,则应在AD7-AD0引脚上传输所有数据。在这种系统中,下拉电阻应连接到AD15-AD8引脚,以确保在BCR写入期间这些线路的状态。(AD15可能需要上拉而不是下拉,如下面SEPAD位部分所述。)

等待与就绪选择

当软件写入BCR时,USC捕获A//B管脚的状态。它在BCR写入后使用这个捕获的状态,这样,如果a//b低,它在寄存器访问和中断确认循环期间驱动/wait//rdy pin作为“确认”(或反转的“就绪”)信号,而如果a//b高,它仅在中断确认循环期间驱动pin作为“等待”信号。因此,软件应在与主机总线上使用的从机到主握手类型相对应的地址对BCR进行编程。

BCR中的位和字段

sepad(单独地址;bcr15):该位只能写为1,16位=0。这种组合使USC使用AD7-AD0进行数据处理,并从AD13-AD8中获取寄存器地址。在此模式下,USC从AD8接收上/下字节指示(U//L),从AD13-AD9接收寄存器地址。

使用这种接口技术,BCR必须写在一个地址上,以便AD13-AD8为低/零。此外,当软件写入BCR时,AD15必须为高/一,AD14必须为低/零。设计者可以通过将AD15和AD14连接到更重要的地址行并在适当的地址写入BCR来确保这一点。或者,设计师可以通过将上拉电阻连接到AD15和下拉电阻连接到AD14来确保这一点。

这种模式对于非多路复用总线很有用,以避免让软件在每次寄存器访问之前向CCAR写入寄存器地址。在此模式下,USC捕获/ds、/rd或/wr上每个前缘/后缘的AD13-AD8状态。但是,当USC检测到/AS上的早期活动时,软件仍然可以对sepad=1(16位=0)进行编程。在这种情况下,USC从AD13-AD8在/AS的每个上升沿捕获地址,而不是像SEPAD=0时那样从低阶广告行捕获地址。

BCR中的位和字段(续)

16位(BCR2):当主机数据总线宽16位(或更宽)时,该位应写为1。将该位写为0有两种效果:它限制主机在读写USC寄存器时使用AD7-AD0上的字节传输,并使USC忽略“b//w”信号或寄存器访问位的状态。该位还控制对CCAR、TDR和RDR的“隐式”访问是8位还是16位宽。

2pulseiack(双脉冲中断确认;bcr1):如果没有使用/pitack管脚,或者如果在主机处理器确认中断时它携带单个脉冲,软件应将该位编程为0;如果/pitack在主机处理器确认中断时携带两个脉冲,软件应编程为1。(后一种模式与某些Intel处理器兼容。)

srighta(右移地址;bcr0):该位仅对多路复用总线有效-对于非多路复用总线,USC忽略该位。如果srighta为1,则USC从AD6-AD0引脚捕获寄存器地址,并忽略AD7引脚。在这种模式下,AD0携带上/下

字节指示(U//L),AD5-AD1携带实际寄存器地址,AD6携带字节/字指示(B//W)。如果srighta为0,则USC从AD7AD1捕获地址并忽略AD0。它从AD1中取u//l,从AD6-AD2中取寄存器地址,从AD7中取b//w。该位对S//D和D//C插脚的使用没有影响。

当使用USC作为16位总线上的8位外围设备时,srighta将为0,这不太可能是常见的应用程序。本手册的某些章节假设srighta为1。

BCR中的所有其他位都是保留的,应编程为0。如果处理器只能向USC写入字节,软件只能在AD7-AD0行上写入BCR的8个LSbit。在这种情况下,软件写入BCR时,AD15-AD8的状态必须通过将这些管脚连接到下拉电阻器或(如果sepad=1)连接到主机地址行来确保。

寄存器寻址图2-9的流程图显示了当主机处理器周期断言/cs和/rd、/wr或/ds之一时,USC如何确定要访问哪个寄存器。

在所有寄存器访问中,A//B引脚在USC中的两个串行通道之间选择。USC样品A//B和下文所述的其他销,位于/AS的上升/后缘,或者,如果/AS被拉起以使其始终处于高位,则位于/DS、/RD或/WR的下降/前缘。

隐式数据寄存器寻址

如果USC对D//C管脚高采样,写入操作访问传输数据寄存器(TDR),读取操作选择接收数据寄存器(RDR)。如果总线配置寄存器(BCR2)中的16位为1(表示16位数据总线),则访问隐式为16位宽;如果BCR2为0,则访问隐式为8位宽。

这意味着,在16位总线上,软件既不能向TDR/TXFIFO写入一个字节,也不能使用使D//C高的地址从RDR/RXFIFO读取一个字节。相反,软件必须直接提供TDR/RDR的ls字节的显式地址,或者将其写入CCAR。

AD13-AD8上的直接寄存器寻址

如果USC采样数D//C低,总线配置寄存器(BCR15)中的SEPAD位为1(仅适用于8位数据总线),则USC采样AD13-AD9引脚作为REGAD以选择要访问的寄存器,采样AD8作为U//L以选择要访问的寄存器字节。USC总是以“小尾数”的方式解释一个U/L位,1表示寄存器中更重要的8位。

如果在该模式下,USC将AD13-AD8采样为全部零,指示信道命令/地址寄存器(CCAR),则USC使用CCAR的内容选择要访问的寄存器,如下文“间接寄存器寻址”所述。

每当使用CCAR作为间接地址时,USC随后将CCAR6-0清除为零,以便下次访问CCAR地址时再次引用CCAR本身的所有16位。因此,在向中央结算系统写入一个寄存器地址后,读取或写入中央结算系统地址将访问由所写入的地址选择的寄存器,但随后对中央结算系统地址的另一个写入将地址再次写入中央结算系统。

CCAR始终可用于选择一个寄存器,以便随后访问CCAR地址,即使USC在重置后检测到活动开/关,并且不考虑SEPAD(BCR15)的状态。

通常,当软件使用间接寄存器寻址时,CCAR地址是它唯一读取和写入的地址,其他所有访问都是写入寄存器地址。注意,CCAR本身可以在单个读写操作中访问:例如,在16位总线上向rtcmd字段写入命令时,软件不必首先写入CCAR的地址(零)。通过在rtcmd中发出命令和/或更改rtmode字段,可以在相同的写入操作中为下一次访问ccar指定寄存器地址。

第4章中的“RxD和TXD引脚”描述了CCAR中的RTMODE字段如何控制发送器和接收器之间的回声和环路。通常,此字段为零,但在使用间接寄存器寻址和非零RTMODE值的应用程序中,当软件将寄存器地址写入CCAR时,必须注意保留RTMODE的当前值。

当使用间接寻址时,一些硬件/软件机制必须防止USC中断,或导致上下文从中断的USC任务切换开的任何中断,从地址写入CCAR的时间到后续读取或写入完成的时间。这是因为已经写入CCAR的地址是被中断任务的上下文的一部分,希望被保存,但无法从USC中读取这样的地址-读取CCAR将返回地址寄存器的内容。

AD6-AD0/AD7-AD1上的直接寄存器寻址

如果USC样本D//C低,SEPAD(BCR15)为0,并且USC检测到BCR之前或写入BCR时的活动,则USC对低阶AD管脚取样,以确定要访问的寄存器。如果srighta(bcr0)为1,则从ad5-1获取寄存器选择(regad);如果srighta为0,则从ad6-ad2获取寄存器选择(regad)。如果16位(bcr2)为1,则usc将ad6(如果srighta/bcr0为0,则为ad7)采样为b//w,以确定如果寄存器(如果b//w为0)或仅为8,是访问所有16位。如果16位为0或b//w为1,则采样ad0(如果srighta为0,则采样ad1)作为u//l,以选择要访问寄存器的哪个字节。USC总是以“小尾数”的方式解释一个U/L位,1表示寄存器中更重要的8位。对于所有16位访问,u//l应为0。

如果在该模式下,USC将AD6-0(或7-1,如果srighta为1)采样为全部零,表明信道命令/地址寄存器(CCAR),则USC使用CCAR的内容选择要访问的寄存器,如下一节所述。

CCAR中的间接寄存器寻址

如果USC样品D/C低,并且:

1。SEPAD(BCR15)为1,USC样本AD13-AD8均为零,表示CCAR,或

2。SEPAD为0,USC检测到BCR之前或写入BCR时的活动,并将AD6-AD0取样为0,表示CCAR,或

三。SEPAD为0,且USC未检测到之前或BCR编写时的活动,

然后,它使用CCAR的低有效字节来选择要访问的寄存器。

图2-8显示了综合资本分析及审查。当USC从中获取间接寄存器地址时,REGAD字段(CCAR5-1)选择要访问的寄存器。如果16位(bcr2)为1,USC使用ccar6作为b//w来决定是访问寄存器的所有16位(如果b//w为0)还是仅访问8位。如果16位为0或b//w为1,则使用ccar0作为u//l来选择要访问寄存器的哪个字节。

USC总是以“little endian”的方式解释一个u/l位,1表示寄存器中更重要的8位。对于所有16位访问,u//l应为0。

USC中可寻址寄存器的名称和地址。表中假设srighta(bcr0)为1。表中的regaddr列反映了适用的ad5-ad1、ad13-ad9或ccar5-1的状态。

如果“16位”(bcr2)为1,则来自ad6、ad14或ccar6的b//w位选择16位传输(如果为0/低)和8位传输(如果为1)。如果“16位”为0,则USC忽略AD6、AD14或CCAR6(如适用)。请注意,表2-1和表2-2的“8位数据”列中的值包括直接和间接寻址的b//w位1,这在16位总线上是必需的。当16位(bcr2)为0时,这些地址值可以如图所示使用,或比“16位数据”列中所示的地址低64位。

对于8位或16位总线上的8位传输,AD0、AD8或CCAR0的状态选择寄存器的低有效8位(如果0/低)或高有效8位(如果1/高)。在这方面,USC就像英特尔的微处理器一样是“小端”。对于16位传输,AD0、AD8或CCAR0必须为0/低。

表的直接地址列假定:(1)srighta(bcr0)为1,

(2)处理器的多路AD6-AD0线连接到AD6-AD0,或其A5-A0线连接到AD13-AD8,具体取决于SEPAD(BCR15)。

(3)直流针接地,且

(4)处理器的A7线连接到A//B。

如果您的设计与这些假设不同,寄存器寻址将与直接地址列中显示的不同。

串行数据寄存器TDR和RDR

RDR和TDR实际上是“同一寄存器位置的读写端”。当地址的其余部分表明可以访问TDR或RDR时,USC忽略AD4、AD12或CCAR4(如适用)的状态。为简单起见,表2-1和2-2显示了较低地址的RDR和较高地址的TDR。

RDR和TDR的MSBytes不应单独读写,只应作为16位访问的一部分。在Zilog 16c0x或Motorola 680x0系统上,通道B使用直接地址97或113(61或71 Hex),通道A使用225或241(e1或f1 Hex),选择字节传输的lsbyte。在基于Intel的系统上,相应地使用地址96、112、224或240(60、70、e0、f0 hex)来选择字节传输的lsbyte。

字节顺序

不同的微处理器在字节地址之间的对应关系以及字节在16位或32位值内的排列方式上有所不同。ZilogZ80和大多数Intel处理器使用有时被称为“小endian”的约定:字的最低有效字节的地址最小,最高有效字节的地址最大。

Zilog16c0x和Motorola680x0处理器是“bigendian”:它们存储和获取低位地址字节中的msbyte和高位地址中的lsbyte。

USC寄存器中字节的寻址本质上是“小尾数”,这样寄存器的最大字节具有奇数地址。

对于仅16位串行数据传输,通道命令/地址寄存器(CCAR15-11)的rtcmd字段中的两个命令允许USC与任何类型的处理器一起使用。“select d15-8 first”和“select d7-0 first”命令控制串行数据16位传输中的字节顺序,并应用于DMA和处理器访问RDR和TDR。

寄存器读写周期

主机处理器读取或写入USC寄存器时所涉及信号的波形。单独的图纸包括多路地址和数据总线上的信号,以及单独地址和数据线的总线。另一方面,由于波形在前几次之后变得很无聊,所以已经做了一些事情来最小化数字的数量。

通过将选通记录道标记为“/ds或/rd”和“/ds或/wr”,将分别读写选通与方向线和公共数据选通的情况结合起来。方向线r//w如图所示,但注释提醒读者其状态与/rd和/wr无关。

“wait”和“acknowledge”信号之间的区别是通过将/wait//rdy跟踪显示为“maybe or maybe not”变低,并加上适当的标签来处理的。(在寄存器访问周期中,USC从不断言“等待”指示。)

是简单USC应用程序的示意图。它包括一个USC、一个80186集成处理器、两个EPROM、两个静态RAM和3个串行接口。

是一种八进制锁存器,它从186年开始捕获地址,并将锁存地址呈现给RAM和EPROM。EPROM由186的上芯片选择(/ucs)输出选择,而RAM由下芯片选择(/lcs)输出选择。美国南加州大学

驻留在I/O空间中,一个通道由186'外围芯片选择输出(PCS0)中的第一个选择,另一个通道由另一个(PCS1)选择。

28针EPROM插槽设置为接受2764、27128、27256或27512。32针RAM插槽可以接受32针128KX8或28针32KX8静态RAM。

U10 74FCT240在186上的激活高信号和USC上的激活低信号之间转换信号。USC信道A的/txreq和/rxreq管脚颠倒,使80186'集成DMA信道的DMA请求0和1输入。这意味着USC信道A可以使用DMA操作,而USC信道B必须是中断驱动或轮询的。由于186’DMA信道采用了流通(两个周期)操作,因此信道A/Txack和/Rxack插脚可在串行接口中自由使用。

USC包括几种串行接口选项和功能,可提高其在各种应用中的实用性。它允许各种时钟方案,并将为NRZI和双相格式进行串行编码和解码,这些格式携带带有串行数据的时钟信息。USC还支持这种芯片上解码

数字锁相环电路。最后,它提供可连接到调制解调器控制和状态信号、与串行链路相关的其他控制和状态线路,甚至与与串行链路无关的输入和/或输出信号的I/O线路。

串行接口引脚说明

Rxda,b.接收数据(输入,正逻辑)。每个通道的串行输入。

发送数据(输出,正逻辑)。每个通道的串行输出。

/RXCA,B.接收时钟(输入或输出)。这些信号可用作每个信道内任何功能块的时钟输入。或者,软件可以对一个信道进行编程,使该管脚是一个输出,其中包含多个接收器或内部时钟信号、通用输入或输出或中断输入。

/TXCA,B.发送时钟(输入或输出)。这些信号可用作每个信道内任何功能块的时钟输入。或者,软件可以对一个信道进行编程,使该管脚是一个输出,其中包含几个发送器或内部时钟信号、通用输入或输出或中断输入中的任何一个。

/RxREQA,B.接收DMA请求(输入或输出)。这些管脚可以从每个通道的接收FIFO承载一个低激活的DMA请求。如果DMA传输不用于信道的接收器,则其RxREQ管脚可用作通用输入或输出,或用作中断输入。

/发送DMA请求(输入或输出)。这些管脚可以从每个通道的发送FIFO传输一个低激活的DMA请求。如果DMA传输不用于信道的发送器,则其TXREQ引脚可用作通用输入或输出,或用作中断输入。

/rxacka,b.接收DMA确认(输入或输出)。如果一个外部的“flyby”DMA控制器被用于一个信道的接收数据,这个管脚携带来自DMA控制器的低激活确认信号。如果一个信道的接收器没有使用DMA传输,或者如果DMA控制器使用的是流通(两个周期)而不是飞驰操作,则该信道的Rxack管脚可以用作通用输入或输出。

/发送DMA确认(输入或输出)。如果一个外部的“flyby”DMA控制器被用于一个信道的传输数据,那么这个管脚携带来自DMA控制器的低激活确认信号。如果一个信道的接收器没有使用DMA传输,或者如果DMA控制器使用的是流通(两个周期)而不是flyby操作,则该信道的txack pin可以用作通用输入或输出。

/数据载波检测(输入或输出,低电平有效)。软件可以对信道进行编程,使该信号启用/禁用其接收器。此外,或者相反,软件可以编程一个通道来请求中断以响应这条线上的转换。这些插脚也可以用作简单的输入或输出。

/CTSA,B.清除发送(输入或输出,低激活)。软件可以对信道进行编程,使该信号启用/禁用其发送器。此外,或者相反,软件可以编程一个通道来请求中断以响应这条线上的转换。这些插脚也可以用作简单的输入或输出。