介绍 功能 体系结构概述 包装标记 订购信息模块:功能描述DS312(v4.2)输入/输出块(IOB)概述 Selectio信号标准 可配置逻辑块K(CLB) 块RAM 专用倍增器 数字时钟管理器(DCM) 时钟网络 配置 为斯巴达3e FPGA供电 生产步进

模块3:直流和开关特性DS312(v4.2)直流电气特性8226;绝对最大额定值•电源电压规格•推荐操作条件•直流特性•开关特性•I/O定时•片定时•DCM定时•块RAM定时•倍增器定时G•配置和JTAG定时模块4:插脚说明DS312(v4.2)插脚说明•包装概述•插脚表

简介:Spartan3e系列现场可编程门阵列(FPGA)专门设计用于满足大容量、成本敏感的消费电子应用的需求,五成员家庭提供的系统门密度范围为100000至160万。Spartan-3e系列通过增加每个I/O的逻辑量,显著降低每个逻辑单元的成本,建立在早期Spartan-3系列的成功基础上。新功能提高了系统性能并降低了配置成本。这些Spartan-3e FPGA增强功能与先进的90纳米工艺技术相结合,每美元提供比以前更多的功能和带宽,为可编程逻辑行业设定了新的标准。由于其极低的成本,斯巴达3e FPGA非常适合广泛的消费电子应用,包括宽带接入、家庭网络、显示/投影和数字电视设备。斯巴达-3e系列是掩模编程ASIC的一个更好的选择。FPGA避免了初始成本高、开发周期长和传统ASIC固有的不灵活。此外,FPGA的可编程性允许在现场进行设计升级,而无需更换硬件,这是ASIC不可能实现的。

功能•非常低的成本、高性能逻辑解决方案,适用于大容量、面向消费者的应用•成熟的90纳米工艺技术•多电压、多标准Selectio接口引脚•高达376个I/O引脚或156个差分信号对

•LVCMOS、LVTTL、HSTL和SSTL单端信号标准•3.3V、2.5V、1.8V、1.5V和1.2V信令•每个I/O的数据传输速率为622+MB/s•真正的LVDS、RSDS、迷你LVDS、差分HSTL/SSTL差分I/O•增强的双数据速率(DDR)支持•DDR SDRAM支持高达333 MB/s•丰富灵活的逻辑资源•D高达33192个逻辑单元,包括可选移位寄存器或分布式RAM支持•高效宽多路复用器、宽逻辑•快速前瞻性进位逻辑•增强型18 x 18多路复用器和可选管道•IEEE 1149.1/1532 JTAG编程/调试端口•分层选择RAM内存结构•高达648 kbits快速块RAM•高达231 kbits的高效分布式RAM•高达8个数字时钟管理器(DCMS)•时钟偏差消除(延迟锁定环路)•频率合成、乘法、除法•高分辨率移相•宽频率范围(5 MHz至300 MHz以上)•8个全局时钟加上每个附加的8个时钟每半个设备,加上丰富的低歪斜路由•配置接口到行业标准PROM•低成本、节省空间的SPI串行闪存PROM•X8或X8/X16并行或非闪存PROM•低成本的Xilinx平台闪存,带JTAG•完整的Xilinx ISE和Webpack软件•Microblaze和Picoblaze嵌入式处理器CORES•完全兼容32/64位33兆赫PCI支持(某些设备支持66兆赫)•低成本QFP和BGA封装选项•通用封装支持轻松密度迁移•无铅封装选项•XA汽车版

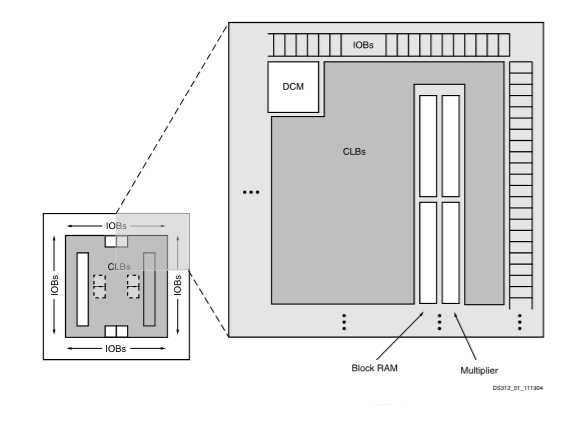

体系结构概述Spartan-3e系列体系结构由五个基本的可编程功能元素组成:•可配置逻辑块(CLB)包含灵活的查找表(LUT),用于实现逻辑加上用作触发器或闩锁的存储元素。CLB执行各种各样的逻辑功能以及存储数据。•输入/输出块(IOB)控制输入/输出引脚和设备内部逻辑之间的数据流。每个IOB都支持双向数据流加上3态操作。支持多种信号标准,包括四种高性能差分标准。包括双数据速率(DDR)寄存器。•块RAM以18 kbit双端口块的形式提供数据存储。•乘法器模块接受两个18位二进制数作为输入,并计算乘积。

•数字时钟管理器(DCM)模块为分配、延迟、乘法、分频和移相时钟信号提供自校准全数字解决方案。这些元素按图1所示进行组织。一个IOB环围绕着一个规则的CLB数组。每个设备有两列块RAM,XC3S100E除外,XC3100E有一列。每个RAM列由几个18 kbit RAM块组成。每个块RAM都与一个专用的乘数相关联。DCMS位于中央,两个位于设备顶部,两个位于设备底部。xc3s100e的顶部和底部只有一个DCM,而xc3s1200e和xc3s160e在左侧和右侧的中间添加了两个DCM。Spartan-3e系列具有丰富的跟踪网络,将所有五个功能元素相互连接,在其中传输信号。每个功能元素都有一个相关的开关矩阵,允许多个连接到路由。

配置spartan-3e FPGA通过将配置数据加载到健壮的、可重新编程的静态CMOS配置闩锁(CCL)中进行编程,CCL共同控制所有功能元素和路由资源。FPGA的配置数据存储在外部的可编程只读存储器或其它非易失性介质中,无论是板上还是板下。通电后,配置数据使用以下七种不同模式中的任意一种写入FPGA:•来自xilinx平台的主串行flash prom•来自行业标准SPI串行flash的串行外围接口(SPI)•来自行业标准X8或X8/X16并行NOR flash的字节外围接口(BPI)向上或向下•SLAve serial,通常从处理器下载•slave parallel,通常从处理器下载•boundary scan(JTAG),通常从处理器或系统测试仪下载。此外,spartan-3e FPGA支持多引导配置,允许将两个或多个FPGA配置位流存储在单个并行NOR闪存中。FPGA应用程序控制下一步要加载的配置以及何时加载。

I/O功能Spartan-3e FPGA Selectio接口支持许多流行的单端和差分标准。表2显示了用户I/O的数量以及每个设备/包组合可用的差分I/O对的数量。Spartan-3e FPGA支持以下单端标准:•3.3V低压TTL(LVTTL)•3.3V、2.5V、1.8V、1.5V或1.2V时的低压CMOS(LVCMOS)•33MHz时的3V PCI,在某些设备中,1.8V时的66MHz•HSTL I和III,通常用于内存应用•1.8V和2.5V时的SSTL I,通常用于内存应用N-3E FPGA支持以下差分标准:•LVDS•总线LVDS•微型LVDS•RSDS•差分HSTL(1.8V,I型和III型)•差分SSTL(2.5V和1.8V,I型)•2.5V LVPECL输入

如体系结构概述所述,Spartan-3e FPGA体系结构由五个基本功能元素组成:•输入/输出块(IOB)•可配置逻辑块(CLB)和切片资源•块RAM•专用乘数•数字时钟管理器(DCMS)。以下各节提供了n每个函数。此外,本节还介绍了以下功能:•时钟基础设施•互连•配置•为Spartan-3e FPGA供电

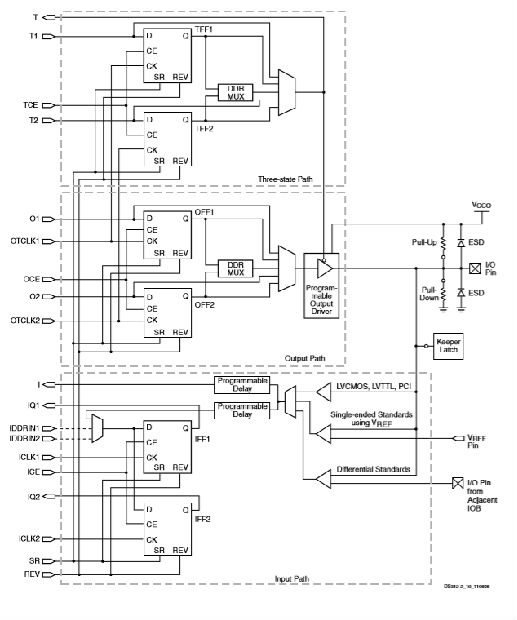

IOB概述输入/输出块(IOB)在封装引脚和FPGA内部逻辑之间提供可编程、单向或双向接口。IOB类似于Spartan-3系列,有以下区别:•只添加输入块•所有块都添加可编程输入延迟•DDR触发器可以在相邻IOB之间共享单向输入块具有完整IOB功能的子集。因此,输出路径没有连接或逻辑。以下段落假定对输出功能的任何引用都不适用于仅输入块。只输入块的数量随设备大小而变化,但永远不会超过IOB总数的25%。IOB内部结构的简化图。IOB中有三个主要的信号路径:输出路径、输入路径和三态路径。每个路径都有自己的一对存储元素,可以用作寄存器或闩锁。有关详细信息,请参见存储元素函数。三个主要信号路径如下:•输入路径通过可选的可编程延迟元件直接将数据从焊盘(焊盘与封装管脚相连)传送到I线。在延迟元素之后,通过将存储元素对到iq1和iq2行。IOB输出i、iq1和iq2导致了FPGA的内部逻辑。可以设置延迟元素以确保保持时间为零(参见输入延迟功能)。•输出路径从O1和O2线开始,通过多路复用器从FPGA内部逻辑传输数据,然后三态驱动程序传输到IOB板。除此直接路径外,多路复用器还提供插入一对存储元素的选项。•3态路径决定输出驱动器何时为高阻抗。T1和T2线通过多路复用器将来自FPGA内部逻辑的数据传输到输出驱动器。除此直接路径外,多路复用器还提供插入一对存储元素的选项。•所有进入IOB的信号路径,包括与存储元件相关的路径,都有一个反相器选项。放置在这些路径上的任何反相器都会自动吸收到IOB中。

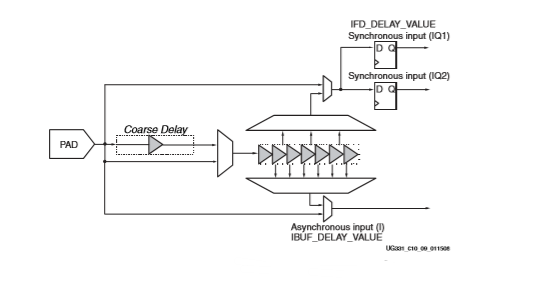

输入延迟功能每个IOB都有一个可编程延迟块,可以选择延迟输入信号,信号路径有一个可以绕过的粗延迟元素。然后,输入信号向6抽头延迟线供电。粗延迟和抽头延迟各不相同;有关特定延迟值,请参阅定时报告。所有六个抽头都可以通过多路复用器直接作为异步输入使用到FPGA结构中。这样,延迟可以通过12个步骤进行编程。六个抽头中的三个也可通过多路复用器连接到同步存储元件的D输入端。插入到存储元素路径中的延迟可以分六步进行更改。第一个粗延迟元素对于异步和同步路径都是通用的,必须对这两个路径都使用或不使用粗延迟元素。延迟值在配置时在硅中设置一次,它们在设备操作中是不可修改的。输入延迟元件的主要用途是调整输入延迟路径,以确保在将输入触发器与全局时钟一起使用时不需要保持时间。默认值由xilinx软件工具自动选择,因为该值取决于设备大小和触发器所在的特定设备边缘。xilinx ISE软件设置的值显示在地图中。

由实现工具生成的报告,以及对输入定时产生的影响,使用定时分析器工具进行报告。如果设计在时钟路径中使用DCM,那么可以安全地将延迟元素设置为零,因为延迟锁定循环(DLL)补偿自动确保仍然没有输入保持时间要求。异步和同步值都可以修改,这在时钟或数据输入需要额外延迟的情况下非常有用,例如,在各种类型RAM的接口中。这些延迟值通过ibuf_delay_值和ifd_delay_值参数定义。默认的ibuf_delay_值为0,绕过异步输入的延迟元素。用户可以将此参数设置为0-12。默认的ifd_delay_值是auto。对于每个输入,ibuf_delay_值和ifd_delay_值是独立的。如果相同的输入端同时使用已注册和未注册的输入路径,则可以使用这两个参数,但它们必须都在总延迟的一半内(都是绕过或使用粗糙延迟元素)。

存储元素功能每个IOB中有三对存储元素,三条路径中的每一对都有一对。可以将这些存储元素配置为边缘触发的D型触发器(fd)或电平敏感锁存器(ld)。输出路径或三态路径上的存储元素对可与专用多路复用器一起使用,以产生双数据速率(DDR)传输。这是通过获取数据来完成的

与时钟信号的上升沿同步,并将其转换为上升沿和下降沿同步的位。两个寄存器和一个多路复用器的组合被称为双数据速率D型触发器(ODDR2)。表4描述了与存储元素关联的信号路径。

输出和三个状态路径中的上层寄存器共享一个公共时钟。OTCLK1时钟信号驱动输出和三个状态路径上上层寄存器的CK时钟输入。同样,otclk2驱动输出和三个状态路径上较低寄存器的ck输入。输入路径上的上下寄存器具有独立的时钟线:ICLK1和ICLK2。OCE启用行控制输出路径上上下寄存器的CE输入。同样地,TCE控制三态路径上寄存器对的CE输入,而ICE对输入路径上寄存器对的CE输入相同。进入IOB的设置/重置(SR)行控制所有六个寄存器,反向(REV)行也是如此。除了IOB概述中描述的信号极性控制外,每个存储元件还支持

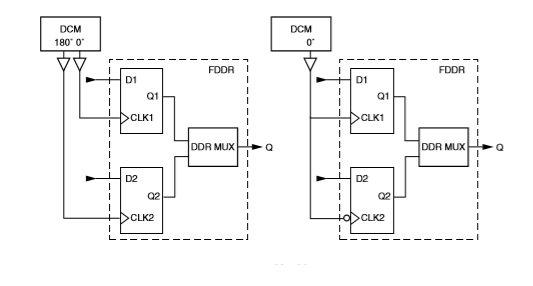

双数据速率传输双数据速率(DDR)传输描述了将信号同步到时钟信号上升和下降边缘的技术。spartan-3e设备在所有三个IOB路径中使用寄存器对来执行DDR操作。IOB输出路径(OFF1和OFF2)上的一对存储元件用作寄存器,与一个特殊的多路复用器结合形成一个DDR D型触发器(ODDR2)。此原语允许DDR传输,其中输出数据位与时钟的上升和下降沿同步。DDR操作需要两个时钟信号(通常为50%的占空比),一个是另一个的倒转形式。这些信号以交替的方式触发两个寄存器,如图7所示。数字时钟管理器(DCM)通过镜像输入信号,然后将其移动180度来生成两个时钟信号。这种方法确保两个信号之间的偏差最小。或者,IOB内的反相器可用于反转时钟信号,因此仅使用一条时钟线和该时钟线的上升和下降沿作为DDR触发器的两个时钟。

三态路径(tff1和tff2)上的存储元素对也可以与本地多路复用器组合以形成ddr原语。这允许同步输出使能对时钟的上升和下降边缘。此DDR操作的实现方式与输出路径相同。输入路径(iff1和iff2)上的存储元素对允许I/O接收DDR信号。传入的DDR时钟信号触发一个寄存器,而反向时钟信号触发另一个寄存器。寄存器轮流捕获传入DDR数据信号的位。允许此功能的原语称为iddr2。除了高带宽数据传输外,DDR输出还可用于在输出上复制或镜像时钟信号。该方法用于同时传输时钟和数据信号(同步源)。类似的方法用于在多个输出端再现时钟信号。这两种方法的优点是,输出之间的偏差最小。

在spartan-3e系列中,一个差分对中的一个IOB可以将其输入存储元素与另一个IOB中的那些作为差分对的一部分进行级联。这是为了使DDR高速操作更容易实现。可用的新DDR连接如图5所示(虚线),仅可用于IOB之间的路由,并且不可由FPGA结构访问。请注意,此功能仅在使用差异I/O标准lvds、rsds和mini_lvds时可用。

三态路径(tff1和tff2)上的存储元素对也可以与本地多路复用器组合以形成ddr原语。这允许同步输出使能对时钟的上升和下降边缘。此DDR操作的实现方式与输出路径相同。输入路径(iff1和iff2)上的存储元素对允许I/O接收DDR信号。传入的DDR时钟信号触发一个寄存器,而反向时钟信号触发另一个寄存器。寄存器轮流捕获传入DDR数据信号的位。允许此功能的原语称为iddr2。除了高带宽数据传输外,DDR输出还可用于在输出上复制或镜像时钟信号。该方法用于同时传输时钟和数据信号(同步源)。类似的方法用于在多个输出端再现时钟信号。这两种方法的优点是,输出之间的偏差最小。

IDDR2作为DDR输入对,主IOB在ICLK1的上升沿(=d1)和ICLK2的上升沿(=d2)上注册输入数据,这通常与ICLK1的下降沿相同。然后将这些数据传输到FPGA结构中。在某个时刻,两个信号都必须进入同一个时钟域,通常是ICLK1。在高频情况下,这可能很困难,因为假设占空比为50%,可用时间仅为时钟周期的一半。