目录

| 1.轨对轨运放输入级的原理 |

| 2.输入差分对管尾电流控制式 |

| 3.仿真分析 |

| 结束语 |

随着SOC(SystemonChip)的迅速发展,使用深亚微米标准CMOS工艺的模拟集成电路的设计,已成为当前芯片设计的一种趋势。CMOS运算放大器是模拟电路中重要基本单元,该单元不但要具有传统运放的基本特性,如高增益、低失调等;而且随着低电源电压的要求,还必须具备接近于供电电源电压和地之间(轨对轨)的输入共模范围和输出摆幅。因此文中基于0.6mCMOS工艺,设计了一种轨对轨运算放大器。该运算放大器采用了3.3V单电源供电,其输入共模范围和输出信号摆幅接近于地和电源电压。

由传统的差分放大器的直流特性可知,通过适当地选择放大器的直流电流和器件特性参数,对于NMOS差分输入放大电路可以使其共模输入范围的上限值接近于电源电压VDD,但下限值电位距离地参考点很远,达不到轨对轨运放输入级的轨对轨的共模输人的要求。同样,对于PMOS差分输入放大电路可以使其共模输入范围的下限值接近于地参考点,而上限值距离V很远,同样也不能满足轨对轨的共模输入的要求。注意到两种差分输入放大电路对于共模输入范围的互补特性,可将两种电路并连作为运算放大器的输入级,这样该输入级的共模输入范围可满足运放输入级轨对轨的要求。

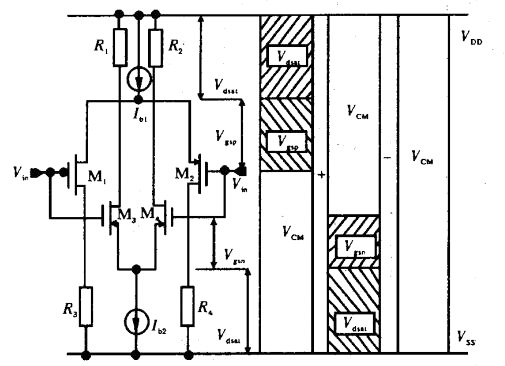

图1 轨对轨输入级电路

互补式运放差分输入电路如图1所示。从图中可以看出,如果NMOS差分对单独工作时,NMOS差分对管M1,M2的输入共模范围为VDD~Vgsn+Vdsat ;如果 PMOS差分对单独工作时,PMOS差分对管M3,M4的输入共模范围为Vss~Vsp+Vdsat;所以两种差分电路并联时的输入共模范围为Vss~VDD,满足了轨对轨输入共模电压范围的要求,输入级的最小电源电压为:

式中,Vgsp为PMOS管的栅源电压;Vsn为NMOS管的栅源电压; Vdsat为采用电流镜作为PMOS差分对和NMOS差分对尾电流管的饱和电压,即电流源两端的电压(这里假设PMOS差分对和NMOS差分对尾电流相等)。

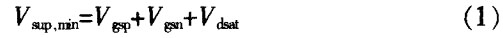

但是将PMOS差分对和NMOS差分对简单地并联构成轨对轨的输入电路,该电路并不能很好地工作。将该输入电路工作状态根据共模输人电压的不同简单分成3个区域,假设K=1/2·Kn·(W/L)n=1/2·Kp·(W/L)p;而且两个PMOS差分对和NMOS差分对尾电流相等,即PMOS差分对尾电流Ip和NMOS差分对尾电流Ip相等,In=Ip=I,则:

式中,gmn脚为NMOS差分对的跨导;gmp为PMOS差分对的跨导。

区域I:当共模输入电压接近于电源电压VDD时,NMOS差分对处于放大工作状态,PMOS差分对处于截止状态,则输入电路的跨导为gm。

区域Ⅱ:当共模输入电压接近于电源电压Gnd时,PMOS差分对处于放大工作状态,NMOS差分对处于截止状态,则输入电路的跨导为gmn。

区域Ⅲ:当共模输入电压处于电源电压的一半时,PMOS和NMOS差分对同时处于放大工作状态,则输入电路的跨导为gmn+gmp=2gmn。

所以,在整个轨对轨的共模输入电压范围内,运放的输入电路的跨导的最大值是其最小值的二倍。由于输入电路的跨导的不同,会导致在共模输入电压范围内运算放大器的增益不同,在相同输入信号频率下相频的反应也会不同,所以输出信号在不同的共模输入电压下产生失真,对于整个电路的相位补偿会相当困难,并且有可能导致运算放大器工作的不稳定。

根据已有文献,可以采用较好地解决该问题的方法如下:

(1)PMOS和NMOS差分对工作于亚阈区,采用控制电路控制NMOS差分对尾电流和PMOS差分对尾电流之和为常数。

(2)采用平方根电路控制NMOS差分对尾电流的平方根值与PMOS差分对尾电流的平方根值之和为常数。

(3)采用尾电流开关控制电路控制PMOS和NMOS差分对尾电流。

(4)采用齐纳二极管,用来保持Vgsn+|Vgsp|为常数。

(5)采用电平移动电路来改变输入差分电路的输入电平。

不种方法具有不同的优缺点.文中的运算放大器输入电路采用的是第三种方法。

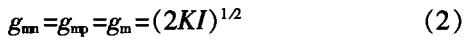

输入差分对管尾电流控制式轨对轨运算放大器如图2所示。从前面的分析可知,当输入共模电压为中间值时的输入差分电路的跨导,为其输入共模电压在共模输入范围的最大值或最小值时的输入差分电路跨导的两倍,即gmn+gmp=2gmn=2·(2KI)。所以,只要使两个差分对单独工作时的尾电流为其同时工作时的尾电流的4倍,就能保证共模输入电压在轨对轨的共模输入范围内输入级的跨导稳定。

图2 输入差分对管尾电流控制式轨对轨运算放大器

如图2所示。电路包含两个分别由开关管控制的放大倍数为1:3的电流镜M13~M14,M8~M7。在输入共模电压在很低范围内时,输入级N管差分对截止,电流开关M15闭和,NMOS对管的尾电流被M15引到由M13和M14组成的1:3的电流镜,从而使PMOS管差分对的尾电流等于原来的4倍。同理,在输入共模电压在接近电源电压VDD范围内时,P管差分对截止,通过开关管控制的1:3的电流镜。N管差分对的尾电流为原来的4倍。在输入共模电压处于中间范围内,两对差分对管同时导通,控制开关M15和M14都断开,两对开关控制的电流镜都不工作,因此实现了在轨对轨的输入共模范围内,输入级的跨导基本相同。

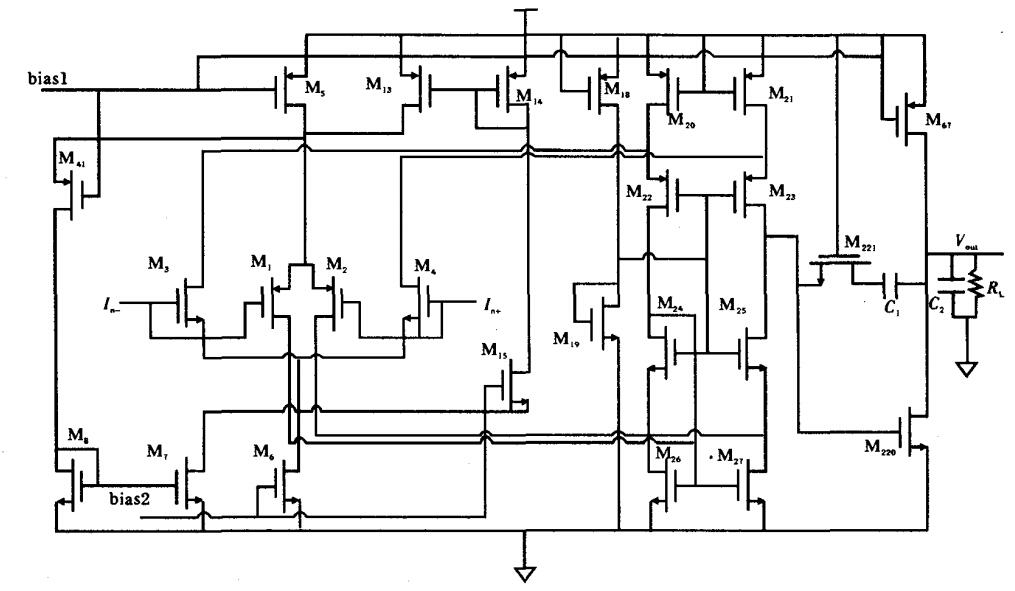

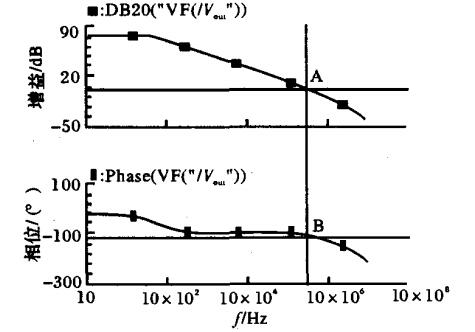

采用Cadence Spectre工具对输入差分对管尾电流控制式轨对轨运算放大器进行仿真分析,所得到的频率响应特性曲线如图3所示。

图3 频率响应特性曲线

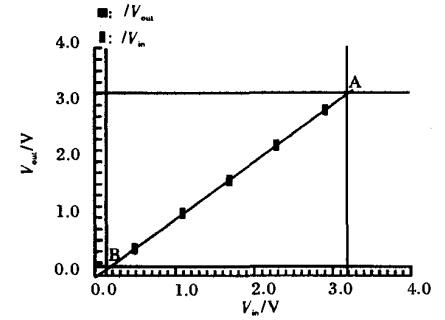

图4 单位增益传输特性曲线

图3表明,该运放在电源电压3.3V.输入共模电压为1.65V,负载电阻100kΩ,负载电容5pF时,其低频增益为77dB,单位增益带宽为4.32MHz,相位裕度为79°。静态功耗为 1.4mW。 图4为该运算放大器的单位增益传输特性曲线,该测试是将运放接成电压跟随器的方式 ,通过输入端 的DC扫描 ,测量运放的单位增益响应。从图4可得到,运放的输入输出的线性度基本达到了轨对轨的电压范围。另外 。通过对该运放的瞬态分析得到,运放的正负转换率分别为SR+=3.624V/μs,SR-=3.63V/μs。

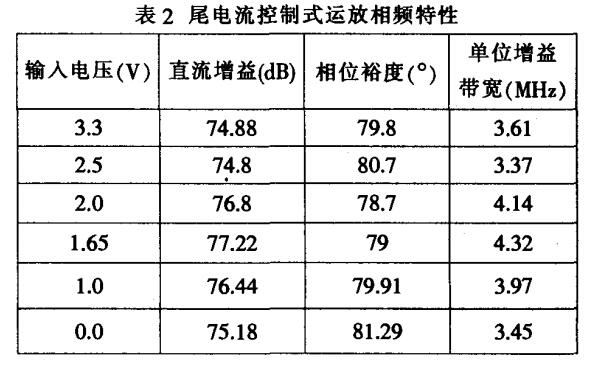

该运放的性能参数分别如表1所示,表2所示为在不同的输入电压下,运放的小信号放大倍数。

其小信号增益最大误差为2.34dB.相位裕度最大误差为2.59°,单位增益带宽最大误差为0.87MHz。

以上就是基于轨对轨CMOS运算放大器的设计的介绍。该运放具有结构简单,低功耗,高增益和较好的输入、输出轨对轨特性。该放大器包括输入级采用带有跨导控制电路的互补差分对结构.输入级的输出采用折叠式宽摆幅共源共栅求和电路.输出级采用具有相位补偿的PMOS为负载的共源级电路。从仿真结果表明,尾电流控制式轨对轨运放从性能结构上非常适用于低压低功耗应用。