目录

| 1.以太网模块 |

| 2.USB主机控制器模块 |

| 3.SDRAM模块 |

| 4. UART(通用异步收发器)模块 |

| 小结 |

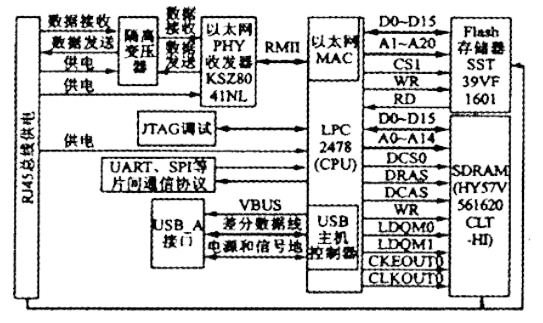

常见ARM7是一种典型的用于嵌入式系统的嵌入式处理器,是应用非常广泛的一种处理器内核。本文以ARM7为内核的微控制器LPC2478为核心,研制了一款可用于科研开发和教学的实验开发板。结构如图1所示。LPC2478控制器的内核为ARM7TDMI-S,包括1个10/100以太网媒体访问控制器(MAC)、1个带4KB终端RAM的

USB全速设备/主机/OTG控制器、4个 UART、2路控制器局域网(CAN)通道、1个

SPI接口、2个同步串行端口(SSP)、3个12C接口和1个12S接口。同时还带有1个片内4MHz内部振荡器、98kB

RAM(包括64kB局部SRAM、16kB以太网SRAM、16kB通用DMASRAM 和2kB电池供电

SRAM)以及1个外部存储器控制器(EMC)来支持各种串行通信接口。

除此以外,还有许多串行通信控制器、多用途的时钟功能和存储器特性,包括有不同的32位定时器、增强型的10位ADC、10位DAC、2个PWM单元、4个外部中断管脚和多达160个高速GPIO。LPC2478连接64个GPIO管脚到基于硬件的向量中断控制器(VIC)。所有的这些特性使 LPC2478特别适用于工业控制和医疗系统。

图1 开发板结构图

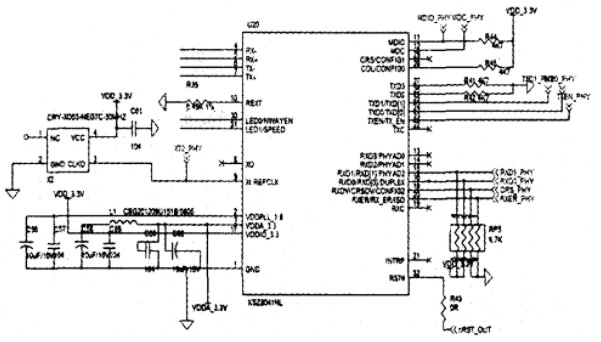

开发板采用的以太网PHY芯片型号是KSZ8041NL。该芯片以太网模块能够通过MII或RMI接口连接的片外PHY发送和接收以太网包。MII或RMII模式可通过软件来选择。通常,在系统启动过程中将对以太网模块进行初始化。以太网模块的软件初始化应包括描述符数组、状态数组以及接收片段缓冲区的初始化。在发送一个包时,软件驱动程序必须建立适当的控制寄存器和一个发送描述符,以便在将信息发送给硬件之前,通过将 TxProducelndex(发送索引)寄存器加1来指向发送包的数据缓冲区。在发送完成之后,硬件将 TxConsumelndex(发送索引)加1,并可选择产生中断。硬件将从PHY 中接收信息包并使用由软件驱动程序配置的滤波机制。在接收一个包时,硬件将从存储器中读取描述符,以找到对应的接收器数据缓冲区的位置。接收数据将被写入到数据缓冲区中,接收状态在接收描述符的状态字中返回。可选择产生中断向软件告知信息包已接收完成。以太网模块电路如图2所示。

图2 以太网模块电路图

在程序设计中,复位后,以太网软件驱动程序需对以太网模块进行初始化。在初始化过程中,软件需完成:

(1)将软件复位条件从MAC中移除;

(2)通过MAC的MIIM接口配置PHY;

(3)选择RMII或MII模式;

(4)配置发送和接收DMA引擎,包括描述符数组;

(5)配置MAC中的主机寄存器(MAC1.MAC2等等);

(6)使能接收和发送数据通道。

寄存器参数配置如下:

MAC_MAC1 = oxCFO0;MAC_COMMAND =Ox0038;MAC_MAC1 = Ox0;

MAC_MAC2 = ox00;MAC_IPGR = Ox0012;MAC_CLRT = Ox370F;

MAC_MAXF = Ox0600; MAC_MCFG =Ox0018;MAC_COMMAND = Ox0240;

MAC_SUPP = ox0000;

USB主机控制器通用串行总线(USB)为4线总线,支持一个主机与一个或多个外设(高达127个)之间的通信。主控制器通过一个基于令牌的协议为连接的设备分配USB带宽。USB总线支持设备的热插拔与动态配置。主控制器启动所有的事务处理。主机将事务安排在1ms的帧中。每帧都包含一个帧开始(SOF)标记和与设备端点进行往返数据传输的事务。每一个设备最多可以具有16个逻辑端点或32个物理端点。针对端点定义了4种传输类型。控制传输可用来对设备进行配置。中断传输则用于周期数据传输。批量传输在对传输速率没有严格要求时使用。同步传输保证了传输时间,但没有纠错功能。LPC2478的USB设备控制器使能与USB主控制器之间的全速(12Mb/s)数据交换。

USB总线处理在设备端点和主机之间传输数据。处理的方向由主机一方定义。OUT处理是指从主机传输数据到设备。IN处理是指从设备传输数据到主机。所有处理都由主控制器启动。对于OUT处理,USB ATX接收USB总线的双向D+和D-信号。串行接口引擎(SIE)从 ATX中接收串行数据并将它转换为并行数据流。并行数据写入EP_RAM的对应的端点缓冲区中。对于IN处理,SIE从EP_RAM的端点缓冲区中读取并行数据,将它转换为串行数据,并使用USB ATX将它传输到USB总线上。一旦数据接收或发送完成,我们就可以对端点缓冲区进行读和写操作。这一点该如何实现由端点的类型和工作模式决定。每个端点有两种工作模式:从(CPU 控制的)模式和 DMA模式。

本开发板采用 HY57V561620SDRAM芯片。HY57V561620数据位宽为16位(16根数据线);12根地址线(行地址选择线有12根,列地址选择线有8根(12根的低8根)),2根bank选择线,总共有22根有效地址线。

初始化 SDRAM控制器的寄存器代码如下:

EMCDynamicReadConfig =1;

EMCDynamicRASCASO = Ox00000303;

EMCDynamicConfig0 = Ox00000680;

EMCDynamicControl = 0x00000183;

EMCDynamicControl = Ox00000103;

EMCDynamicRefresh = 0x00000002;

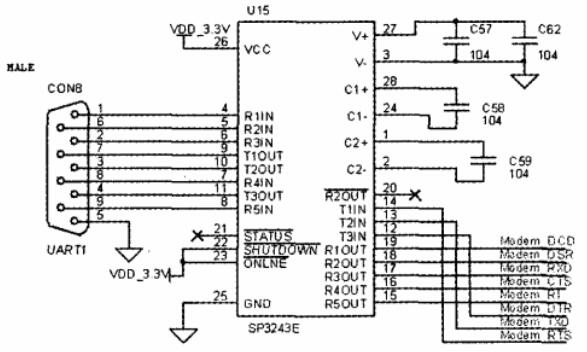

开发板控制器中包含四个通用异步收发器,每个收发器都包含16字节接收和发送 FIFO;内置波特率发生器;用于控制波特率的小数分频器,并拥有赖以实现软件流控制的自动波特率(auto-baud)检测能力和机制;另外,UART3还包含一种支持红外通信的 IrDA模式。其中UART1增加了—个调制解调器(Modem)接口,包含标准调制解调器接口信号(CTS,DCD,DTS,DTR, RI,RTS)。

UART1 的工作原理为:APB接口提供 CPU或主机与 UART1之间的通信连接。UART1接收器模块U1RX 监视串行输入线 RXD1的有效输入。UART1 RX移位寄存器(U1RSR)通过RXD1接收有效的字符。当U1RSR接收到一个有效字符时,它将该字符传送到UART1 RX 缓冲寄存器 FIFO中,等待 CPU 或主机通过主机接口进行访问。UART1发送器模块U1Tx接收 CPU或主机写入的数据并缓冲存放在UART1 TX保持寄存器Fl-FO(U1THR)中的数据。UART1 TX移位寄存器(U1TSR)读取U1THR中的数据并将这些数据通过串行输出管脚 TXD1发送。UART1波特率发生器模块 U1BRG产生供 UART1 TX模块使用的定时使能信号。

UIBRG模块的时钟输人源为 APB时钟(PCLK)。主时钟与UIDLL和U1DLM寄存器所定义的除数相除得到 UART1TX模块使用的时钟。Modem接口包含寄存器U1MCR 和UIMSR。该接口负责 Modem 外设和UART1之间的信号交换(handshaking)。中断接口包含寄存器U1IER和 U1IIR。中断接口接收几个来自U1TX和U1RX 模块的单时钟宽度的使能信号。UITX 和U1RX 的状态信息保存在U1LSR 中。UITX和U1RX的控制信息保存在U1LCR 中。它还包含一种使能实现软件流和硬件流控制的机制。UART1的工作外部接线图如图3所示。

图3 UART1接线图

以上就是基于ARM7内核设计的开发板介绍了。本设计的开发板能满足各种功能程序测试的开发设计,可以使得科研人员或者学生根据测试例程,编写自己的程序,以板为平台,开发各种控制器,满足通信、控制、显示等各种需要。