MCIMX508CVM8B 点击型号即可查看芯片规格书

产品型号 | MCIMX508CVM8B |

描述 | 集成电路MPU I.MX50 800MHZ 400MAPBGA |

分类 | 集成电路(IC),嵌入式-微处理器 |

制造商 | 恩智浦半导体 |

系列 | i.MX50 |

打包 | 托盘 |

零件状态 | 活性 |

工作温度 | 0°C〜70°C(TA) |

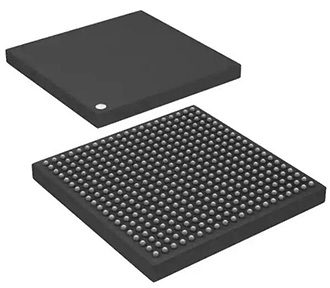

包装/箱 | 400-LFBGA |

供应商设备包装 | 400-MAPBGA(17x17) |

基本零件号 | MCIMX50 |

MCIMX508CVM8B

制造商包装说明 | 17 X 17 MM,0.5 MM间距,符合RoHS标准,塑料,MABGA-400 |

符合REACH | 是 |

符合欧盟RoHS | 是 |

状态 | 活性 |

边界扫描 | 是 |

核心处理器 | ARM®Cortex®-A8 |

最大时钟频率 | 800.0兆赫 |

JESD-30代码 | S-PBGA-B400 |

JESD-609代码 | e1 |

端子数 | 400 |

最低工作温度 | 0℃ |

最高工作温度 | 70℃ |

包装主体材料 | 塑料/环氧树脂 |

包装代码 | LFBGA |

包装等效代码 | BGA400、20X20、32 |

包装形状 | 四方形 |

包装形式 | 网格状,低轮廓,精细间距 |

峰值回流温度(℃) | 260 |

RAM(字) | 131072 |

座高 | 1.6毫米 |

最大电源电流 | 628.0毫安 |

电源电压标称 | 1.225伏 |

最小供电电压 | 1.175伏 |

最大电源电压 | 1.275伏 |

表面贴装 | 是 |

技术 | CMOS |

温度等级 | 商业类 |

终端完成 | 锡/银/铜(Sn / Ag / Cu) |

终端表格 | 球 |

端子间距 | 0.8毫米 |

终端位置 | 底部 |

时间@峰值回流温度-最大(秒) | 40 |

长度 | 17.0毫米 |

宽度 | 17.0毫米 |

RoHS状态 | 符合ROHS3 |

水分敏感性水平(MSL) | 3(168小时) |

●MMU,L1指令缓存和L1数据缓存

●统一的二级缓存

●内核的800MHz或1GHz目标频率(包括NEON,VFPv3和L1缓存)

●支持VFPv3的NEON协处理器(SIMD媒体处理体系结构)和矢量浮点(VFP-Lite)协处理器内存系统由以下组件组成:

●1级缓存:

指令(32KB)

数据(32KB)

●2级缓存:

统一的指令和数据(256KB)

●2级(内部)内存:

引导ROM,包括HAB(96KB)

内部多媒体/共享的快速访问RAM(128KB)

●外部存储器接口:

16/32位DDR2-533,LPDDR2-533或LPDDR1-400,总计2GB

8位NAND SLC/MLC闪存,具有高达100MHz的同步时钟速率和高达32位的硬件ECC(块大小为1KB)

具有专用16位多路复用模式接口的16/32位NOR闪存。I/O复用逻辑在系统引导时选择EIMv2端口作为主要复用。

16位PSRAM,蜂窝RAM

受管理的NAND,包括4.4版之前的eMMCi.MX50引入了下一代系统总线架构体系结构,该体系结构聚合了各种子系统总线和主控器,以访问系统外围设备和内存。

●各种总线系统和组件如下:

●64位AXI架构(266MHz)

该总线结构是SoC的中央总线聚合点。

提供对SoC中所有从设备目标的访问:

ROM(ROMCP)

片上RAM(OCRAM)

外部DRAM(DRAMMC)

外部静态RAM(EIM)

中断控制器(TZIC)

解码到AHBMAX交叉开关第二级AHB结构中。

向系统中的以下主机提供仲裁:

ARM CPU复合体

像素处理管线(ePXP)

电泳显示控制器(EPDC)

eLCDIF LCD显示控制器

DCP加密引擎

BCH ECC引擎

MAX AHB横杆

GPU 2D

SDMA

USBOH1(USBOTG和主机控制器复合体)

FEC以太网控制器

●MAXAHB交叉开关(133MHz)

这将连接系统中的各个AHB总线子段,并提供解码为以下从站:

IP总线1(66MHz)

该总线段包含可由ARM内核访问且不具有DMA功能的外围设备

IP总线2(66MHz)

该总线段包含可由ARM内核访问且不具有DMA功能的外围设备

APBHDMA桥(133MHz)

APBHDMA桥是MAX的主存储器,用于其存储器侧DMA操作。APBH总线是AMBAAPB从总线,可通过外围设备访问i.MX50上的许多高速IP模块

●IP总线3(66MHz)

该第三外围总线网段包含可由ARM内核和SDMA访问的外围设备,因此容纳了具有DMA功能的外围设备。ARMCPU可以通过IP总线1和SPBA访问IP总线3。

●服务质量控制器(QoSC)

这提供了软性和动态仲裁/优先级控制。QoSC与关键的显示模块(例如eLCDIF和EPDC)协同工作,可基于实时指标提供动态优先级控制。i.MX50利用专用的硬件加速器来实现最新的多媒体性能。硬件加速器的使用可提供高性能和低功耗,同时将CPU内核释放给其他任务。i.MX50包含以下硬件加速器:

●GPU2Dv1

2D图形加速器,OpenVG1.1、200Mpix/s的性能

恩智浦半导体(英语:NXP Semiconductors),前身为飞利浦半导体,由荷兰企业飞利浦在1953年创立,公司总部位于荷兰埃因霍温。恩智浦的产品技术与解决方案应用于以下五个市场领域:汽车电子、智能识别、家庭娱乐、手机及个人移动通信以及多重市场半导体,进而建立各大市场中的领导地位。 四十家直接大客户营业额贡献率约为50%。 主要客户包括:苹果、博世、大陆、 德菲尔、爱立信、诺基亚、诺基亚西门子网络、松下、飞利浦和三星。