MAX9632 ; MAX2880 点击型号即可查看芯片规格书

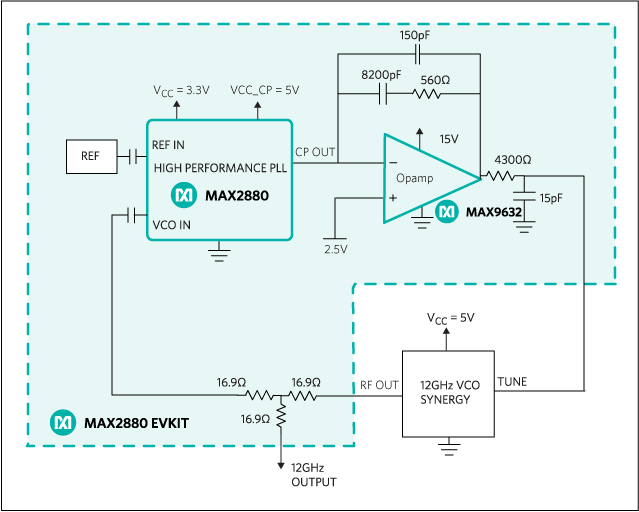

图1所示、基于MAX2880的12GHz超低相位噪声分数n锁相环

主要特点:

超低相位噪声:92飞秒RMS抖动(1kHz-20MHz)

不需要外部分频器

有源滤波器与调谐范围从0.5V到15V

这种高性能锁相环可用于产生混频器本振(LO)频率或ADC/DAC时钟,适用于微波点对点系统、测试和测量设备或汽车雷达。

相位噪声性能数据和详细的设置指南包括在这个应用程序说明。

锁相环总相位噪声通常由锁相环带内相位底噪声和压控振荡器相位噪声决定。为了构建超低相位噪声的锁相环,设计人员需要选择低相位噪声的压控振荡器和锁相环。MAX2880能够实现带内相位本底噪声,整数模式为-229dBc/Hz,分数低噪声模式为-225dBc/Hz。

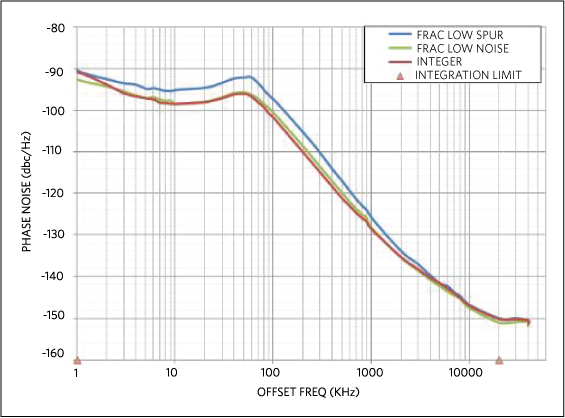

表1和图2给出了该电路在12GHz和MAX2880不同模式下的相位噪声性能。

| 参数 | 结果 | 单位 |

| 载波频率 | 12 | GHz |

| RMS抖动(整数模式) | 89 | 飞秒 |

| RMS抖动(分数低噪声模式) | 92 | 飞秒 |

| RMS抖动(分数低杂散模式) | 140 | 飞秒 |

| 集成相位噪声(整数模式) | -46.7 | dBc |

| 集成相位噪声(分数低噪声模式) | -46.2 | dBc |

| 综合相位噪声(分数阶低杂散模式) | -42.7 | dBc |

| 集成限制 | 1 - 20000 | 千赫 |

| VCO调谐范围 | -15 - 0.5 | V |

图2、12GHz相位噪声图

该设计需要MAX2880评估套件(EV套件)和12GHz外部VCO (Synergy DXO11751220-5)。

注意:MAX2880 EV套件中不包括Synergy VCO,需要对EV套件进行一些修改。

验证默认的MAX2880功能。请按照MAX2880 EV套件数据表了解详细的操作程序。

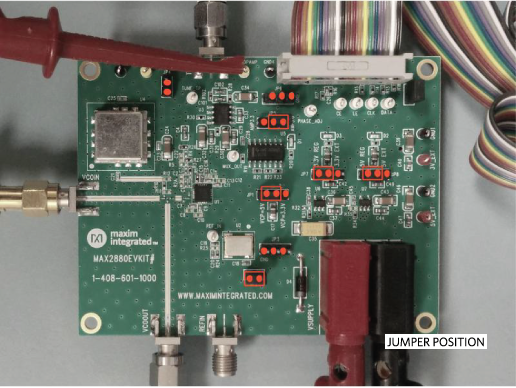

根据表2修改MAX2880 EV套件,并根据图3更改跳线位置。

| 部分(单位) | 改变 | 默认的 | 请注意 |

| C1 (nF) | 开放 | 10 | 去除无源滤波器 |

| R2A(欧姆) | 开放 | One hundred. | 去除无源滤波器 |

| C2 (nF) | 开放 | One hundred. | 去除无源滤波器 |

| R3(欧姆) | 开放 | 47.5 | 去除无源滤波器 |

| C3 (nF) | 开放 | 1 | 去除无源滤波器 |

| R4(欧姆) | 开放 | 0 | 去除无源滤波器 |

| R27(欧姆) | 0 | 开放 | 连接有源滤波器 |

| R26(欧姆) | 4300 | 开放 | 有源滤波器 |

| C4 (pF) | 15 | 开放 | 有源滤波器 |

| C101 (pF) | 150 | 开放 | 有源滤波器 |

| R102(欧姆) | 560 | 开放 | 有源滤波器 |

| C102 (pF) | 8200 | 开放 | 有源滤波器 |

| R9机型(欧姆) | 开放 | 16.9 | 断开板载VCO |

| R9到NC1 | 16.9 | 开放 | 连接外部VCO |

| JP4 2针跳线 | 开放 | 连接 | 下电板载VCO |

| JP5 3针跳线 | 连接中心引脚至5P0_V(CC) | 开放 | 电流输入+偏置 |

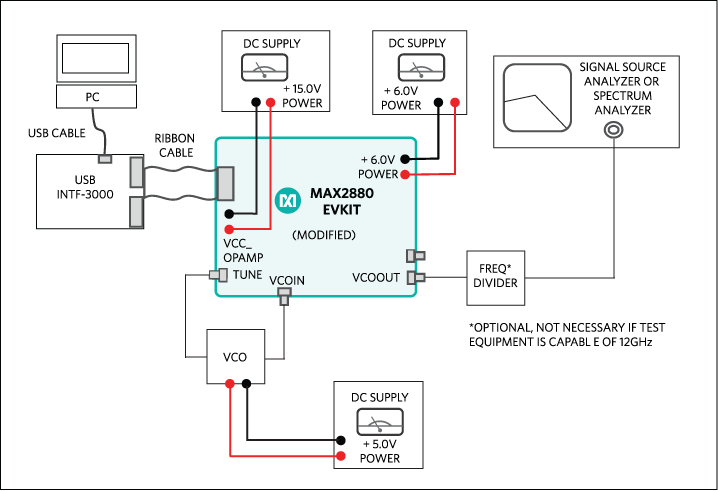

根据图4连接到EV套件。确保所有电源都处于关闭状态。

将VCO上电至+5V。

用+15V和+6V上电MAX2870 EV套件。

将MAX2880寄存器编程为所需模式:

整数低噪声模式:003C0000、06000001、6F00CE22、00002503、00000004、00000005

分数阶低噪声模式:003C0000、06000001、0F00FFFA、00000303、00000004、00000005

分数阶Low-Spur模式:003C00C8、06000001、6F00CE22、00000B03、00000004、00000005

图3、跳线的位置

图4、详细设置图