TXB0104 点击型号查看芯片规格书

Texas Instruments(德州仪器) 芯片规格书大全

作者: Sales and Marketing/Shenzhen China——Zoe Yang

Abstract

TXB0104是应用在AM3352(Sitara MCU/MPU等)和EMMC (嵌入式多媒体存储卡)芯片之间通信的双向自动检测电平转换芯片。当系统的软件资源配置不足,需要电平转换芯片自己识别信号传输方向的时候,需要注意外部硬件设计,不然可能会出现挂载时好时坏的失效情况。

问题背景:

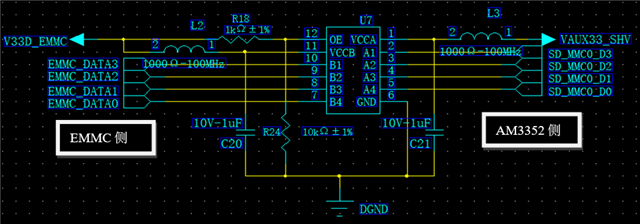

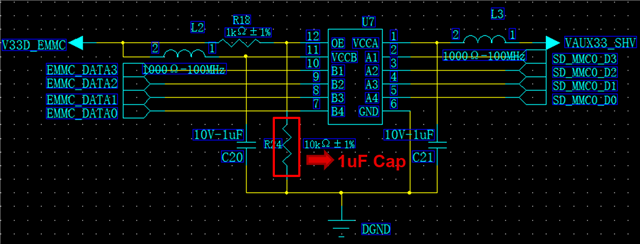

EMMC与AM3352挂载失败,定位为TXB0104工作异常。实测中发现如图中线路所示:

只有D0通道无信号,因为将D0数据线由主芯片(AM3352)侧飞线到EMMC,D0开始传输数据信号,eMMC挂载正常(该情况下在AM3352侧也能测到D1/2/3的数据波形);

将D0飞线跨过该转换芯片,同时断开D2(在转换芯片与eMMC之间),挂载失败;——综合1、2,说明D2在挂载的时候需要使用到,同时在双向电平转换芯片中D2通道正常;

将D0和D2数据线在U7中对应的电平转换通道中交叉焊接,测试D0无信号(D0无信号的时候D1/2/3也无波形),eMMC挂载失败;

将D0飞线跨过该转换芯片,同时将D2数据线连接U7的D0通道,可以正常挂载上;——双向电平转换芯片中D0通道正常,但连接上D0数据后异常;

图1.异常板子的电路图

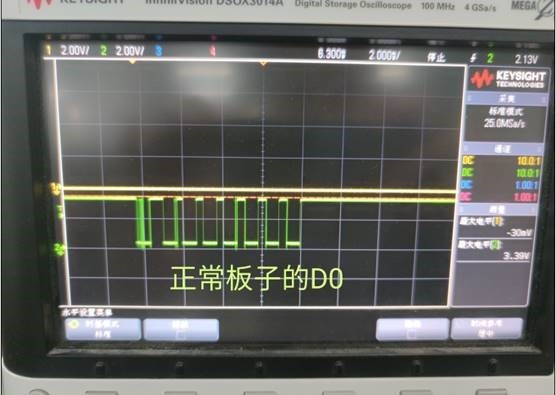

挂载时好时坏的板子分别在正常时、异常时的D0信号波形如下

图2.正常(上)和异常(下)挂载的板子传输信号D0通道波形

问题聚焦:

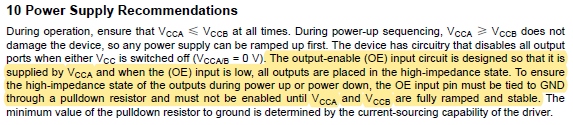

检查线路图后发现, OE上拉到3.3VCCB。规格书明确指出,针对在上电过程中,OE在电源稳定之前必须保持低电平。

图3.规格书中声明OE的上电时序

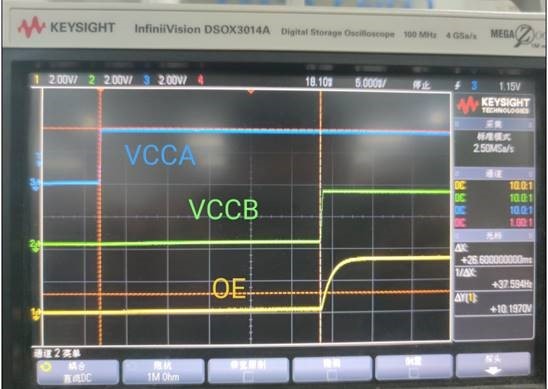

现同时通过原始电阻分压采样VCCB上电时序和OE的管脚波形,发现OE与VCCB同时上电。

图4. 原始电阻分压时序展开:OE与VCCB同时上电

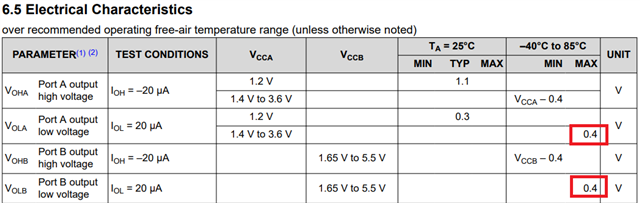

VOLB识别低电平的状态在3.3V供电状态最高为0.4V,因此要延长VOE保持低电平的时间,让IC保证识别到低电平状态。

图5.高低电平阈值比较

整改方案:

为了能保证OE在上电期间保持足够的低电平,建议将R24电阻替换成1uF的电容。利用电容替代电阻的方法可以适当增加RC时间常数来稳定OE保持低电平的时间。

图6.原始电路基础上的整改方案

重新通过原始电阻分压采样VCCB上电时序和OE的管脚波形,发现换成1uF电容电压时序展开(t=1/RC),在VCCB稳定后OE保持低电平(<0.35VCCB)的时间约为320us,挂载异常不再复现。

图7.enable建议时间

图8.VCC与OE爬升时间拉长

分析总结:

经过测试分析,延长OE的低电平时间可以有效地避免MCU和EMMC芯片握手失败。

这种导致芯片传输挂机失败的原因是由于TXB0104在上电期间的传输口是不定态所致。

如果TXB0104的OE脚没被拉低,则在上电期间传输口A,B会处于不定态(低电平,高电平或高阻态),此时要求和传输口A,B相连的EMMC和MCU相应I/O口此刻应保持确定的高阻态,以确保上电期间EMMC和MCU的I/O口不会被短路。 如果TXB0104的OE脚在上电期间被拉低(将对地电阻换成电容),则传输口A,B是处于确定的高阻态,对相连的EMMC和MCU的I/O没有影响,信号就能正常传输。

所以在OE端口挂电容能保证上电期间传输口确定的高阻态,故障因此得以消除。

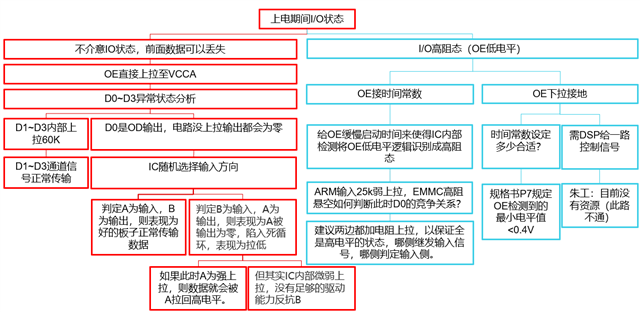

为了简化用户系统的设计分析,下面通过一个流程图来梳理TXB0104的I/O口各个状态对应系统的应用可能,避免类似的不定态传输导致信号判断失误。

图9.I/O端口状态流程图