国产互连类芯片—澜起科技

电子技术

2024-07-09 11:00

1748

0

上周六(7月6号)澜起发布了一则业绩预测公告,公告中提到互联类芯片季度收入创历史新高,主要原因是:

2,受益于AI产业浪潮,澜起的三款高性能"运力"芯片新产品呈快速成长态势。

1)PCIe Retimer芯片:受益于全球AI服务器需求旺盛,澜起PCIe Retimer芯片出货量快速增长,24年Q1出货15万颗,24年Q2 出货约30万颗。

2)MRCD和MDB芯片:受益于AI及高性能计算对更高带宽内存模组需求的推动,搭配澜起MRCD和MDB芯片的服务器带宽内存模组开始在境内外主流云计算/互联网厂商规模使用,24年Q1销售额超过2000万,24年Q2销售额超过5000万人民币。

3)CKD芯片:24年4年在业界率先试用,24年Q2开始规模出货,单季度销售额超过1000万人民币。

内存接口芯片是服务器内存模组的核心逻辑器件,位于CPU和DRAM内存颗粒通路之间。由于CPU主频频率(GHz 级)远大于内存颗粒核心频率(MHz级),内存读取数据速度远小于CPU计算速度,因此需要内存接口芯片缓冲来提升数据访问速度及稳定性。

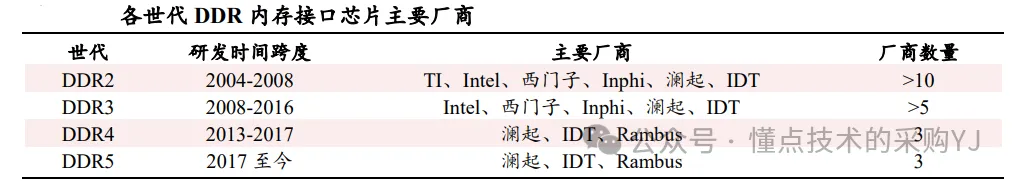

内存接口芯片认证、技术壁垒高,行业格局高度集中。自DDR4开始,行业主要参与者仅剩澜起、瑞萨(IDT)、Rambus三家。

现阶段DDR4及DDR5内存接口芯片按功能可以分为两类,即寄存缓冲器(RCD)和数据缓冲器(DB)。

澜起的DDR4产品在2013年10月获得 Intel认证,并发明了“1+9” 分布式缓冲内存子系统框架,被JEDEC采纳为国际标准。

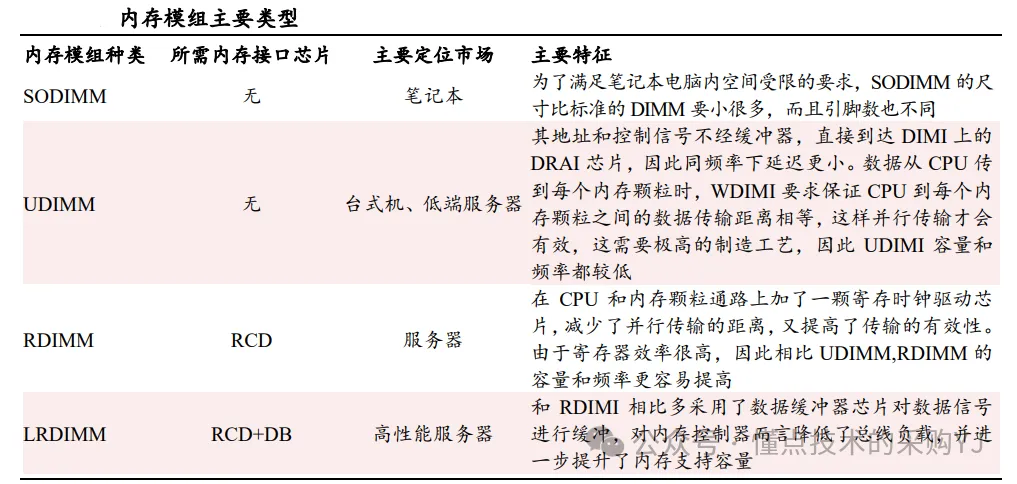

1、服务器内存模组,其主要类型为 RDIMM、LRDIMM

2、普通台式机、笔记本内存模组,其主要类型为UDIMM、SODIMM。

RDIMM仅采用了一颗RCD芯片,而LRDIMM采用了RCD和DB套片组合,在DDR4是“1+9” 架构即1颗RCD和9颗DB 芯片,在DDR5则演变成“1+10”架构。

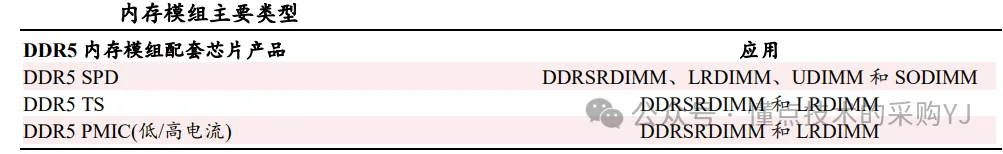

根据JEDEC标准,DDR5内存模组上除了内存颗粒及内存接口芯片外,还需要三种配套芯片,分别是串行检测集线器(SPD)、温度传感器(TS)以及电源管理芯片(PMIC)。

澜起内存模组配套芯片是与合作伙伴(聚辰??)共同研发,具体如下:

PCIeRetimer芯片是适用于PCIe高速数据传输协议的超高速时序整合芯片。在PCIe 4.0及更早版本之前,数据传输速率相对较低,对信号完整性的要求不高,Retimer芯片并非刚需,而进入PCIe5.0 时代,信号衰减和抖动问题开始突出,在服务器中 GPU与CPU连接时至少需要一颗Retimer芯片来保证信号质量。

目前Astera Labs、谱瑞-KY、澜起科技是PCIe Retimer市场中的三家主要厂商。

Astera Labs最先推出并量 产 PCIe 5.0 Retimer,其Aries产品线现已发展到第二代,包括支持PCIe 4.0、 PCIe 5.0和 CXL1.1的多款产品;

澜起科技是全球可量产PCIe 5.0 Retimer(兼容PCIe和CXL两种工作模式)的唯一中国大陆供应商。

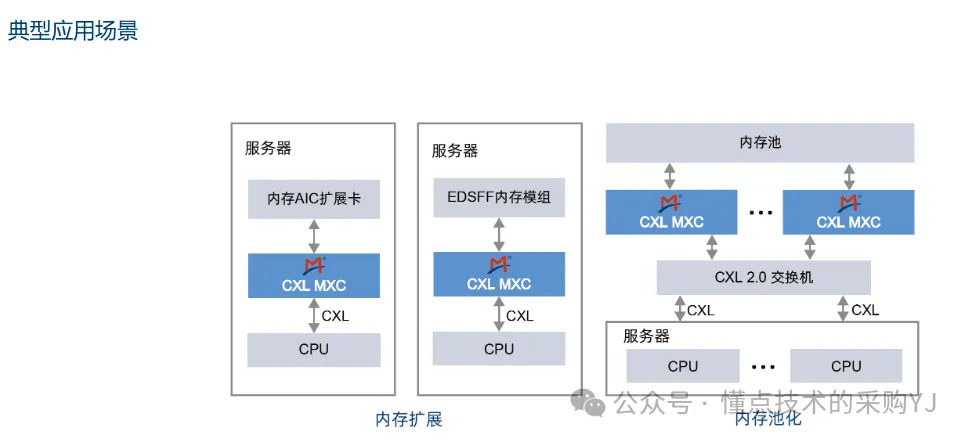

MXC芯片用于为CPU及基于CXL协议的设备提供高速互连解决方案,实现CPU与各CXL设备之间的内存共享。

官网看目前只有一个型号:M88MX5891,支持JEDEC DDR4和DDR5,最高支持速率:DDR4-3200/DDR5-5600,同时也符合CXL(®) 2.0规范,支持PCIe(®) 5.0的速率。

时钟驱动器芯片(CKD),用于缓冲来自台式机和笔记本电脑中央处理器的高速内存时钟信号,并将之输出驱动到UDIMM、SODIMM模组上的多个DRAM内存颗粒。

时钟驱动功能集成于寄存时钟驱动器(Register Clock Driver)芯片,在服务器RDIMM或LRDIMM模组上面使用,并未用到PC端。

随着DDR5传输速率持续提升,时钟信号频率越来越高,时钟信号的完整性问题变得日益突出。当 DDR5 数据速率达到6400MT/s 及以上时,PC端内存如台式机及笔记本电脑的UDIMM、SODIMM模组,须采用一颗专用的时钟驱动芯片(CKD芯片)来对内存模组上的时钟信号进行缓冲再驱动,才能满足高速时钟信号的完整性和可靠性要求。

2022年9月,澜起发布业界首款DDR5第一子代时钟驱动器(CKD)工程样片,并已送样给业界主流内存厂商,24年Q2已开始批量出货。

转自-懂点技术的采购YJ

数据源于网络,错改,侵删!

登录icspec成功后,会自动跳转查看全文