5CEFA9F27I7N 点击型号即可查看芯片规格书

产品型号 | 5CEFA9F27I7N |

描述 | 集成电路FPGA 336 I/O 672FBGA |

分类 | 集成电路(IC),嵌入式-FPGA(现场可编程门阵列) |

制造商 | 英特尔 |

系列 | Cyclone®VE |

打包 | 托盘 |

零件状态 | 活性 |

电压-电源 | 1.07V〜1.13V |

工作温度 | -40°C〜100°C(TJ) |

包装/箱 | 672-BGA |

供应商设备包装 | 672-FBGA(27x27) |

基本零件号 | 5CEFA9 |

5CEFA9F27I7N

可编程逻辑类型 | 现场可编程门阵列 |

符合REACH | 是 |

符合欧盟RoHS | 是 |

状态 | 转移 |

最大时钟频率 | 622.0兆赫 |

JESD-30代码 | S-PBGA-B672 |

JESD-609代码 | 1号 |

总RAM位 | 14251008 |

CLB数量 | 301000.0 |

输入数量 | 336.0 |

端子数 | 672 |

组织 | 301000 CLBS |

峰值回流温度(℃) | 未标明 |

电源 | 1.1,1.2 / 3.3,2.5 |

资格状态 | 不合格 |

座高 | 2.0毫米 |

子类别 | 现场可编程门阵列 |

电源电压标称 | 1.1伏 |

最小供电电压 | 1.07伏 |

最大电源电压 | 1.13伏 |

安装类型 | 表面贴装 |

技术 | CMOS |

终端完成 | 锡银铜 |

终端表格 | 球 |

端子间距 | 1.0毫米 |

终端位置 | 底部 |

时间@峰值回流温度最大值(秒) | 未标明 |

长度 | 27.0毫米 |

宽度 | 27.0毫米 |

包装主体材料 | 塑料/环氧树脂 |

包装代码 | BGA |

包装等效代码 | BGA672,26X26,40 |

包装形状 | 广场 |

包装形式 | 网格阵列 |

制造商包装说明 | 27毫米,符合ROHS标准,FBGA-672 |

无铅状态/RoHS状态 | 无铅/符合RoHS |

水分敏感性水平(MSL) | 3(168小时) |

•技术

。TSMC的28-nm低功耗(28LP)工艺技术

。1.1 V核心电压

•包装

。引线键合低卤素封装

。具有兼容封装尺寸的多种设备密度,可在不同设备密度之间无缝迁移

。符合RoHS和含铅(1)的选项

•高性能FPGA架构

。具有四个寄存器的增强型8输入ALM

•内部存储块

。M10K-带有软纠错码(ECC)的10千(Kb)内存块

。存储器逻辑阵列模块(MLAB)-640位分布式LUTRAM,您可以在其中使用多达25%的ALM作为MLAB存储器

•嵌入式硬IP 模块

。可变精度DSP

—在同一可变精度DSP模块中,本机支持多达三个信号处理精度级别(三个9 x 9,两个18 x 18或一个27 x 27乘法器)

—64位累加器和级联

—嵌入式内部系数存储器

—预加器/减法器,以提高效率

。内存控制器

—具有16位和32位ECC支持的DDR3,DDR2和LPDDR2

。嵌入式收发器I / O

—PCI Express *(PCIe *)Gen2和Gen1(x1,x2或x4)硬IP,具有多功能支持,端点和根端口

•时钟网络

。高达550 MHz的全球时钟网络

。全局,象限和外围时钟网络

。可以关闭未使用的时钟网络以降低动态功耗

•锁相环(PLL)

。精确的时钟合成,时钟延迟补偿和零延迟缓冲(ZDB)

。整数模式和小数模式

•FPGA通用I / O(GPIO)

。875 Mbps的LVDS接收器和840 Mbps的LVDS 发送器

。400 MHz / 800 Mbps外部存储器接口

。片上匹配(OCT)

。3.3 V支持,最高16 mA驱动强度

•低功耗高速串行接口

。614 Mbps至6.144 Gbps集成收发器速度

。传输预加重和接收机均衡

。个别通道的动态部分重新配置

•HPS (仅Cyclone V SE,SX 和ST设备)

。单核或双核Arm Cortex-A9 MPCore处理器-最高频率可达925 MHz,并支持对称和非对称多处理

。接口外围设备-10/100/1000以太网媒体访问控制(EMAC),USB 2.0 On-The-GO(OTG)控制器,四串口外围接口(QSPI)闪存控制器,NAND 闪存控制器,安全数字/多媒体卡(SD / MMC)控制器,UART,控制器局域网(CAN),串行外围设备接口(SPI),I2C接口以及多达85个HPS GPIO 接口

。系统外设-通用定时器,看门狗定时器,直接存储器访问(DMA)控制器,FPGA配置管理器以及时钟和复位管理器

。片上RAM和引导ROM

。HPS-FPGA桥接器-包括FPGA到HPS,HPS到FPGA和轻型HPS到FPGA的桥接器,这些桥接器允许FPGA架构向HPS中的从属发出事务,反之亦然

。FPGA到HPS SDRAM控制器子系统-提供与HPS SDRAM控制器的多端口前端(MPFE)的可配置接口

。Arm CoreSight™JTAG调试访问端口,跟踪端口和片上跟踪存储

•配置

。篡改保护-全面的设计保护,可保护您宝贵的IP投资

。增强的高级加密标准(AES)设计安全功能

。CvP

。FPGA的动态重配置

。有源串行(AS)x1和x4,无源串行(PS),JTAG和快速无源并行(FPP)x8和x16配置选项

。内部擦洗

。部分重新配置

5CEFA9F27I7N符号

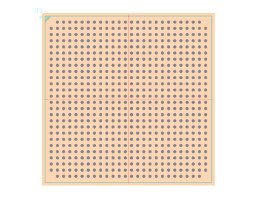

5CEFA9F27I7N脚印

Altera公司(NASDAQ:ALTR),中文名:阿尔特拉。是位于美国硅谷的一家可编程逻辑器件和可反复配置的复杂数字电路的制造企业。Altera结合带有软件工具的可编程逻辑技术、知识产权(IP)和技术服务,在世界范围内为14,000多个客户提供高质量的可编程解决方案。Altera的主要产品为FPGA(分属Stratix、Arria和Cyclone三大系列)、CPLD复杂可编程逻辑设备(MAX系列)和ASIC(HardCopy系列)。此外,公司还推出了名为Quartus II的电子设计自动化工具软件。