资料:Hi3559AV100

随着科技的进步和人们对生活品质的追求,8K 超高清电视正成为研究的热点,本文 8K 智能摄像头搭配 8K 电视形成了家庭 8K 图像采集和图像显示的端到端解决方案,满足了人们对图像采集和显示的极致追求。

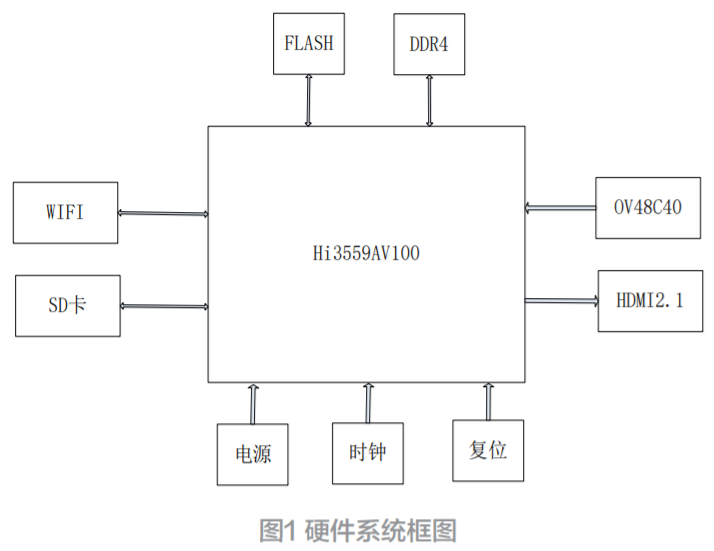

1 硬件系统方案

8K 摄像机主控采用海思 Hi3559AV100,传感器采用豪威 OV48C40,DC-DC 采用 MP1495S,内存采用 MT53B256M32D1-NP,SPI FLASH 采用 MX25U25635F;Wi-Fi 采用 RTL8822CU。硬件系统框图如图 1。

其中,电源给整个系统供电;时钟电路保系统中的各模块同步;复位电路确保主控可靠的工作;DDR 是随机存储器,同步需要时钟;FLASH 用来程序存储;传感器采集数据;HDMI2.1 传输图像数据;Wi-Fi 可以 来无线传输,满足人们无线观看视频需求,但是最大支持 2K;SD 用来存储视频。

Hi3559AV100 是一款 8K(支持最大分辨率为 8 192×8 640)摄像头处理芯片,支持 8K@30 广播级图像质量的数字处理,支持连接多路传感器传感器, 支持原始图像 RAW 数据输出和 H.265 编码,内部集成了超高性能 ISP,采用最先进的低功耗架构和工艺设计。HDMI2.1 接口最大传输速率为 12 Gb/s,可以满足 8K@30 视频传输。

2 电路设计

2.1 电源设计

电源给整个系统供电,电源芯片供电能力大于 2 A,电感值大于 2.2 µH,饱和电流大于 3 A。Hi3559 内核电压 0.8 V,IO 电压 18 V,DDR4 接口电压 1.2 V, LPDDR4 接口电压 1.2 V。内核电源方面,DDR 电源和 IO 电源上电时序为:IO 电源> DDR 电源>内核电源;下电时 IO 先下电,内核最后下电。DDR PLL 电源与 IO 电源连接时,必须使用磁珠隔离,纹波小于 800 mV,不能有固定频点噪声。FLASH 接口的 IO 电源实际连接的时要与对接芯片的接口电平一致。

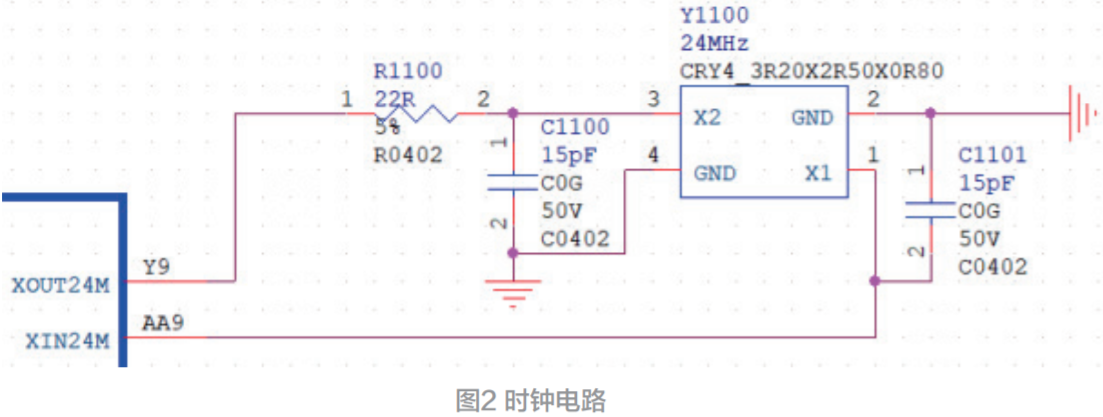

2.2 时钟电路

外部 24 MHz 时钟电路和芯片内部的反馈电路形成了系统时钟电路。外部晶体振荡电路采用 4P 贴片晶振,其中 2 个 GND 要充分接地,增加系统时钟抗 ESD 干扰能力;外围电容采用 NPO,为防止电磁干扰,时钟到主控的输入端串联 22R 的端接电阻。时钟电路如图 2 所示。

2.3 复位电路

系统上电后由主控内部 POR 电路对芯片进行复位,Hi3559 硬件复位通过 RESET 引进来实现,低电平有效,最短复位周期为 100 个 24 MHz 的时钟周期,也就是说至少需要 4 ms。系统复位电平一定要与 FLASH 电平保持一致,否则系统无法启动。

2.4 DDR电路

DDR 电路采用 2×DDR4,数据总线宽度为 32 位,DDR4 传输速率为 3 200 Mbps。DDR4 采用了最先进工艺技术,在提高性能、降低成本同时还降低了功耗。DDR4 引脚由数据线、地址线、控制线、电源和地组成。DDR 按照引脚功能可以分为 7 类:电源、地、配置、控制信号、时钟信号、地址信号、数据信号。DDR4 中最重要的信号就是地址信号和数据信号。DQ[0:31] 是数据信号,DQS_N/DQS_P 是数据选通信号;A[0:16] 是地址选择信号,BA[0:1] 是 Bank 地址选择;CK_N/CK_P 是差分时钟信号;CS_N 是 DDR 片选信号;ODT 是阻抗匹配使能信号。DDR 与主控的信号连接示意图如图 3 所示。

2.5 传感器电路

传感器采用豪威 OV48C40,它是一款 8K(支持最大分辨率为 8 064×6 048)像素,1/1.32 英寸的 CMOS 传感器。支持 DCG HDR 功能,信噪比高。芯片电源供电分三部分:DOVDD、AVDD 和 DVDD,三部分电源滤波电容靠近对应引脚。VREFN、VREFN2、VREFH 以及 TXVDD 和地之间必须接电容,可滤除高频和低频的电源纹波,如果不接电容 8K 视频信号传输不稳定。DOVDD 电压须与主控 Hi3559AV100 的 I/O 电压保持一致。模拟地和数字地用磁珠隔开。

2.6 其它电路

Wi-Fi 通过 USB 接口与主控相连,SD 卡通过 SDIO 接口与主控相连,HDMI2.1 按照 HDMI 接口标准规范与主控相连。

3 PCB设计注意事项

PCB 布局和布线是产品成败的关键,因此 PCB 设计要按照芯片规格书要求逐条核对。如传感器 PCB 布局和布线直接影响摄像头出图,电源、DDR 的 PCB 布局和布线直接影响摄像头启动,Wi-Fi、SD 卡的 PCB 布局和布线直接影响视频信号传输和存储。

3.1 传感器PCB设计

镜头下面尽量不要摆放任何电容电阻,减少对芯片表面脏污;AVDD 布线尽可能远离 EXTCLK、MIPI 信号线,减少电源纹波和噪声对信号的干扰;MIPI 信号差分线阻抗控制在 100 Ω,误差小于 ±10%;避免直角走线带来的信号反射,影响 8K 高速传输性能;信号线下方的参考层必须保证是整片的地层。MIPI 线对要走等长,误差控制在 8 mil(毫英寸);行数据线、时 钟线等至少保持 3 W 以上的距离且绝不能平行走线。 MIPI 信号线尽量不要打过孔,如有过孔则 MIPI 信号线对上的两根线都要有过孔(保持过孔的对称性),信号线换层后参考层也要在靠近信号线的过孔处打孔换层。

3.2 DDR PCB设计

DDR4 地址线布局布线不可使用 T 型,一定要用 Fly-by 的拓扑结构,拓扑过孔到管脚的长度小于 120 mil;VTT 的上拉电阻要放在信号的末端,且走线越短越好,走线长度不能大于 400 mil;VTT 信号端要放一个滤波电容。主控和 DDR4 颗粒端的每个引脚放一个滤波电容,且滤波电容尽可能靠近引脚,布线要短而粗,回路要短。

DDR4 单端信号阻抗为 50 Ω,差分线阻抗为 100 Ω;焊盘到过孔之间要内层走线,并且尽可能短;所有的内层走线之间不要有信号层,避免串扰和跨分割,走线到平面的边缘必须大于 4 mil;Flyby 拓扑的 stub 走线要短,可以降低走线的有效阻抗;在设计中应该通过减小支线线宽的方式将负载部分的走线设计成高阻抗,负载部分的走线和主线阻抗保持一致,这样可以降低信号反射。

3.3 电源PCB设计

电源要采用模块化设计,保持电源完整性的同时满足各模块所需电流。且电源要远离信号线,避免电源纹波和噪声对信号的干扰。

4 结语

本文设计的一款基于 Hi3559 的 8K 智能摄像机,搭配 8K 电视,给用户带来极致视觉体验。由于受到带宽和速率的限制,Wi-Fi 和 SD 卡默认传输和存储分辨率为 1 080 P。