特征

允许安全插入和移除电路板从带电的48V背板

工作电压从-10V到-80V

可编程浪涌电流

允许50mA反向漏极引脚电流

可编程电子断路器

可编程过压保护

可编程欠压闭锁

功率良好控制输出

应用程序

中央办公交换机

–48V分布式电力系统

负电源控制

说明

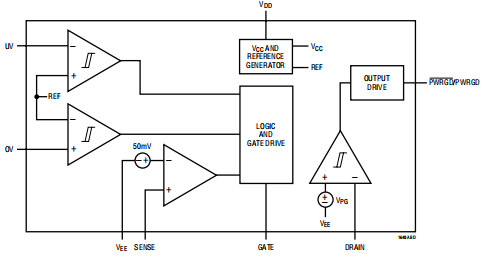

LT®1640AL/LT1640AH为8针,负电压热交换控制器,使电路板安全插入并从活动背板上卸下。通过控制外部N沟道通晶体管的栅电压。这个如果输入电压小于可编程欠压阈值或大于过电压阈值。可编程电子设备断路器保护系统免受短路。这个PWRGD(LT1640AL)或PWRGD(LT1640AH)信号can用于直接启用电源模块。LT1640AL为具有低启用输入和LT1640AH用于具有高启用输入的模块。LT1640AL/LT1640AH提供8针PDIP和所以包装。

绝对最大额定值(注1)

电源电压(VDD–V型)–0.3伏至100伏

PWRGD,PWRGD引脚 –0.3伏至100伏

排液销 –2伏至100伏

感应,门插脚 –0.3伏至20伏

UV、OV引脚 –0.3伏至60伏

最高结温 125摄氏度

工作温度范围

LT1640ALC/LT1640AHC 0°C至70°C

LT1640ALI/LT1640AHI –40°C至85°C

储存温度范围 –65°C至150°C

铅温度(焊接,10秒)300摄氏度

所有电压参考VEE

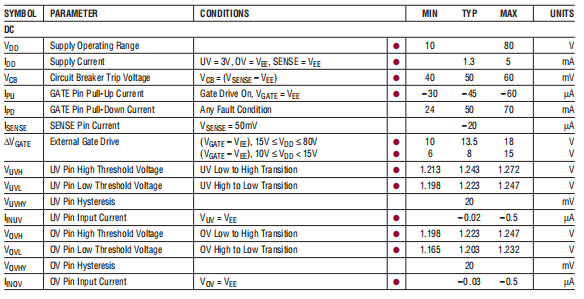

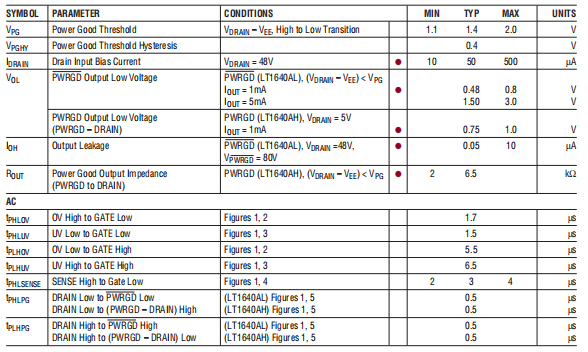

电气特性 表示适用于整个操作的规范

温度范围,否则规格为TA=25°C.(注2),VDD=48V,VEE=0V,除非另有说明。

注1:绝对最大额定值是指超过寿命的值设备可能受损。

注2:所有进入器件引脚的电流都是正的;所有从器件输出的电流都是正的引脚为负。除非另有规定,否则所有电压均参考VEE明确规定。

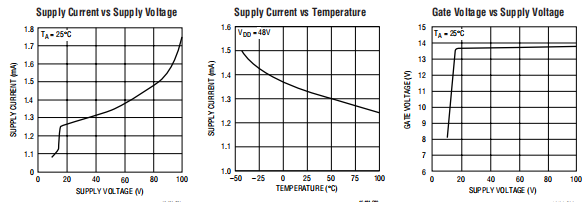

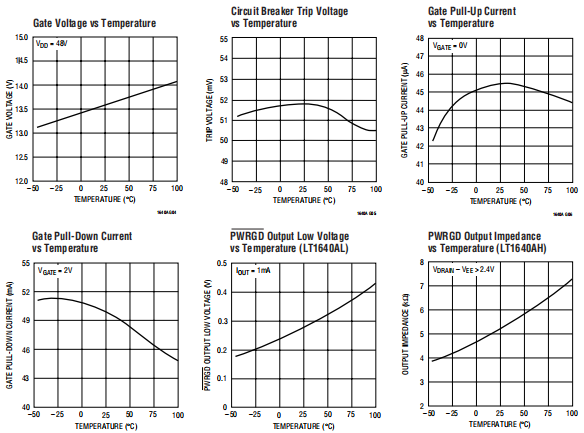

典型性能特征

应用程序

PWRGD/PWRGD(引脚1):电源良好输出引脚。这个别针当VDRAIN在VEE的VPG范围内时将切换。这个别针可以直接连接到电源模块的启用引脚。当LT1640AL的排液销高于VEE by时超过VPG,PWRGD引脚将是高阻抗,允许模块启用引脚的上拉电流将插销拔高,然后关闭模块。当VDRAIN下降到VPG以下,PWRGD引脚吸收电流到VEE,将启用引脚拉低并打开模块。

当LT1640AH的排水销高于VEE by时超过VPG时,PWRGD引脚会将电流汇至将模块启用引脚拉低的漏极引脚,强迫它离开。当VDRAIN低于VPG时,PWRGD关闭漏电流并连接6.5k电阻器在PWRGD和漏极之间,允许模块的上拉电流将使能引脚拉高并打开模块。

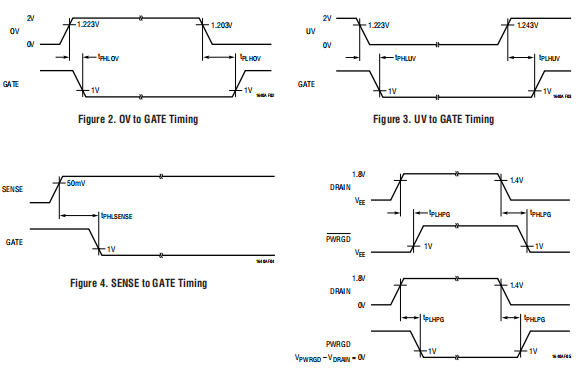

OV(引脚2):模拟过电压输入。当OV被拉时高于1.223V低到高阈值,即过电压检测到状况,门销将立即拉低了。栅极引脚将保持在低位,直到OV下降低于1.203V高到低阈值。

UV(引脚3):模拟欠压输入。当UV为拉到1.223V高到低阈值以下时,检测到欠电压状态,门引脚将立即拉低。门销将保持低位直到紫外线上升到高于1.243的低到高阈值。紫外管脚还用于重置电子电路断路器。如果UV引脚在断路器跳闸,断路器复位将出现正常的通电顺序。

VEE(引脚4):负电源电压输入。连接到电源的低电位。

感应(引脚5):断路器感应引脚。有感觉的放置在VEE和感应时,断路器会在电压电阻超过50mV。噪声尖峰超过2μs被过滤掉,不会使电路跳闸断路器。如果断路器跳闸电流设置为正常值的两倍工作电流,只有25mV在正常工作时感应电阻。禁用断路器、VEE和SENSE可以一起短路。

闸门(针脚6):外部的闸门驱动输出N通道。当以下情况下,闸门销将变高满足启动条件:UV引脚高,OV引脚低且(VSENSE–VEE)<50mV。门销被拉高45μa电流源,并用50mA电流源。

漏极(引脚7):模拟漏感输入。连接此外部N通道和V-引脚的排水管销电源模块的。当排水管脚低于VPG时,PWRGD或PWRGD引脚将切换。在某些情况下,排水销被拉到V形以下。部分不是如果反向放油销电流限制在50mA。

VDD(针脚8):正极电源电压输入。连接此电源输入的高电位引脚,以及电源模块的V+引脚。输入电源电压范围为10V至80V。

热回路插入

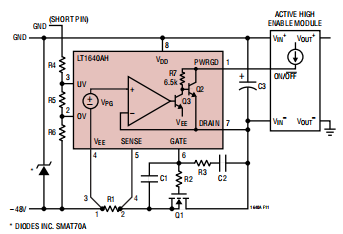

当电路板插入带电的48V背板时,板电源输入处的旁路电容器模块或开关电源在充电时会产生巨大的电流。瞬变电流会对电路板组件造成永久性损坏并导致系统电源出现故障。LT1640A设计用于打开电路板电源控制电压,使电路板从带电背板安全插入或移除。芯片还提供欠压、过压和过电流保护电源模块,直到输入电压稳定且在公差范围内。

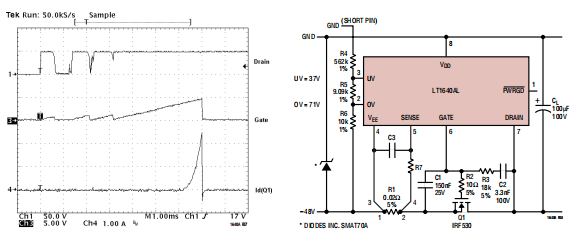

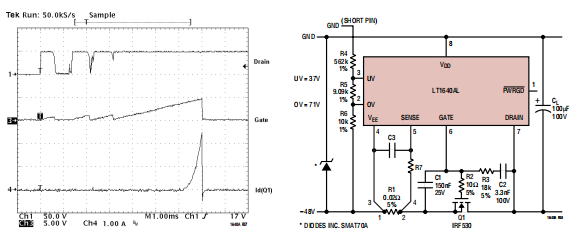

电源斜坡

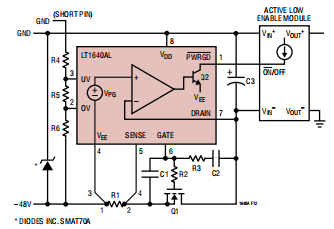

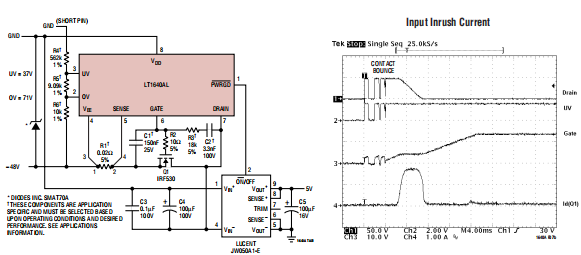

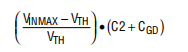

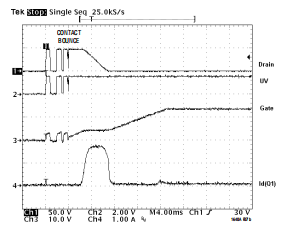

板上电源模块的输入由在功率路径(图6a,所有波形均与LT1640A的V形销)。R1提供电流故障检测和R2可防止高频振荡。电阻R4、R5和R6提供欠压和过压感应。通过缓慢地把Q1的大门向上倾斜电涌电流充电负载电容器C3和C4当电路板连接。电阻器R3和电容器C2作为反馈网络准确控制励磁涌流。励磁涌流可以用以下公式计算:IINRUSH=(45μA•CL)/C2式中,CL是总负载电容等于C3+C4+模块输入电容。电容器C1和电阻器R3防止电源引脚第一次接触时Q1瞬间接通。没有C1和R3,电容器C2会拉Q1的门高达大约等于VEE•C2/CGS(Q1)之前的电压LT1640A可以通电并主动拉闸低。将电容器C1与栅极并联Q1的电容,并使用电阻R3,问题解决。C1的值应该:

其中VTH是MOSFET的最小栅阈值,并且VINMAX是最大工作输入电压。R3的值不是临界值,由(VINMAX+∆VGATE)给出/5毫安。波形如图6b所示插针接触,会弹几次。而触点跳动,LT1640A感应到欠压情况下,闸门立即电源插脚断开时拉低。一旦电源引脚停止弹跳,门引脚开始加强。当Q1打开时,栅极电压保持不变由R3和C2的反馈网络保持恒定。当漏极电压已经完成斜坡,那么栅极引脚渐变到其最终值。

电子断路器

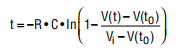

LT1640A具有电子断路器功能,可防止短路或过大的供电电流。在V形管之间放置一个感应电阻当感应电阻上的电压大于50mV,超过3μs,如图7所示。注意,应设置断路器阈值足够高以计算负载电流之和以及励磁涌流。如果负载电流可以控制通过PWRGD/PWRGD引脚(如图6a所示),阈值可以设置得更低,因为它永远不需要适应同时励磁涌流和负载电流。当断路器跳闸时,门销立即拉到V形,外部N通道关闭。这个在断路器复位之前,门引脚将保持在低位通过拉低紫外线,然后高紫外线或循环功率到零件。如果需要超过3μs的除泥时间来拒绝电流噪声,外部电阻和电容器可以添加到检测电路中,如图8所示。R7和C3作为一个低通滤波器,它将减慢感应引脚的速度电压上升过快。因为感应针会源电流,通常为20μA,会出现电压降在R7上。此电压将计入断路器跳闸电压和通过感应电阻的电压一样。建议R7使用小电阻。R7为100Ω会导致2mV错误。可以使用以下公式要估计检测引脚的延迟时间:

其中V(t)是断路器跳闸电压,通常50毫伏。V(tO)是通过感测电阻器的电压降在短路或过电流状态发生之前。不及物动词是电流短路时,感应电阻上的电压或施加过电流。

示例:系统的电流负载为1A,0.02Ω使用感应电阻。扩展延迟电路需要设计为负载跳至后50μs延迟时间

5A.在这种情况下:

V(t)=50毫伏

V(至)=20毫伏

=5A0.02Ω=100毫伏

如果选择R=100Ω,则C=1μF。

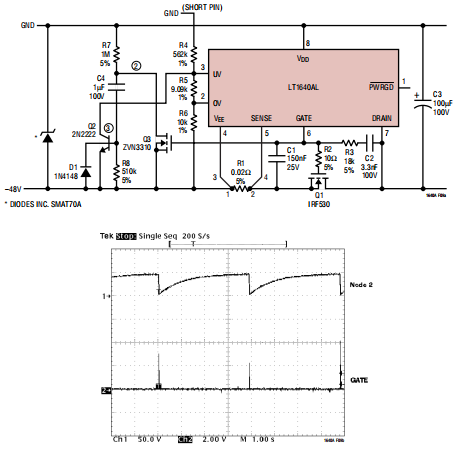

在某些情况下,输出端短路使输入电源低于紫外线阈值,立即复位断路器。LT1640A然后反复循环,直到短路被移除。可以通过添加用一个电容器从UV到维。该电容器与紫外线下的电阻,允许输入电源恢复之前UV引脚复位断路器。一种自动复位断路器的电路电流故障如图9所示。晶体管Q2和Q3以及R7、R8、C4和D1形成一种可编程的一次性电路。在短路发生之前,门销拉高,Q3打开,拉动节点2转向。电阻器R8关闭Q2。当一个发生时,门引脚被拉低,Q3关闭。节点2开始充电C4和Q2打开,拉动UV引脚低并重置断路器。一旦C4完全充电后,R8关闭Q2,UV升高,栅极开始加速。Q3重新打开并快速拉入节点2回到VEE。二极管D1夹住节点3一个二极管下降在V形下方。占空比设置为10%,以防止Q1过热。

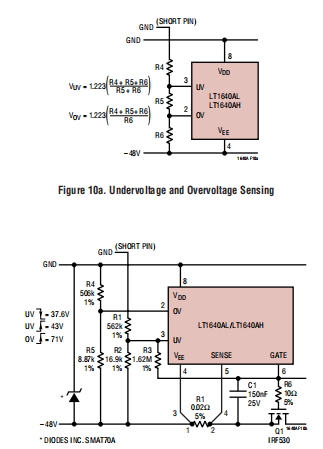

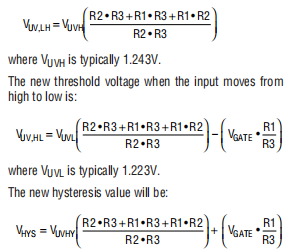

欠压和过压检测

可使用UV(引脚3)和OV(引脚2)引脚进行检测电源欠压和过电压条件电源输入。OV和UV引脚内部连接带20mV滞后的模拟比较器。当UV pin低于阈值或OV pin高于阈值它的门槛,门销立即拉低。这个栅极引脚将保持在较低水平,直到UV高,OV低。欠压和过压跳闸电压可以是使用三电阻分压器编程,如中所示图10a.R4=562k,R5=9.09k,R6=10k时欠压阈值设为37V,过电压阈值设置71V。电阻分压器也将放大UV引脚和OV引脚处的20mV滞后输入端分别为0.6V和1.2V。可以通过以下方式将更多滞后添加到UV阈值在UV引脚和栅极之间连接电阻器R3如图10b所示。

当输入从低电平移动时的新阈值电压高是:

R1=562k,R2=16.9k,R3=1.62M,VGATE=13.5VVUVHY=20mV,欠压阈值为43V(从低到高)和37.6V(从高到低)。这个滞后为5.4V。单独的电阻分压器应用于设置过电压阈值:

当R4=506k,R5=8.87k,VOVH=1.223V时过电压阈值为71V。

PWRGD/PWRGD输出

当输入电压输入到模块时,PWRGD/PWRGD输出可用于直接打开电源模块在公差范围内。LT1640AL具有PWRGD输出对于具有低激活输入的模块,以及LT1640AH有一个PWRGD输出,用于带有高激活输入。当LT1640AH的漏极电压高对于VEE(图11),内部晶体管Q3是关闭,R7和Q2夹紧PWRGD引脚1二极管下降(≈0.7V)以上的排水销。晶体管Q2陷波模块的上拉电流和模块关闭。当漏极电压降到VPG以下时,Q3将开启,将R7底部短接至排水管,并关闭Q2。然后,模块中的上拉电流流过R7,将PWRGD引脚拉高并启用模块。

当LT1640AL的漏极电压高对于VEE,内部下拉晶体管Q2关闭图12为高阻抗状态。PWRGD引脚将被模块的内部上拉电流源,关闭模块。当漏极电压低于VPG时,Q2将导通PWRGD引脚将拉低,从而启用模块。PWRGD信号也可用于打开LED或光隔离器指示电源良好,如图所示在图13中。

门引脚电压调节

当芯片的供电电压大于15.5V时,栅极引脚电压被调节为高于VEE的13.5V。如果电源电压低于15.5V,栅极电压将低于电源电压约2伏。最低10伏电源电压,栅极电压保证更大大于6V,门电压不大于18V电源电压高达80V。

排液销保护

LT1640A的一个独特特点是放油销。排水管设计成能承受负极不需要外部二极管的电压(关于V型)。48V背板上出现短路V形管脚,但由于储能电容器C3(图12),漏极管脚比V形管脚更负别针。Q1的主体二极管,加上R1上的I•R压降(如果R1是小的),保持漏极引脚低于1.5V维。1.5V反向电压产生50mA反向电压漏极电流,在LT1640A。R1大于0.1Ω的设计可能需要与漏极引脚串联的电阻不超过最大50mA漏电流。