TQFP64点击型号即可查看芯片规格书

L6713A点击型号即可查看芯片规格书

一般特征

负载瞬态升压(LTB)技术™ 到尽量减少输出电容器的数量(正在申请专利)

双边缘异步PWM

可选2相或3相操作

0.5%输出电压精度

高达1.60000V的7/8位可编程输出-Intel VR10.x,VR11 DAC

高达1.5500V的6位可编程输出-AMD 6位DAC

大电流集成门驱动器

通过感应器的全差分电流感应

嵌入式VRD热监视器

差分遥感电压

动态视频管理

可调电压偏移

低侧启动

可编程软启动

可编程过压保护

初步过电压保护

可编程过电流保护

可调开关频率

输出启用

SS_END/PGOOD信号

TQFP64 10x10mm包装,带外露衬垫

应用

台式CPU的大电流VRD

工作站和服务器CPU电源

VRM模块

说明

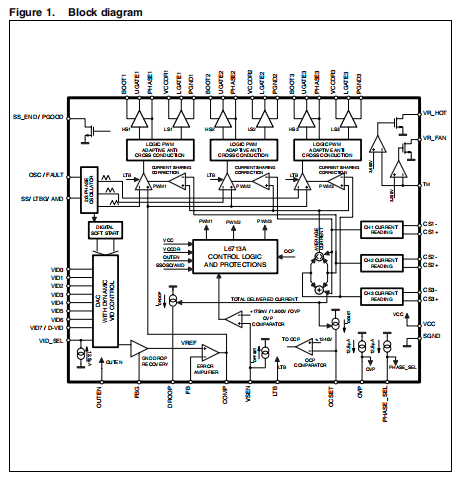

L6713A执行两/三相降压具有180o/120o相移的控制器各相集成高电流驱动器紧凑型10x10mm车身组件垫子。那个2相或3相操作很容易通过相位选择引脚选择。负载瞬态升压(LTB)技术™ (专利待定)通过提供因此,对负载转换的最快响应需要较少的体积和陶瓷输出电容器以满足负载瞬态要求。LTB技术™ 可以禁用和在此条件设备作为双边缘工作异步PWM。设备嵌入可选的dac:输出电压范围高达1.60000V(均为Intel VR10.x和VR11 DAC)或高达1.5500V(AMD 6位DAC)用±0.5%的输出电压管理D-VID线路和温度变化的精度。控制器确保快速保护负载过电流和欠压/过压也在UVLO之前)。过流时该装置关闭所有MOSFET并锁定条件。还提供了系统热监视器,允许系统过热保护条件。

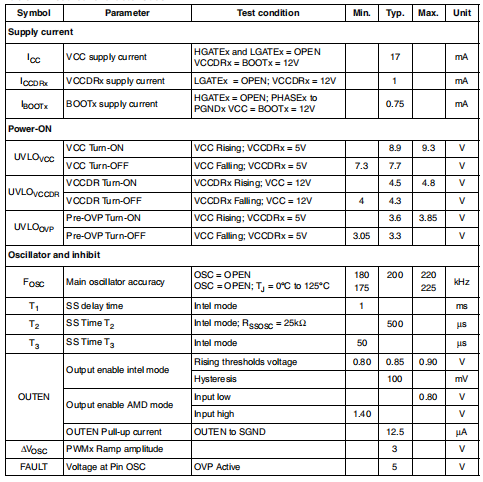

电气特性

VCC=12V±15%,TJ=0°C至70°C,除非另有规定

设备说明

L6713A是双/三相PWM控制器,内置大电流驱动器,提供高性能降压DC-DC电压的完整控制逻辑和保护调节器优化先进的微处理器电源。多相buck是最简单、最经济的拓扑结构,可以满足对新型微处理器和现代大电流VRM的需求不断增加模块。它允许使用更小、更便宜和最常见的外部功率mosfet和电感器。而且,多亏了每相之间相移,输入和输出电容器计数结果减少。相位交错实际上导致输入均方根电流和输出纹波电压降低并显示出有效的输出开关频率增加:每相200kHz的自由运行频率,可通过电阻器进行外部调节,结果成倍增加按相数输出。L6713A是一种双边缘异步PWM控制器,具有负载瞬态升压(LTB)技术™ (正在申请专利):该装置将同时开启所有相位当检测到负载瞬态时,允许通过提供最快的对负载转换的响应。检测负载转换(通过LTB引脚)测量输出的导数dV/dt电压和dV/dt可以很容易地编程,扩展了系统设计的灵活性。此外,负载瞬态升压(LTB)技术™ 增益可以很容易地修改,以便控制输出电压回环。LTB技术™ 可以禁用,在这种情况下,设备作为一个双边缘工作异步PWM。控制器允许实现可扩展的设计:三相设计可以很容易地实现只需保留一个相位不安装并离开即可降级为两相相位选择引脚浮动。同一设计可以用于多个项目,节省开发和调试时间。同样,两阶段的设计可以进一步升级到三相面对更新和高要求的应用程序。L6713A允许通过感应器的电流读数完全进入,从而简化系统设计差分模式。也可以考虑串联到电感器上的感测电阻提高阅读精度。读取的电流信息校正PWM输出,以使平均值相等在静态和动态条件下,各相所载电流将误差限制在±3%除非考虑到传感元件的扩展。控制器包括多个DAC,可通过适当的引脚进行选择,允许同时兼容Intel VR10、VR11和AMD 6BIT处理器规格相应地进行D-VID转换。低侧启动允许软启动超过预偏置输出避免危险电流通过主电感器以及负载侧的负尖峰返回。

L6713A提供可编程过电压保护,以保护负载危险的过度压力。它可以通过适当的外部设置为固定电压电阻,或者可以在内部设置,通过打开下驱动器和驱动高故障引脚。此外,初步OVP保护还允许设备保护负载VCC不高于UVLO阈值时出现危险的OVP。过电流保护作用于总输出电流,并导致装置转动关闭所有MOSFET并锁定状态。L6713A还提供系统热监测:通过一个合适的引脚设备感测驱动警告的应用程序中最热部件的温度结果是警报信号。紧凑型10 x 10毫米机身TQFP64封装,带外露散热垫,可散热通过系统板驱动外部MOSFET的电源。

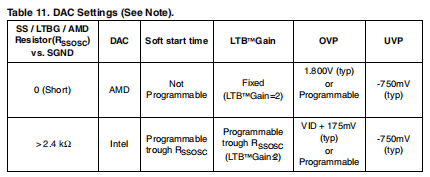

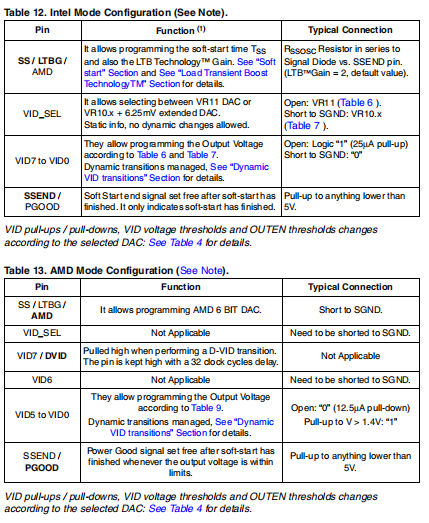

配置设备

在系统启动之前,需要配置相数和多个DAC编程合适的引脚相位选择和SS/LTBG/AMD引脚。该引脚的配置确定了两个主要工作区(见表11)的区别符合Intel VR10、VR11或AMD 6BIT规格。根据考虑到主规范,可以进行进一步的定制:主要区别是关于DAC表,软启动实现,保护管理和动态视频转换。有关设备的更多详细信息,请参见表12和表13配置。

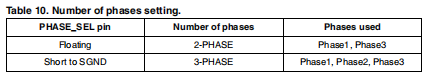

相数选择

L6713A允许简单地使用相位选择引脚,如下表所示。

DAC选择

L6713A嵌入一个可选的DAC(通过SS/LTBG/AMD引脚,见表11),允许调节输出电压,公差为±0.5%(AMD DAC为±0.6%),恢复补偿和制造变更。如果选择Intel模式,则设备自动向调节电压引入-19mV(VRD10.x和VR11)偏移为了避免任何外部偏置电路恶化保证精度,作为结果,计算出的系统TOB

注:选择Intel模式时,SS/LTBG/AMD引脚用于选择软启动时间和长期借款™ 增益(见专用部分)输出电压通过VID引脚编程:它们是内部DAC的输入是通过一系列提供内部电压分区的电阻来实现的参考。VID代码驱动多路复用器,在分隔线。DAC输出被传送到获得参考电压的放大器(即误差放大器的设定值,VREF)。

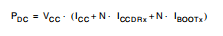

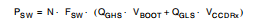

功率损耗

L6713A为高侧和低侧MOSFET嵌入了高电流MOSFET驱动器:it然后考虑设备在驱动它们时所消耗的功率是很重要的以避免克服最高结工作温度。此外,因为该设备有一个裸露的衬垫,以更好地耗散功率,热电阻连接处与周围环境之间的布局也随之重要:散热垫需要通过几个通孔焊接到PCB接地层上,以便散热。两个方面:驱动功率和驱动功率。第一个(PDC)取决于装置通过电源引脚的静态消耗它可以简单地量化如下(假设为HS和LS驱动器提供相同的驱动程序设备的VCC):

其中N是相数。驾驶员电源是驾驶员持续打开和关闭外部MOSFET;它是开关频率和总栅电荷的函数选择MOSFET。考虑到总功率PSW耗散到开关mosfet(易于计算)的损耗主要有三个因素:外栅极电阻(如果存在)、本征MOSFET电阻和本征驱动器电阻。这个最后一项是器件功耗计算中需要确定的重要项。开关MOSFET所消耗的总功率结果:

外部栅极电阻有助于器件耗散开关功率,因为功率PSW将在内部驱动器阻抗和外部电阻器之间共享导致设备普遍冷却。当并联驱动多个mosfet时建议每个MOSFET使用一个栅极电阻。

电流读数和均流回路

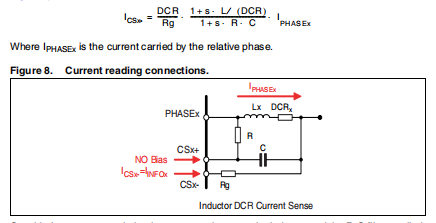

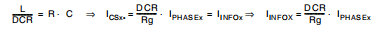

L6713A嵌入了一个灵活的,全差分电流检测电路,能够读出电感器寄生电阻或串联在感应器上的感测电阻元素。全差分电流读数可抑制噪声并允许放置感测不影响测量精度的不同位置的元件。读取电流通过电感器DCR时,电流通过每一相被读取使用输出电感器或感测电阻串联时的电压降内部转换成电流。反导比由外部电阻Rg放置在芯片外部CSx引脚之间,朝向读取点。电流检测电路始终跟踪电流信息,不产生偏置电流来自CSx+引脚:该引脚用作保持CSx引脚电压的参考。到正确再现电感电流必须引入R-C滤波网络与传感元件平行。从CSx引脚流出的电流由以下等式给出(参见图8):

现在考虑匹配电感和R-C滤波器之间的时间常数(时间常数不匹配导致在电流读数网络中引入电极造成不稳定。此外,负荷瞬态响应也很重要系统显示电阻等效输出阻抗),结果:

其中iinfo是内部复制的当前信息。

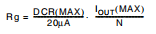

必须使用以下公式按顺序选择Rg反电导电阻器为保证内部电流读数电路的正确功能:

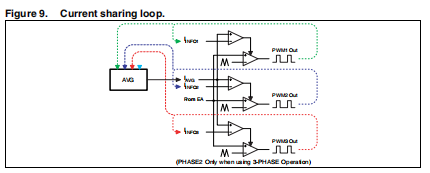

图9中报告的均流控制回路:它认为电流IINFOx与每相电流和平均电流。错误读取电流IINFOx和参考IAVG之间的电压转换为使用适当的增益来调整占空比,其主导值由电压误差放大器,以均衡各相所携带的电流。关于连接如图8所示。

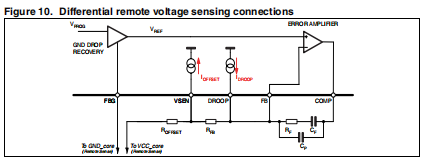

差分遥感电压

在FB和FBG引脚之间的全差分模式下检测输出电压。FB引脚必须通过电阻器连接到调节点,而光纤光栅引脚必须直接连接到遥感接地点。通过这种方式,编程的输出电压在远程感测点之间进行调节补偿主板或连接器损耗。保持FB和FBG轨迹平行,并由电源板保护,结果是共同的任何拾取噪声的模式耦合。

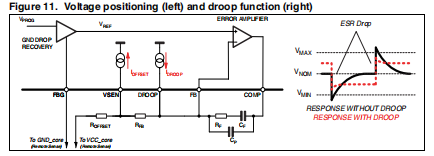

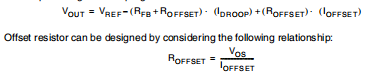

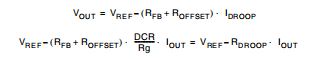

输出电压定位通过选择基准DAC和编程速降功能和偏移到参考值(参见图11)。洋流源于下垂和下沉的VSEN引脚导致输出电压根据至外部RFB和ROFFSET电阻器。输出电压由以下关系驱动:

可禁用降速和降速销连接功能

销在一起实现了负载调节的依赖性,而如果这种效果不理想,通过将下垂管脚短路到SGND,器件可以作为经典电压运行模式降压转换器。降速销也可以通过电阻器连接到SGND获得与可用于监测目的的电流成比例的电压。使用ROFFSET等于零可以禁用偏移。

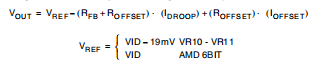

偏移量(可选)

来自VSEN引脚的IOFFSET电流(见表4)允许编程为正通过在VSEN引脚和VOUT,如图11所示;除了这个偏移量之外,还必须考虑这个偏移量已经在生产阶段为Intel VR10,VR11模式引入。输出电压编程如下:

DAC选择自动给出的偏移量与通过实现的偏移量不同

补偿电流:内置特性在生产中进行微调,保证±0.5%的误差(AMD DAC为±0.6%)过载和线路变化。

降速功能(可选)

这种方法“恢复”部分由于负载中的输出电容ESR引起的下降瞬态,引入输出电压对负载电流的依赖性:静态误差与输出电流成比例导致输出电压根据感测到的电流。如图11所示,ESR下降在任何情况下都是存在的,但使用的是降速函数输出电压的总偏差为最小化。而且越来越多的高性能cpu需要精确的负载线调节才能正常工作。降速功能不仅需要优化输出滤波器,而且还需要负荷要求。将下垂管脚和FB引脚连接在一起,装置会强制电流IDROOP,与读取电流成比例,进入反馈电阻(RFB+ROFFSET)中,实现负荷调节依赖性。因为IDROOP依赖于N的当前信息相位,输出特性与负载电流的关系由(忽略偏移量电压项):

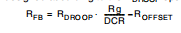

其中,DCR是电感器寄生电阻(或使用时的感应电阻),IOUT是系统输出电流。整个电源可以用“真实”来表示具有等效输出电阻RDROOP和电压值VREF的电压发生器。RFB电阻器也可根据RDROOP规范设计如下:

速降功能是可选的,如果不需要,可以断开速降销从FB获得关于总输出电流的信息调试和/或电流监控。不使用时,引脚可短接到SGND

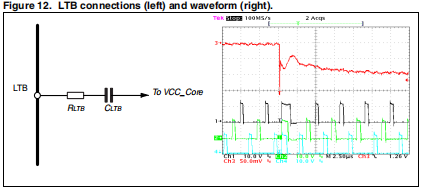

负载瞬态升压技术

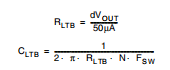

负载瞬态升压(LTB)技术™ (正在申请专利)是L6713A的一项功能,可将考虑负载瞬态的输出滤波电容器(MLCC和大容量电容器)的计数规范。一旦检测到负载瞬态,该装置将同时开启所有相位让它们在必要的时间内保持运转,为装载。这个时间取决于补偿引脚电压和内部增益,以保持对输出电压回响。通过连接RLTB-CLTB与VOUT:设备的LTB引脚检测负载转换测量输出电压的导数dV/dt,因此它能够接通所有相位在负载转移检测后立即进行,最大限度地减少延迟干预。修改RLTB-CLTB值dV/dt可以很容易地编程,扩展了系统设计灵活性

其中,dVOUT是由于负载转换而产生的输出电压降。此外,负载瞬态升压(LTB)技术™ 增益可以很容易地修改,以便控制输出电压回环。

将LTB引脚短接至SGND以禁用LTB技术™:在这种情况下,设备工作作为双边缘异步PWM控制器。