LTC1292点击型号即可查看芯片规格书

LTC1297点击型号即可查看芯片规格书

使用PC板。接地针脚(针脚4)应系紧直接接地平面,最小引线长度(a低调的插座是可以的)。图7显示了双面板的理想LTC1292/LTC1297接地层设计。当然,这么多的地面飞机不会总是可能的,但是用户应该努力接近为了这个理想。

旁路

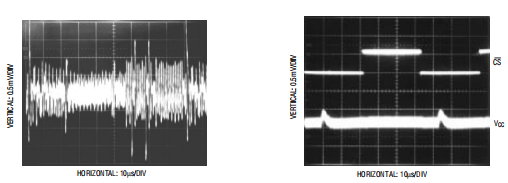

为了获得良好的性能,VCC必须没有噪音和涟漪。有关VCC电压的任何变化在转换周期内接地可能会导致错误或输出代码中有噪音。VCC噪声和纹波可以保持通过将VCC引脚直接旁路至钽含量至少为22μF的模拟接地层电容器和引线尽可能短。线索从设备到VCC电源也应保持在最小值,VCC电源应具有低输出阻抗,如从电压调节器获得的阻抗(例如LT323A)。对于高频旁路,0.1μF与22μF平行放置的陶瓷盘推荐。同样,导线应保持在最小值。图8和图9显示了good和VCC旁路不良。

模拟输入

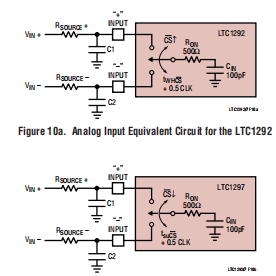

因为电容再分配A/D转换所使用的技术,LTC1292的模拟输入/LTC1297具有电容开关输入电流峰值。这些电流尖峰很快稳定下来,不会导致问题。如果使用大的源电阻或速度慢稳定的运算放大器驱动输入,注意确保电流尖峰引起的瞬变完全消失在转换开始之前。

源电阻

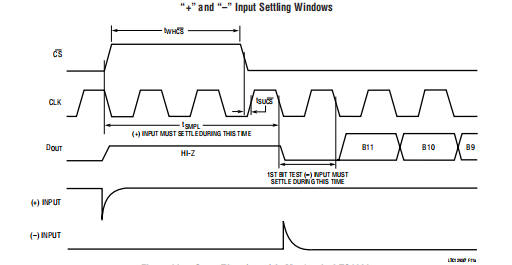

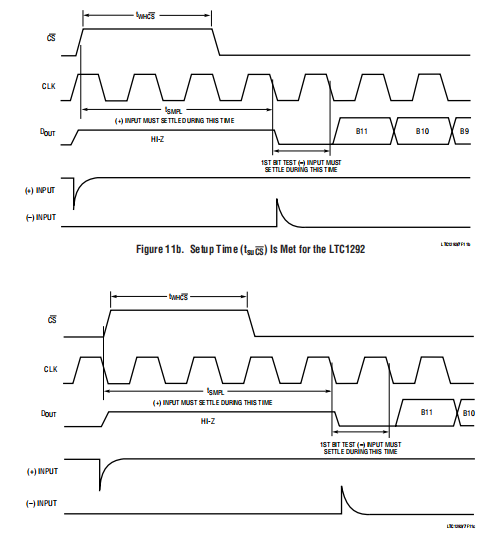

LTC1292/LTC1297的模拟输入看起来像100pF电容器(CIN)与500Ω电阻器(RON)串联(图10a和10b)。CIN在(+)和之间切换(–)在每个转换周期中输入一次。大外部源电阻和电容会降低输入的设置。重要的是整个RC时间常数足够短,以允许模拟输入在允许的时间内完全解决。“+”输入设置LTC1292的输入电容器切换到在采样阶段输入“+”(tSMPL,见图11a,11b和11c)。采样周期可短至tWHCS+1/2 CLK循环或与tWHCS+1 1/2 CLK循环一样长在转换开始之前。这种可变性取决于其中CS相对于CLK下降。“+”输入端的电压必须在样品期内完全沉淀。最小化RSOURCE+和C1将改善沉降时间。如果大“+”输入源必须使用电阻,采样时间可以通过使用较慢的CLK频率来增加。和最短采样时间为3.0μs,RSOURCE+<2.0kC1<20pF将提供足够的沉降时间。

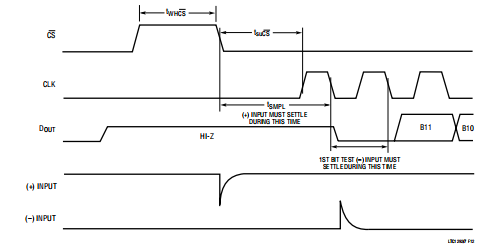

LTC1297的采样周期从下降开始CS的边缘和第一个CLK的下降边缘结束(图12)。采样周期的长度为tsuCS+0.5CLK循环。同样,“+”输入端的电压必须稳定完全在样品期内。如果输入“+”大必须使用源电阻,采样时间可以通过使用较慢的CLK频率或增加

tsuCS。最短采样时间为6μs,RSOURCE+<5k和C1<20pF将提供足够的稳定时间。一般情况下,LTC1292和LTC1297保持总阻力和总阻力的乘积电容小于tSMPL/9。如果这种情况不能met,然后使C1>0.47μF(参见RC输入滤波第节)。

“–”输入设置

在采样阶段结束时,输入电容器切换到“–”输入,转换开始(参见图11a,11b、11c和12)。在转换过程中,“+”输入电压被采样保持有效地“保持”并且不会影响转换结果。至关重要的是

“–”输入电压无噪声,完全稳定在转换的第一个CLK循环期间。最小化RSOURCE–和C2将改善沉降时间。如果大“–”输入源电阻必须使用的时间可以通过使用较慢的CLK频率进行扩展。最多的时候CLK频率为1MHz,RSOURCE–<250Ω和C2<20pF将提供足够的沉降。

输入运算放大器

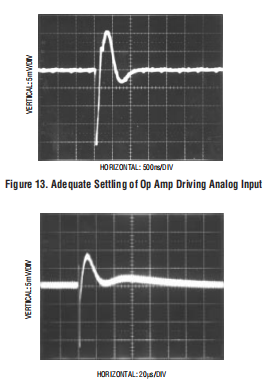

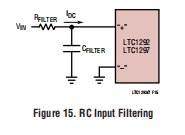

当用运算放大器驱动模拟输入时重要的是运算放大器在允许的时间内稳定下来(见图11a、11b、11c和12)。再说一遍“+”和“-“输入采样时间可按说明延长以适应较慢的运算放大器。大多数运算放大器包括LT1797和LT1677单电源运算放大器即使使用最小沉降量也能使沉降良好对于LTC1292,窗口为3.0μs,对于LTC1297(“+”输入)和1μs(“–”输入)最大时钟频率为1MHz。图13和14显示适当和较差的运算放大器设置的例子。

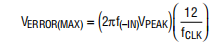

RC输入滤波

可以用RC网络过滤输入如图15所示。对于较大的CF值(例如1μF),则电容输入开关电流被平均到一个网络中直流电流。滤波器应选用小电阻和大电容器,以防止直流电压降过电阻器。直流电流的大小约为IDC=100pF×VIN/tCYC,与VIN大致成比例。什么时候?以最小周期运行LTC1292(LTC1297)时间为16.5μs(20μs),输入电流等于30μA(25μA)在VIN=5V时。此时4Ω(5Ω)的滤波电阻将导致0.1LSB满标度误差。如果一个大的滤波电阻必须使用,可以通过增加典型性能所示的循环时间最大滤波电阻与周期的特性曲线时间。

输入漏电流

输入漏电流也会在源阻力太大了。例如,最大输入流经源的1μA泄漏规格1k电阻会导致1mV或8磅。这种误差在较低的情况下会大大减少因为泄漏迅速下降(见典型输入信道泄漏性能特性曲线电流与温度)。

抽样保留

单端输入

LTC1292/LTC1297在+in输入端为采集的信号提供一个内置的采样和保持(S&H)功能在单端模式下(–针脚接地)。采样和保持允许LTC1292/LTC1297快速转换变化信号(见典型性能特征S&H采集时间与源电阻的曲线)。这个输入电压在tSMPL时间内采样,如图所示在图11中。采样间隔从上升开始LTC1292的CS边缘和CS下降边缘对于LTC1297,一直持续到转换开始前CLK。在这个下降的边缘S&H进入保持模式,转换开始。

差分输入

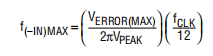

有了差分输入,a/D不再转换单个但是转换两个电压之间的差。对+IN引脚上的电压进行采样并保持快速时变的,如单端模式。电压在–IN销上必须保持恒定且无噪音在整个转换过程中产生涟漪。否则差分运算不能准确地进行。这个转换时间为12 CLK周期。因此在这段时间内输入电压会导致转换错误。对于输入端的正弦电压输入此错误为:

其中f(–IN)是–IN输入电压的频率,VPEAK是其峰值振幅,fCLK是克莱克。通常情况下,错误并不重要。对于60Hz输入端的信号产生0.25LSB的误差(300μV)当转换器以CLK=1MHz运行时,其峰值必须是66mV。重新安排上述内容方程式最大正弦信号数字化到给定精度的公式如下:

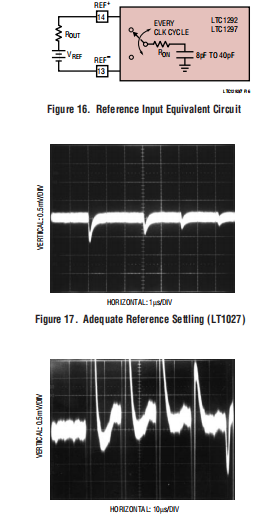

对于0.25LSB误差(300μV),最大输入正弦曲线开关电容转换技术产生的开关电流(见图16)。在每个位测试期间转换(每个CLK周期)的电容电流A/D将在参考引脚上产生尖峰。这些电流尖峰很快稳定下来,不会导致问题。如果慢沉降电路用于驱动参考输入,注意确保瞬态由于这些电流尖峰在转换的每一位测试5V峰值振幅可数字化为0.8Hz。

参考输入

LTC1292参考输入端的电压/LTC1297确定A/D转换器的电压范围。参考输入具有瞬态电容性

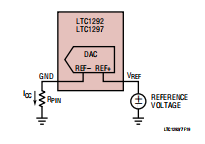

图17和18显示了适当和沉降差。使用较慢的CLK将允许更多的时间以供参考结算。即使在最高时钟1MHz的速率大多数参考和运算放大器可以使其在1μs位时间内沉降。例如LT1790将充分解决。

简化参考操作

LTC1292/LTC1297的有效分辨率可以通过减小转换器的输入范围来增加。LTC1292/LTC1297具有良好的线性在一个参考电压范围内(见线性度与参考电压)。由于LSB降低,在低VREF值下操作时必须小心步长和由此产生的更高精度要求放在转换器上。偏移和噪声是影响因素在低VREF下运行时必须考虑这一点价值观。VREF的内部引用已绑定到GND引脚。从GND引脚到接地层将导致增益误差。减小VREF的偏移量LTC1292/LTC1297的偏移量影响较大A/D操作时的输出代码降低参考电压。偏移量(通常是固定电压)变为当LSB的大小减小时。典型的未调整的偏移误差与参考电压的性能特性曲线显示了偏移量的大小LSB与参考电压有关,为典型值关于VOS。例如0.1mV的VOS,即0.1LSB在5V的情况下,参考电压变为0.4LSB,电压为1.25V参考。如果此偏移量不可接受,则可以通过接收系统或偏移LTC1292/LTC1297的输入进行数字校正。

降低VREF的噪声

LTC1292/LTC1297的总输入参考噪声可使用地平面,良好的旁路,良好的布局技术关于输入和最小化噪声。这个噪声在5V参考输入下是微不足道的,但是成为LSB的一个更大的部分作为LSB的大小减少了。典型的性能特征噪声误差与参考电压的关系曲线显示200μV噪声的LSB贡献。对于5V参考电压下的操作,200μV噪声为峰间只有0.16LSB。这里是LTC1292/LTC1297噪音几乎不会对输出代码。对于减少的参考,噪声可能成为LSB的重要组成部分输出代码中不需要的抖动。例如,使用在1.25V参考电压下,该200μV噪声的峰间为0.64LSB。这将减小输入电压的范围通过它可以获得稳定的输出代码0.64磅。现在,平均读数可能是必要的。这些噪音数据是在一个非常干净的测试夹具中采集的。任何设置引起的噪声(VCC、VREF上的噪声或波纹或VIN)会增加内部噪音。越低的参考电压越高有一个无噪音的设置。减小VREF导致的增益误差LTC1292/LTC1297的增益误差很好在广泛的参考电压范围内。错误在典型性能中看到的组件增益误差与参考电压的特性曲线变化是由于GND引脚上的电压降引起的从设备到地平面。尽量减少这种情况错误LTC1292/LTC1297应直接焊接到PC板上。内部参考点因为VREF与GND相连。GND引脚是否有电压降使参考电压,在装置内部,小于外部应用的值(图19)。这个由于引脚的乘积,压降通常为420μV电阻(RPIN)和LTC1292/LTC1297电源电流。

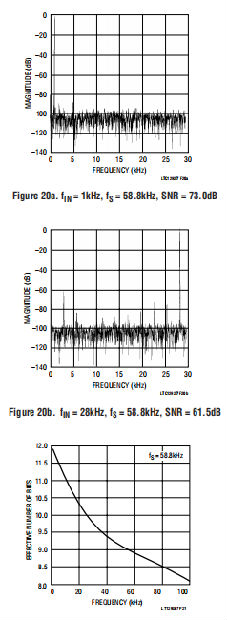

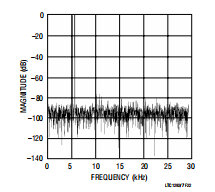

例如,当VREF=1.25V时,这将导致在增益误差与增益误差相差-1.0LSB时VREF=5V测量。LTC1292交流特性两个常用的优点数字,用于指定数字信号中A/Ds的动态性能处理应用是信噪比(SNR)和“有效比特数(ENOB)。”SNR是基波的均方根值与所有非基波信号的均方根值高达奈奎斯特频率(采样频率的一半)。正弦波的理论最大信噪比输入由:信噪比=(6.02N+1.76dB)其中N是位的数目。因此信噪比取决于关于A/D的分辨率。理想的12位A/D信噪比等于74dB。快速傅里叶变换图中显示了LTC1292的输出光谱图在图20a和20b中,输入(fIN)频率为1kHz和28kHz,采样频率(fS)为58.8千赫。测得的snr为73.0dB61.5分贝。通过重写SNR表达式,可以获得基于信噪比测量的等效分辨率。

这是有效位数(ENOB)。对于示例如图20a和20b所示,N=11.8位和9.9位。图21显示了ENOB作为输入频率的函数。第二个谐波失真项解释了ENOB as fIN接近fS/2。图22显示了应用于A/D输入的两个音调。非线性在A/D中,会导致畸变产物的总和和基本原理和基本原理产品的不同频率。这是经典的说法作为互调失真(IMD)。

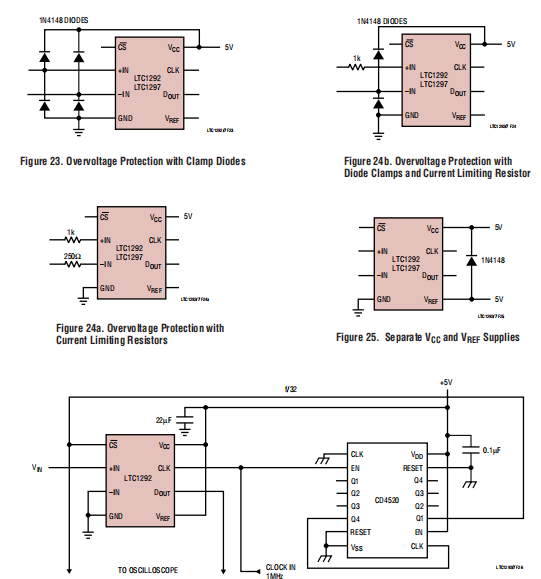

过电压保护

将信号应用于LTC1292/LTC1297的模拟超过正电源或低于正电源的输入地面将降低A/D的精度,并可能损坏设备。例如这个条件如果信号被应用于模拟输入,则会发生在LTC1292/LTC1297通电之前。另一个例子是输入源是从比LTC1292更有价值的不同供应/

LTC1297。这些情况也应加以预防通过适当的供应顺序或使用外部箝位或电流限制输入源的电路。有两种保护输入的方法。在图23中从VCC和GND的输入端使用二极管夹。第二种方法是将电阻器与限流模拟输入。将电流限制为每个通道15mA。+IN输入可以接受一个电阻器值1k,但–IN输入不能接受大于250Ω,当其最大时钟频率为1兆赫。如果LTC1292/LTC1297在最大时钟频率和250Ω不足以电流限制输入源,则钳位二极管推荐(图24a和24b)。原因电阻值的限制是MSB位测试受放置在–IN处的电阻值的影响输入(参见关于模拟输入和典型性能特性最大时钟频率vs源电阻)。

如果VCC和VREF没有连接在一起,那么VCC应该先打开,再打开VREF。如果这个序列不能met,建议将二极管从VREF连接到VCC(见图25)。因为独特的输入保护结构用于数字输入引脚,这些引脚上的信号电平可以在不损坏设备的情况下超过设备VCC。

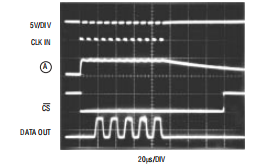

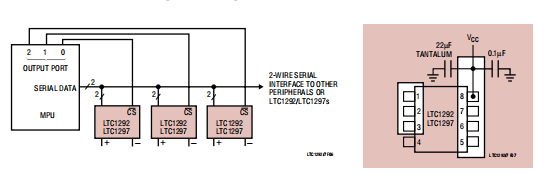

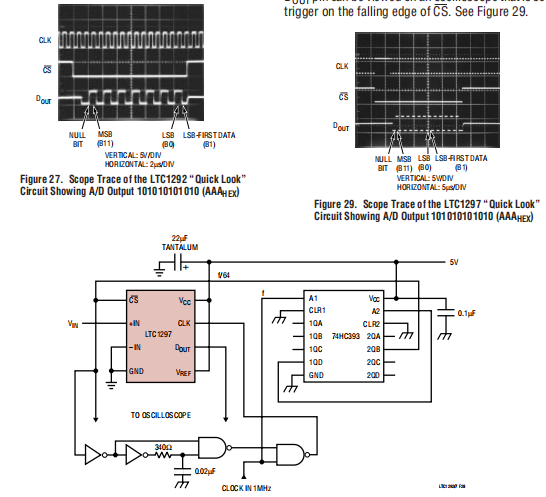

LTC1292的“快速查看”电路用户可以快速了解LTC1292使用图中的“快速查看”电路26VREF与VCC绑定。VIN应用于+IN输入输入端连接到地平面。CS被驱动在1/32时钟速率下由CD4520和DOUT输出数据。DOUT管脚的输出数据可以是在设置为触发的示波器上查看CS下降沿(图27)。注意LSB数据是在CS变高之前部分打卡。

LTC1297的“快速查看”电路类似于LTC1292的电路可以是用于LTC1297(图28)。只有一次机会用与非门、电阻和电容产生满足设置时间tsuCS。如果使用较慢的时钟。当CS变低的时候触发。这将关闭LTC1297的时钟固定的时间见tsuCS。时钟一开始,杜特就开始了一次移动一点。CS以1/64的速度驱动时钟速率为74HC393。的输出数据可以在设置为的示波器上查看双引脚CS下降沿触发。见图29。

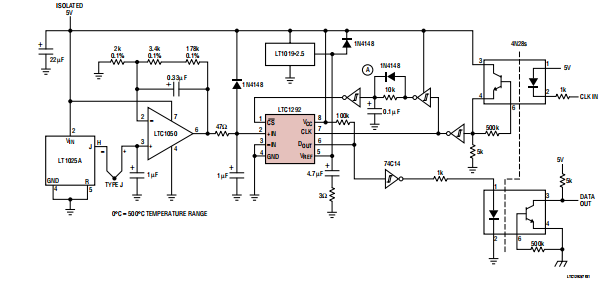

光隔离温度监测器

通常需要放大传感器输出产生一个足够大的信号来正确数字化。例如,J型热电偶仅提供52μV/°C。LTC1050斩波器操作的5μV偏移amp产生的误差小于0.1°C(图31)。冷结补偿由LT1025A提供。(更多详情见LTC设计注释5)。在光隔离接口中产生两个信号从一开始。这允许一个两线接口连接到LTC1292型。CLK IN输入上的长高信号(>1ms)允许0.1μF电容器在CS高的情况下放电。这将重置下一次转换的A/D。当CLK在开始切换时,CS变低并保持在那里直到下一个在高时间延长时钟。见图30。