L9848点击型号即可查看芯片规格书

可配置多达6个高端驱动器

RDSON=最大1.5Ω@Tj=25°C

每个输出的电流限制至少为0.8A

电源电压4.75V至5.25V

输出电压钳位最小35V(低压侧模式)

输出电压钳位-30V(高压侧模式)

数据通信用SPI接口

2个输出的额外PWM输入

所有输出的热关机

关闭模式下的开放式负载检测

输出反向电池保护(amb)

高压侧接地断开配置

输出

说明

L9848集成电路是一种高度灵活的单片介质包含2个专用的电流输出驱动器低端输出(输出7-8)和6个可以用作内部低端或高端驱动任意组合(输出1-6)。此外,2个输出能够通过外部引脚进行PWMed(输出5-6)。集成标准串行外围接口(SPI)控制所有输出并提供诊断信息。集成箝位电路,波形成形,正、负电压瞬变保护、所有输出的热关机汽车和工业应用范围

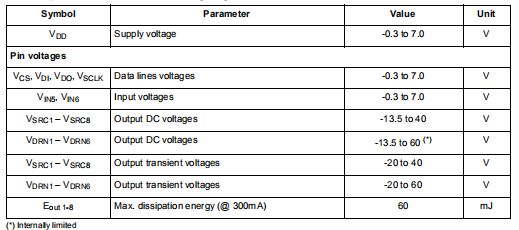

绝对最大额定值

用于外部施加到设备上的电压和电流。如果将此零件从规定的绝对最大额定值范围外取出,可能会造成无法修复的损坏

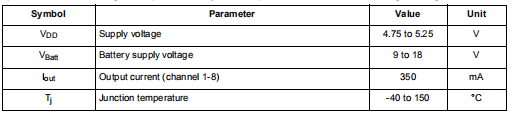

操作条件

如果超出最大额定值,此部件可能无法工作。一旦条件恢复到

规定的最大额定值或功率被重新循环,零件将恢复而不会损坏或退化。

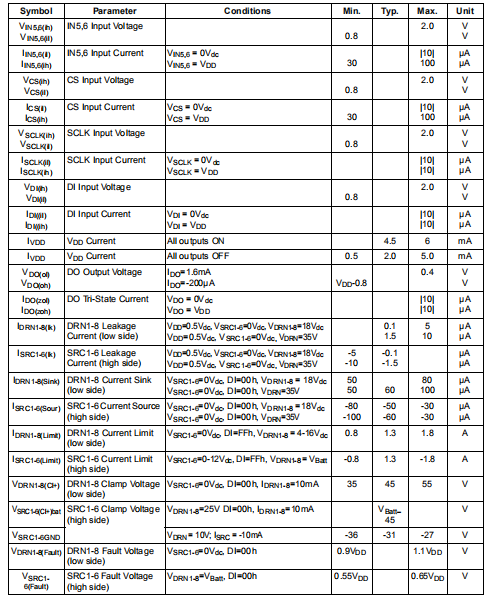

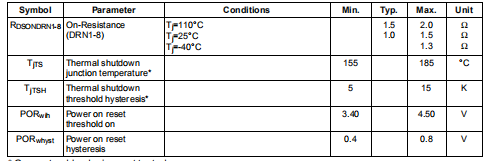

电气特性

直流特性

(Tj=-40°C至150°C,VDD=4.75Vdc至5.25Vdc,VBatt=9V至18V,除非另有规定)

电气特性(续)

直流特性

(Tj=-40°C至150°C,VDD=4.75Vdc至5.25Vdc,VBatt=9V至18V,除非另有规定)

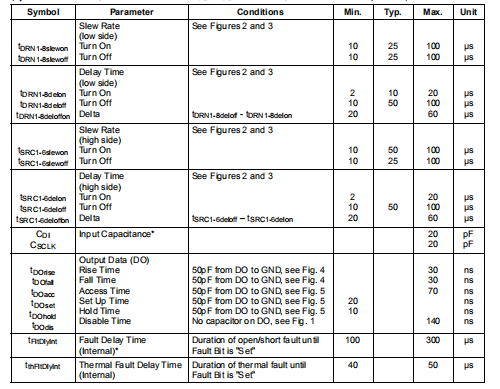

交流特性

(Tj=-40°C至150°C,VDD=4.75V至5.25Vdc,VBatt=9V至18V,除非另有规定)

功能描述

一般特征

L9848集成电路是一个单片集成电路,它为驱动中等负载提供了高度的灵活性。8个输出,其中6个(输出1-6)可以作为任何组合的内部低端或高端驱动器,2个是专用低压侧输出(输出7-8)。使用该设备可通过SPI接口串行控制输出,从而降低微处理器的I/O端口要求。此外,输出5-6能够通过外部引脚(输入5-6)进行PWMed。8位SPI输入用于命令8个输出驱动器打开或关闭和附加,以指示可能已发生的锁定故障条件。多个L9848可以通过菊花链与每个设备的一个额外的微处理器I/O端口(CSn)相连。实现的自配置允许用户将高侧或低压侧负载连接到这些输出端,L9848将正确驱动它们以及提供正确的故障模式操作,无需其他输入。该装置切换可变负载工作温度范围内的电流。输出是MOSFET驱动器,以最小化Vdd电流要求。没有VBatt输入引脚,但是VBatt连接到高端输出的漏极。L9848当施加到输出漏极的电源电压在工作范围内时,符合所有要求的规格。对于施加在漏极上的电源电压低至6.8V,该部件是正常工作的,但它确实起作用不满足所有参数限制,即输出通电状态电压。

输出-通用特性

6个自配置输出(输出1-6)能够驱动白炽灯、感应负载(非PWMed)或偏向VBatt的电阻负载。这些输出通过SPI总线启用和禁用。每个这些输出具有短路电流限制,并具有“功能说明-热关机”中所述的过热保护。当高压侧配置输出在被指令接通时,电源电压将变为(VBatt-45V)的较小负电压。这是由于设计电路和MOSFET的跨导。当指令低侧配置输出时关闭在被命令打开后,输出电压将上升到内部齐纳钳位电压(40Vdc最小值)由于感应负载的反激。

–输出1-4

这四个输出可以用作高压侧或低压侧驱动。集成电流源上拉采用下拉方式正确锁定“空载”故障数据。这两种电流来源需要检测开路负载状态,因为这些输出自配置为高压侧或低压侧驱动器。

输出1-4(DRN1-4)的排水连接这些引脚连接到n沟道MOSFET晶体管的漏极。输出1-4(SRC1-4)的源连接这些引脚连接到n沟道MOSFET晶体管的源。

–输出5-6

这两个自配置输出可用于驱动高侧或低侧负载。除了这些输出由SPI总线控制,也可以通过IN5和IN6输入启用和禁用。IN5和IN6输入与SPI命令逻辑地“或”,以允许IN5-6输入或启动这些输出的SPI命令。在这些输出上使用IN5-6进行PWM控制应只能在非感应负载下进行。采用集成电流源上拉和下拉,以正确锁定“空载”故障数据。这两个电流源都需要检测一个开放的,因为这些输出自配置为高或低侧驱动器输出口5-6(DRN5-6)的排水连接这些引脚连接到n沟道MOSFET晶体管的漏极。

输出5-6(SRC5-6)的源连接

这些引脚连接到n沟道MOSFET晶体管的源。

–输出7-8

这两个输出(DRN7-8)是专用的低端驱动器。集成电流源下拉需要正确锁定“空载”故障数据。

主电源输入(VDD)

VDD输入是L9848的主电源。此电源用作所有its的电源逻辑电路和其他各种功能。请注意,如果L9848与正在运行的处理器连接在较低电压(例如3.0 VDC)下,连接到L9848的微处理器输入将从0摆动到5.0直流电。

离散输入(IN5-6)

这些输入允许在不使用SPI的情况下通过外部引脚启用输出5-6。一个逻辑“1”无论SPI命令寄存器的状态如何,输入都会启用相应的输出。逻辑“0”开启如果SPI命令寄存器没有命令该输出打开,这些输入将禁用相应的输出。如果仅通过SPI(内部下拉)控制输出,这些引脚可以保持“打开”。这些输入适用于脉冲宽度调制(PWMed)的非感应负载。这允许PWM控制没有使用SPI。TTL电平兼容的输入电压允许微处理器正常工作使用5.0V或3.0V的Vdd电源

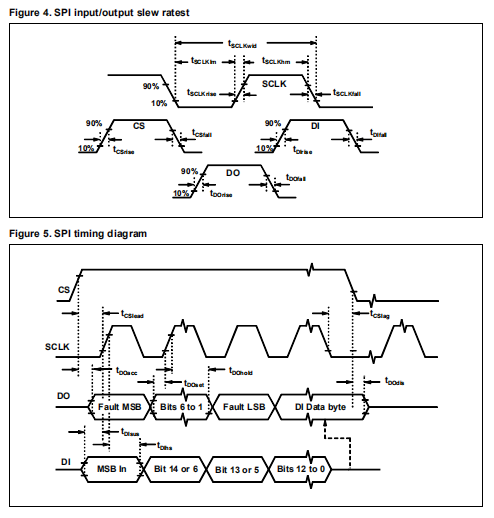

串行外设接口(SPI)

一种标准的串行外围接口,由串行时钟(SCLK)、数据输出(DO)、数据输入(DI)和芯片组成实现Select(CS)以允许访问L9848的内部寄存器。所有输出通过这个SPI。那个输入引脚CS、SCLK和DI具有TTL电平兼容的输入电压,允许正常工作来自使用5.0V或3.0V作为VDD电源的微处理器。L9848的设计允许多个L9848的“菊花链”进一步减少对控制器引脚的需求。

–串行数据输出(DO)

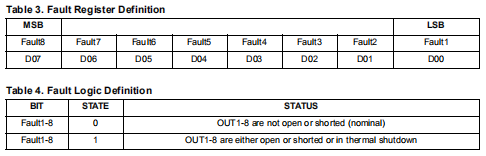

当CS为逻辑“0”(低)时,该输出引脚处于三态状态。当CS为逻辑“1”(高)时,该引脚总是将8位数据从故障寄存器传输到数字控制器。在前8位之后数据被发送到DO输出,然后依次发送刚刚接收到的数字数据(8个SCLK循环之前)在DI引脚上。DO输出继续发送8 SCLK延迟位从DI输入到CS最终从逻辑“1”转换到逻辑“0”的数据。是否更改数据在SCLK下降边缘后,状态为10ns或更晚。根据定义,MSB(表3)是一旦CS从逻辑“0”转换到逻辑“1”,DO和LSB上传输的字节是在DO上传输的字节的最后一位。

–串行数据输入(DI)

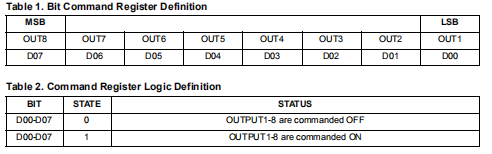

当CS高时,此输入从数字控制器获取数据。L9848接受8位数据流命令输出打开或关闭。根据定义,MSB(表1)是每个在DI上接收的字节,LSB是DI上接收到的每个字节的最后一位,一旦CS从逻辑“0”到逻辑“1”。

–芯片选择(CS)

这是芯片选择输入引脚。在CS的上升沿,DO引脚从三态切换到主动输出模式。当CS为高电平时,寄存器数据分别由DI和DO引脚在每个后续SCLK上移入和移出。在CS的下降沿,DO引脚切换回三态如果接收到有效的DI字节,则模式和故障寄存器将被“清除”。有效的DI字节定义如下:首先,接收到8位的倍数当CS降低时,第2个SCLK较低当SCLK低时,第三个电流SPI循环开始除非满足上述3个条件,否则故障数据不会被清除。SCLK转换必须在CS被解释为活动之前看到。为了有足够的时间重新加载故障寄存器,CS引脚必须保持低至少1μs,然后再次变高,然后开始移动故障数据在DO引脚上位出。CS有一个集成的故障滤波器,用于50ns或较短(即无故障数据和输出1-8启用状态将改变)。对于开路情况CS内部拉低至GND。

–串行时钟(SCLK)

这是用于同步串行数据传输的时钟信号输入。DI数据被转移到DI中在SCLK上升沿输入,在SCLK下降沿进行数据更改。

SPI DI输入命令寄存器

输入字节(8位)被路由到命令寄存器。表中给出了该命令寄存器的内容1和表2。附加的DI数据将继续缠绕在DO管脚上。如果CS在接收完当前字节后,这个刚刚发送的字节将被忽略

故障操作

故障诊断功能包括一个8位内部移位寄存器。通过比较源极或漏极电压与VDD电压,提供开路或短路负载检测。当输出连接为低压侧装置或高压侧装置被指令关闭,可检测到开路负载。当作为低压侧装置或高压侧装置连接的输出装置被指令接通短路负载时,可以检测到。这个如果输出1-8出现短路、开路或温度过高情况,则每个通道的故障位“设置”。该故障寄存器的内容如表3所示。每个单独通道的输出负载状态在中定义表4。如果开路和短路满足最小持续时间标准,则随后重新锁闭如果热故障在CS变为“低”后符合持续时间标准,则热故障将被重新锁定条件仍然存在。故障寄存器能够检测和锁定多个故障条件(在8个输出中)在清除故障标志之间发生的。所有故障将在芯片选择(CS)的下降沿清除。

初始故障寄存器SPI周期

在首次将VDD应用到L9848之后,在

初始SPI周期和所有后续周期的有效故障数据将从DO(故障位)中时钟输出。

“设置”的位表示哪个输出有故障。

–白炽灯输出

由于与

灯负载。例如,灯负载通道在一个SPI循环期间启用。大约

20ms-100ms后,需要一个SPI循环来读取正确的故障锁存数据,该数据将被清除

在那个SPI周期的CS下降边缘之后。

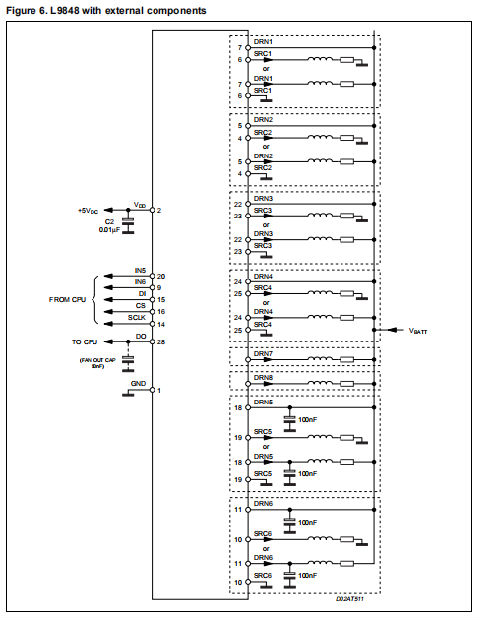

输出1-6的配置

每个输出的漏极和源引脚必须以以下两种配置之一连接(请参阅

图6a和图6b)。

–低端驱动程序

当在低端驱动器配置中连接输出1-6的任意组合时

适用输出(SRC1-6)必须接地。适用输出的漏极(DRN1-

6) 必须连接到负载的低端。

–高端驾驶员

当输出1-6的任何组合连接到高侧驱动配置中时

适用输出(DRN1-6)必须连接到VBatt。适用输出的来源

(SRC1-6)必须连接到负载的高压侧。

DRN1-6对负电压瞬变的敏感性

对于连接并用于高压侧驱动的任何输出,快速负瞬态转换率不会无意中发出POR(上电复位)或导致寄生闭锁发生。但在某些情况下

可能需要有一个10nF到100nF的陶瓷芯片电容器从漏极连接到GND以帮助

防止由于设备排水管上的非常快的负瞬态而导致问题的发生。

热关机

每8个输出都有独立的热保护电路,一旦局部n沟道MOSFET器件温度达到超温关机极限。由于启用和禁用温度水平的滞后性,故障通道将周期性地关闭和打开,直到出现故障条件被清除,环境温度充分降低或输出被命令关闭。一旦任何单个通道进入热关机状态,逻辑“1”被锁存到故障寄存器中,如果它满足热故障过滤器(注:不通过开路/短路故障过滤器)。注:由于L9848的设计,每个输出的热限制“可能”并不真正独立,如果一个输出短路,它可能会影响其他输出的操作(由于模具中的横向加热)。用户可能需要监视故障位定期地。如果一个故障位被“设置”为最后启用的输出,并且随后,其他启用输出的故障位开始被“设置”,用户将在100ms内发送两个SPI写入周期。第一个SPI写入周期将“清除”故障锁存。如果是多个在第二个SPI写入周期之后,会显示故障,这些故障很可能是热故障。然后用户将禁用此输出最近启用的。随后应询问故障寄存器,以验证其他已启用输出通道的正确操作。

充电泵使用

L9848为6个可配置输出通道中的每一个使用单独的电荷泵和振荡器来提供

低RDSON值当连接在高侧配置时,这些振荡器以非同步工作模式工作。这些电荷泵的频率范围设计为高于调幅收音机波段和低于8.0MHz,这样谐波就不会进入调频收音机波段。

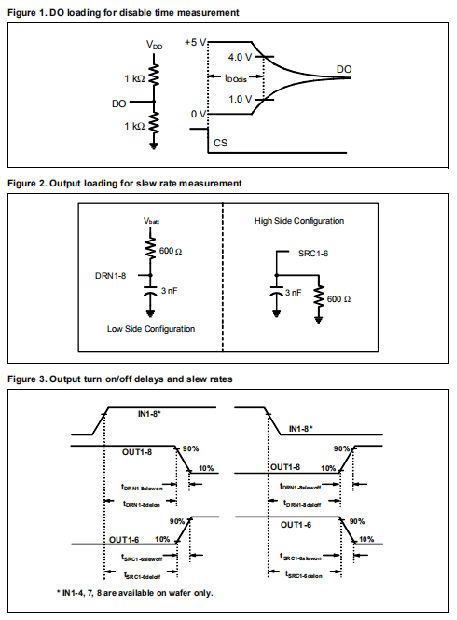

波形成形

所有输出(输出1-8)的开启和关闭转换速率都受到限制,以降低传导电磁兼容性车辆线束中的能量。在输出驱动过程中,开关电压的特性是线性的,没有间断状态转换。

POR寄存器初始化

如果VDD电源在0.3ms到3ms内从0增加到5VDC,L9848将唤醒。L9848有一个监测VDD电压的POR电路。当VDD电压大致达到4.1VDC,并保持在该跳闸水平以上至少20μs,命令和故障寄存器被“清除”。在VDD达到该跳闸电平之前,保证所有八个输出处于关闭状态。在发生有效POR且VDD电压低于有效高电平,达到所需量后时间,L9848的电源是完全控制的。没有输出会出现故障“开”,也没有错误的故障在DO输出上允许数据。

异常电压条件L9848在以下异常电压条件下仍能正常工作。

–倒车电池

直接施加或通过负载施加到带源引脚(SRC1-6)的漏极引脚(DRN1-6)接负载或接地(冷灯、螺线管等)。

–最大负瞬态

这会迫使输出的排水管或电源低于模块接地-20V。地面偏移量L9848接地和任何直接连接到高侧负载时底盘接地。如果驱动低侧负载,L9848接地和负载接地之间不会有偏移。此外,可能存在最大地差L9848接地和与之相连的任何其他模块之间的-0.5V至1.0V或±VAC(10-200赫兹)。

–失去地面操作

在L9848模块失去接地的情况下,任何输出都受到保护,以在电源仍然接通的情况下激活。