OPA171-Q1点击型号即可查看芯片规格书

OPA2171-Q1点击型号即可查看芯片规格书

OPA4171-Q1点击型号即可查看芯片规格书

特征

•适合汽车应用

•AEC-Q100测试指南,包括以下内容:

–设备温度1级:–40°C至+125°C环境工作温度

–设备HBM ESD分类级别:

–OPA171-Q1的3A级

–OPA2171-Q1的3A级

–2级OPA4171-Q1

–设备CDM ESD分类级别

–OPA171-Q1的C4A级

–OPA2171-Q1的C6级

–OPA4171-Q1的C6级

•电源范围:2.7至36 V,±1.35至±18 V

•低噪声:14 nV/√Hz

•低偏移漂移:±0.3μV/°C(典型值)

•RFI过滤输入

•输入范围包括负电源

•输入范围工作至正电源

•轨对轨输出

•增益带宽:3 MHz

•低静态电流:每个放大器475μA

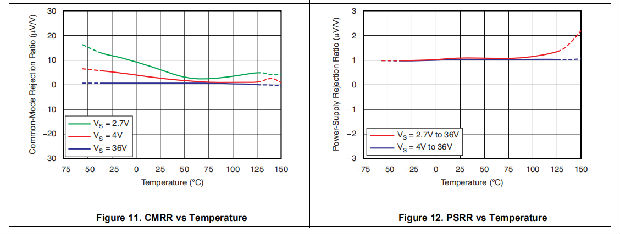

•高共模抑制:120 dB(典型值)

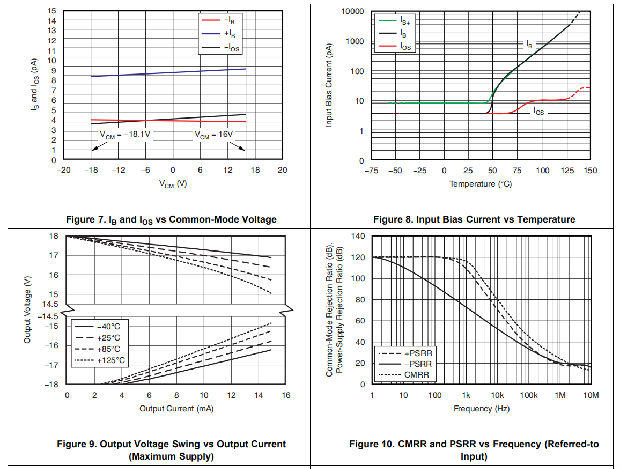

•低输入偏置电流:8 pA

•行业标准包:

–5针小外形晶体管SOT-23(DBV)封装

应用

•功率模块中的跟踪放大器

•商用电源

•传感器放大器

•桥式放大器

•温度测量

•应变计放大器

•精密积分器

•电池供电仪器

•测试设备

说明

OPA171-Q1系列器件是一种36V、单电源、低噪声运算放大器(运算放大器),能够在2.7伏(±1.35伏)到36伏(±18伏)的电源上工作。该器件采用微型封装,提供低偏移、低漂移和低静态电流带宽。单、双和四个版本都有相同的规格,以实现最大的设计灵活性。

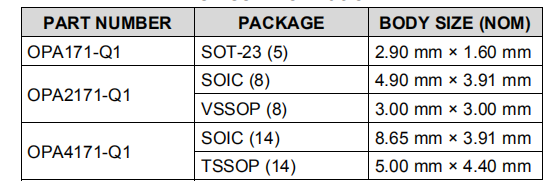

设备信息(1)

(1)、有关所有可用的软件包,请参阅数据表末尾的医嘱内容附录。

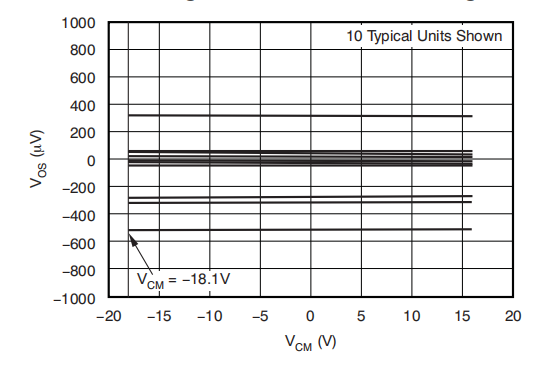

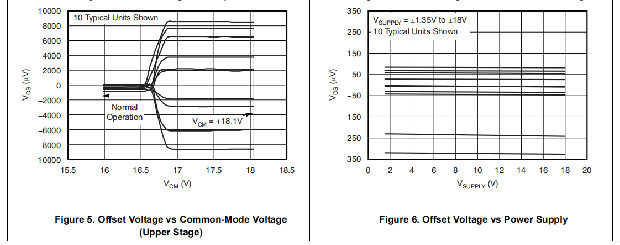

偏移电压与共模电压

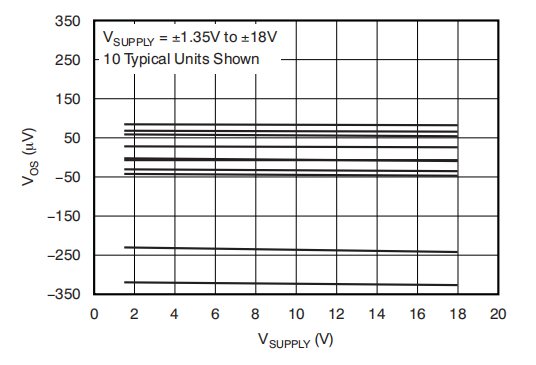

偏移电压与电源

与大多数只在一个电源电压下指定的运算放大器不同,OPAx171-Q1系列设备的电压范围为2.7至36 V。超出电源导轨的输入信号不会导致相位反转。OPAx171-Q1系列器件在电容负载高达300 pF时稳定。在正常运行期间,该输入可在负轨下100毫伏和顶轨2伏范围内工作。该装置可在超过顶部轨道的100 mV全轨对轨输入下运行,但在顶部轨道2 V范围内性能降低。

OPAx171-Q1运算放大器的规定温度为-40°C至+125°C。

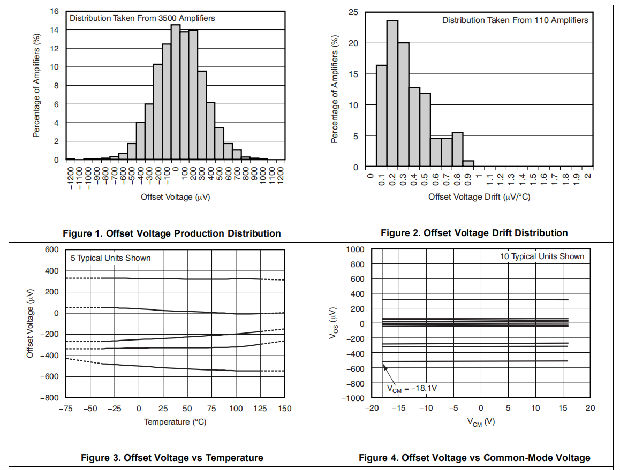

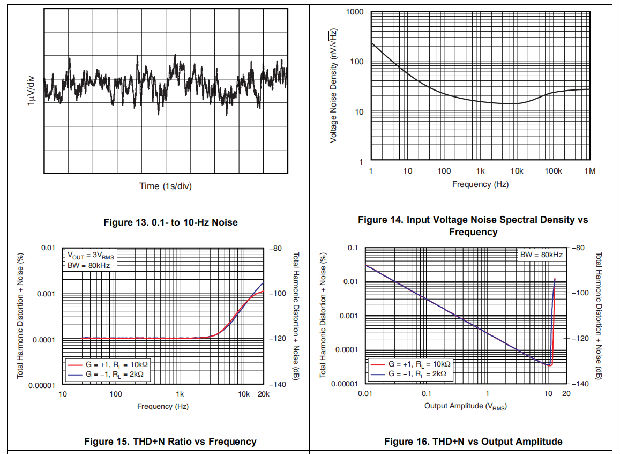

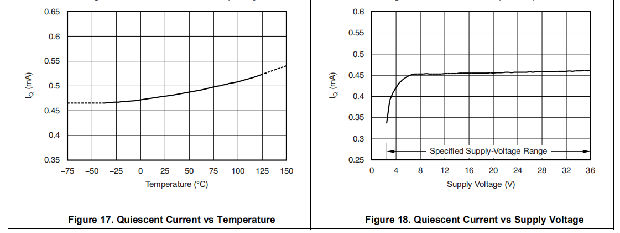

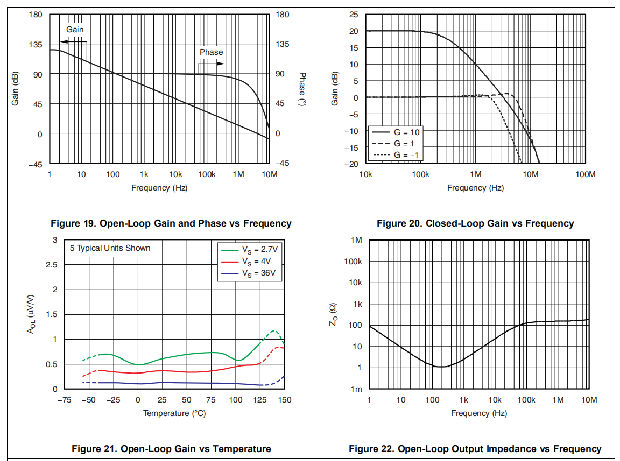

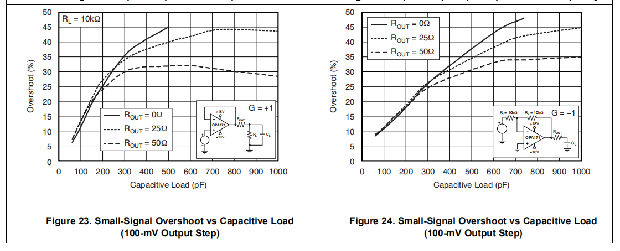

典型特征

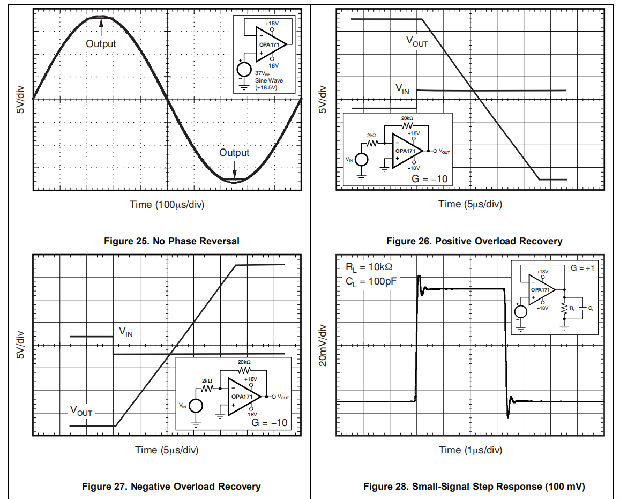

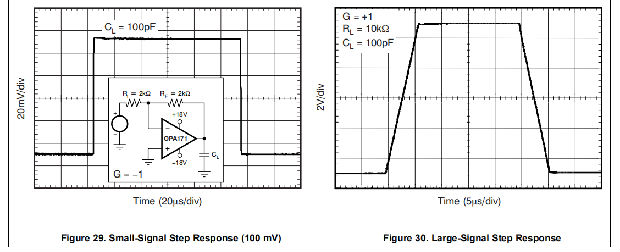

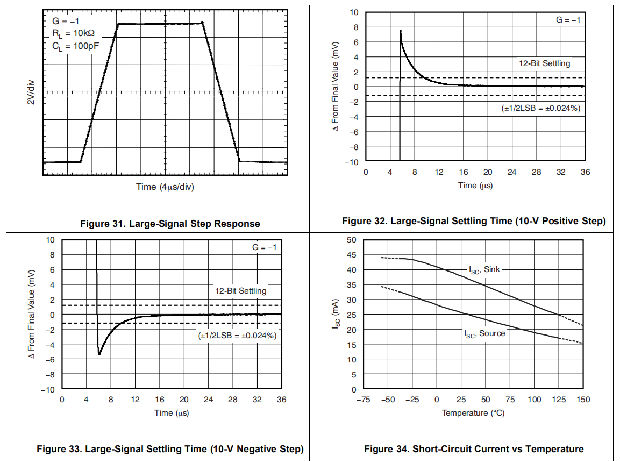

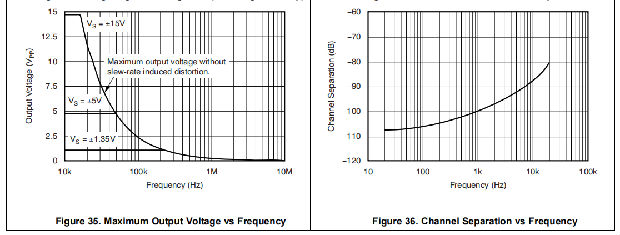

VS=±18 V,VCM=VS/2,RLOAD=10 kΩ,连接到VS/2,CL=100 pF,除非另有说明。

详细说明

概述

OPAx171-Q1系列运算放大器提供高整体性能,使其成为许多通用应用的理想选择。只有1.5μV/°C(最大值)的优良偏移漂移在整个温度范围内提供了极好的稳定性。此外,该设备提供了非常好的整体性能与高共模抑制比,电源抑制比,AOL和优越的THD。

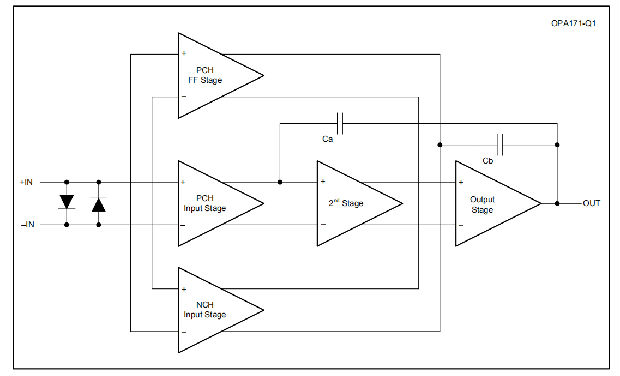

功能框图

特性描述

运行特性

OPAx171-Q1系列设备的工作电压为2.7至36 V(±1.35至±18 V)。许多规范适用于-40°C至+125°C。典型特性部分显示了与工作电压或温度相关的显著变化的参数。

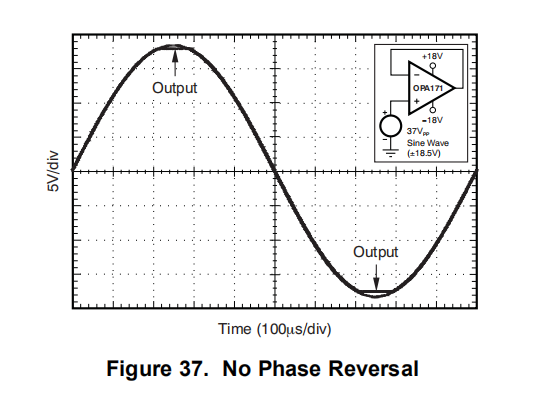

倒相保护

OPAx171-Q1系列设备具有内部相位反转保护。当输入被驱动超过其线性共模范围时,许多运算放大器都会出现相位反转。这种情况在非换向电路中最常见,当输入被驱动到超过规定的共模电压范围时,导致输出反向进入相反的轨道。OPAx171-Q1系列器件的输入可防止共模电压过高时的相位反转。相反,输出限制在适当的轨道上。图37显示了这种性能。

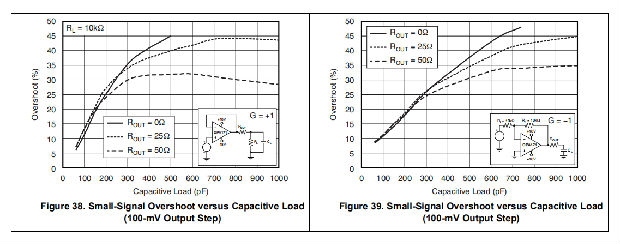

电容性负载及稳定性

OPAx171-Q1系列器件的动态特性已针对常见的操作条件进行了优化。低闭环增益和高容性负载的结合降低了放大器的相位裕度,并可能导致增益峰值或振荡。因此,较重的电容性负载必须与输出隔离。实现这种隔离的最简单方法是在输出端串联一个小电阻(例如,ROUT等于50Ω)。图38和图39显示了几个ROUT值的小信号超调与电容性负载的关系。

设备功能模式

共模电压范围

OPAx171-Q1系列器件的输入共模电压范围在负轨以下延伸100毫伏,在正常运行时在顶轨的2v范围内。

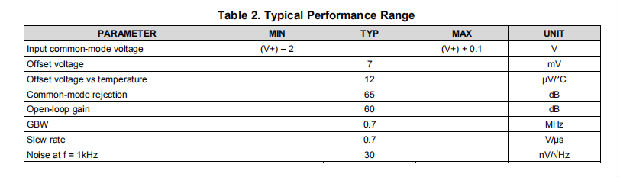

该装置可在顶部轨外100 mV的全轨对轨输入下运行,但在顶部轨2 V范围内性能降低。表2总结了该范围内的典型性能。

应用与实施

注意

以下应用章节中的信息不是TI组件规范的一部分,TI不保证其准确性或完整性。TI的客户负责确定组件的适用性。客户应验证和测试其设计实现,以确认系统功能。

申请信息

OPAx171-Q1运算放大器提供高整体性能,使其成为许多通用应用的理想选择。仅2μV/°C的良好偏移漂移在整个温度范围内提供了极好的稳定性。此外,该设备具有很高的CMRR、PSRR和AOL的整体性能。与所有放大器一样,噪声或高阻抗电源的应用需要离器件引脚近的去耦电容器。在大多数情况下,0.1-μF电容器就足够了。

电气过应力

设计者经常会问运算放大器承受过大电应力的能力。这些问题往往集中在设备输入上,但可能涉及电源电压引脚,甚至输出引脚。每一种不同的引脚功能都具有由特定半导体制造工艺和连接到引脚的特定电路的电压击穿特性决定的电应力极限。此外,内部静电放电(ESD)保护内置在这些电路中,以防止在产品装配之前和过程中发生意外的ESD事件。

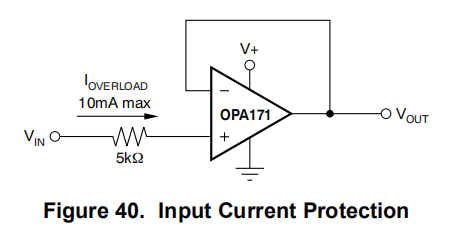

这些ESD保护二极管还提供电路内输入过驱动保护,只要电流限制在10毫安,如绝对最大额定值表所述。图40显示了如何将串联输入电阻添加到驱动输入端以限制输入电流。增加的电阻在放大器输入端产生热噪声,在对噪声敏感的应用中,其值应保持在最小值。

ESD事件产生一个持续时间短的高压脉冲,当它通过半导体器件放电时,该脉冲被转换成短时间的大电流脉冲。ESD保护电路设计用于在运算放大器核心周围提供电流通路,以防止其损坏。保护电路吸收的能量随后以热量的形式散失。

当运算放大器连接到电路中时,ESD保护组件将保持非活动状态,并且不会参与应用电路的操作。然而,当外加电压超过给定引脚的工作电压范围时,可能会出现这种情况。如果出现这种情况,则存在一些内部ESD保护电路可能偏压并传导电流的风险。任何这样的电流都是通过静电放电单元产生的,很少涉及到吸收装置。

如果电源吸收电流的能力不确定,可以在电源引脚上加上外部齐纳二极管。必须选择齐纳电压,使二极管在正常运行期间不会打开。

然而,齐纳电压应足够低,以便在电源引脚开始上升到高于安全工作电源电压水平时齐纳二极管导通。

典型应用

使用隔离电阻的电容负载驱动解决方案

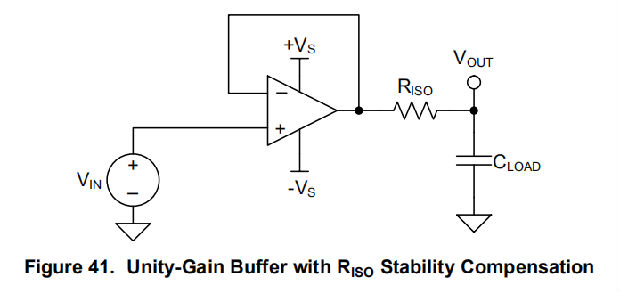

OPA171-Q1器件可用于电容性负载,如电缆屏蔽、参考缓冲器、MOSFET栅极和二极管。该电路使用隔离电阻(RISO)来稳定运算放大器的输出。RISO通过调整系统的开环增益来保证电路有足够的相位裕度。

设计要求

设计要求为:

•电源电压:30 V(±15 V)

•电容性负载:100 pF、1000 pF、0.01μF、0.1μF和1μF

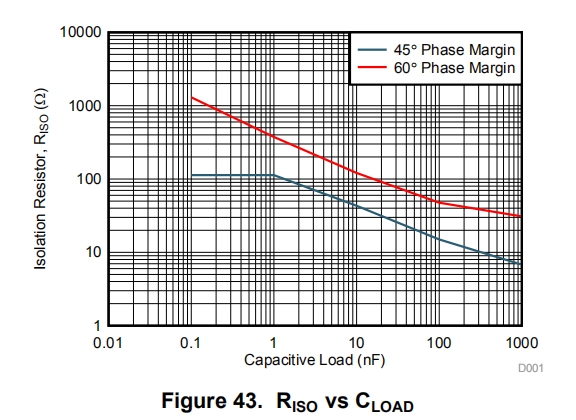

•相位裕度:45°和60°

详细设计程序

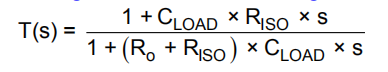

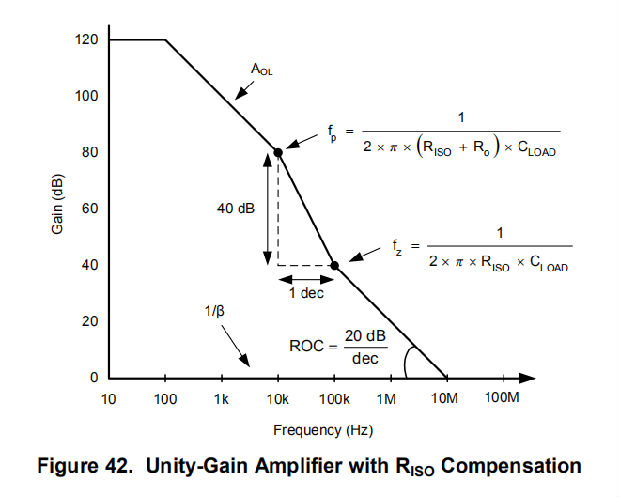

图42显示了驱动电容性负载的单位增益缓冲器。方程式1显示了图42中电路的传递函数。图42中没有显示运算放大器的开环输出电阻。

方程1中的传递函数有极点和零点。极点(fp)的频率由(Ro+RISO)和CLOAD确定。成分RISO和CLOAD决定了零点的频率(fz)。通过选择RISO,使开环增益(AOL)与1/β之间的闭合速率(ROC)为20db/decade,得到了一个稳定的系统。图42显示了这个概念。单位增益缓冲器的1/β曲线为0 dB。

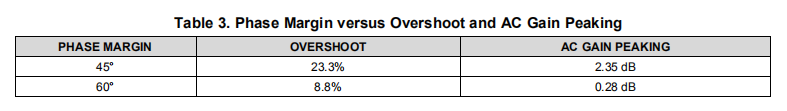

ROC稳定性分析是典型的模拟。分析的有效性取决于多因素,尤其是反渗透模型的精确性。除了模拟ROC,鲁棒稳定性分析还包括使用函数发生器、示波器、增益和相位分析仪测量电路的过冲百分比和交流增益峰值。然后根据这些测量值计算相位裕度。表3列出了与相位裕度45°和60°相对应的过冲百分比和交流增益峰值。有关此设计和其他可替代OPA171的详细信息,请参阅使用隔离电阻器的精密设计电容负载驱动解决方案(TIPD128)。

应用曲线

OPA171-Q1设备满足30 V的电源电压要求。对OPA171-Q1设备进行了各种电容性负载测试,并对RISO进行了调整,以实现表3所示的超调量。图43显示了测试结果。

电源建议

OPAx171-Q1系列设备规定在4.5 V至36 V(±2.25 V至±18 V)下运行;许多规范适用于-40°C至+125°C。在典型特性部分中给出了与工作电压或温度相关的显著变化的参数。

注意安全

大于40 V的电源电压可能会永久损坏设备;请参阅绝对最大额定值表。

将0.1-μF旁路电容器靠近电源引脚,以减少噪声或高阻抗电源的耦合误差。有关旁路电容器放置的详细信息,请参阅布局部分。

布局

布局指南

为获得设备的最佳运行性能,请使用良好的印刷电路板(PCB)布局实践,包括:

•噪声可以通过整个电路的电源引脚和运放本身传播到模拟电路中。旁路电容器用于通过提供模拟电路局部的低阻抗电源来降低耦合噪声。

–将低ESR、0.1-μF陶瓷旁路电容器连接在每个电源引脚和接地之间,并尽可能靠近设备。从V+到地的单旁路电容器适用于单电源应用。

•电路模拟和数字部分的单独接地是最简单和最有效的噪声抑制方法之一。多层印刷电路板上的一层或多层通常用于接地层。接地板有助于分配热量并减少电磁干扰噪音。确保在物理上分离数字和模拟接地,注意接地电流的流动。有关详细信息,请参阅SLOA089电路板布局技术。

•为了减少寄生耦合,输入轨迹应尽可能远离电源或输出轨迹。如果不可能使它们分开,最好垂直于敏感记录道,而不是与有噪声的记录道平行。

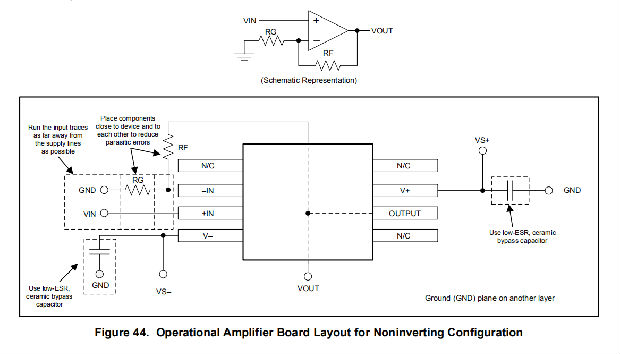

•将外部组件尽可能靠近设备。如图44所示,保持RF和RG接近逆变输入可以最大限度地减小寄生电容。

•输入记录道的长度应尽可能短。始终记住,输入轨迹是电路中最敏感的部分。

•考虑在关键线路周围设置一个驱动的低阻抗保护环。保护环可以显著降低附近不同电位的漏电电流。

布局示例