DAC2902点击型号即可查看芯片规格书

特征

●125MSPS更新率

●单电源:+3.3V或+5V

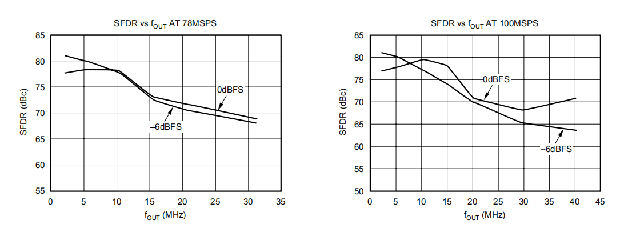

●高SFDR:70dB,fOUT=20MHz

●低故障:2pVs

●低功率:310mW

●内部参考

●断电模式:23mW

应用

●通讯:

-基站、无线局域网、无线局域网

-基带I/Q调制

●医疗/测试仪器

●任意波形发生器(ARB)

●直接数字合成(DDS)

说明

DAC2902是一个单片、12位、双通道、高速数模转换器(DAC),优化后可提供高动态性能,同时功耗仅为310mW。

DAC2902具有高达125MSPS的高更新率,提供了卓越的动态性能,并能够生成非常高的输出频率,适合“直接中频”应用。DAC2902已针对通信应用进行了优化,在通信应用中,处理分离速率I和Q数据,同时保持紧密的增益和偏移匹配。

每个DAC具有高阻抗差分电流输出,适用于单端或差分模拟输出配置。

DAC2902结合了高动态性能和高吞吐率,为各种波形合成应用创造了一个经济高效的解决方案:

•系列成员之间的引脚兼容性提供10位(DAC2900)、12位(DAC2902)和14位(DAC2904)分辨率。

•引脚兼容AD9765双DAC。

•增益匹配通常为满标度的0.5%,偏移匹配指定为最大0.02%。

•DAC2902采用先进的CMOS工艺;分段式结构将输出故障能量降至最低,并最大限度地提高动态性能。

•所有数字输入为+3.3V和+5V逻辑兼容。DAC2902具有内部参考电路,并允许使用外部参考。

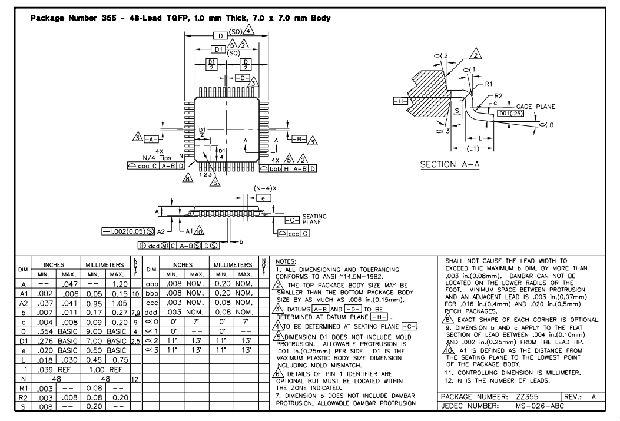

•DAC2902在TQFP-48封装中提供,并在扩展的工业温度范围-40°C至+85°C范围内指定。

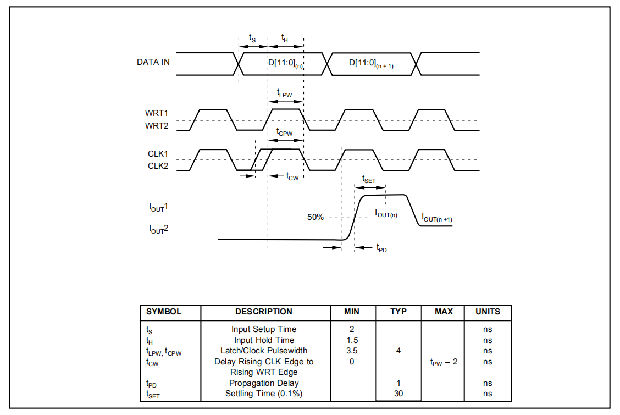

时序图

数字输入和定时

DAC2902的数据输入端口接受标准的正编码,数据位D11是最高有效位(MSB)。转换器输出支持高达125MSPS的时钟速率。最佳性能通常是通过对称的写入和时钟占空比实现的;但是,只要满足定时规范,占空比可能会有所不同。此外,设置和保持时间可在其规定的限制内选择。

DAC2902的所有数字输入都与CMOS兼容。逻辑阈值取决于应用的数字电源电压,因此它们被设置为大约一半的电源电压;Vth=+VD/2(±20%公差)。DAC2902设计用于在+3.0V至+5.5V的数字电源(+VD)下工作。

DAC2902内的两个转换器通道由两个独立的12位并行数据端口组成。每个DACchannel都由它自己的一组写(WRT1,WRT2)和时钟(CLK1,CLK2)输入控制。这里,WRT线控制信道输入锁存器,CLK线控制DAC锁存器。数据首先由WRT线的上升沿加载到输入锁存器中。该数据在WRT信号的下一个下降沿提供给DAC锁存器。在CLK线的下一个上升沿,DAC用新数据更新,模拟输出信号将相应地改变。DAC2902的双锁存结构为WRT和CLK信号生成一个定义的序列,用参数“tCW”表示。当CLK上升沿出现在WRT信号上升沿的同时或之前时,观察到正确的定时。将WRT和CLK线路连接在一起就可以满足这个条件。注意,所有的规格都是在WRT和CLK线路连接在一起的情况下测量的。

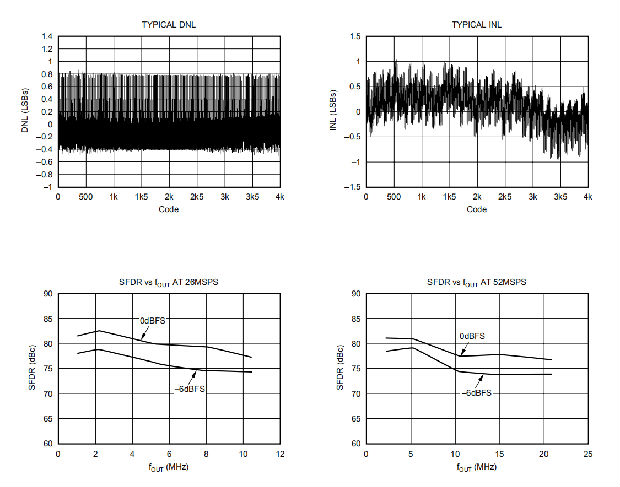

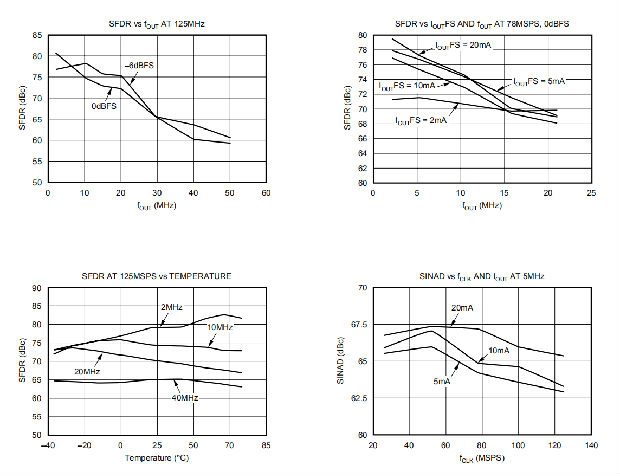

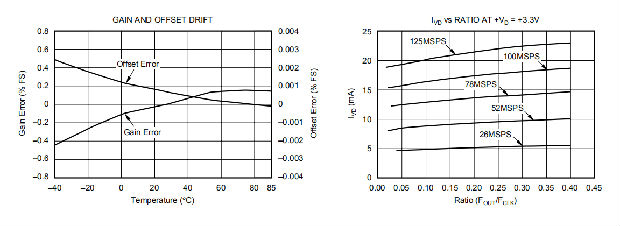

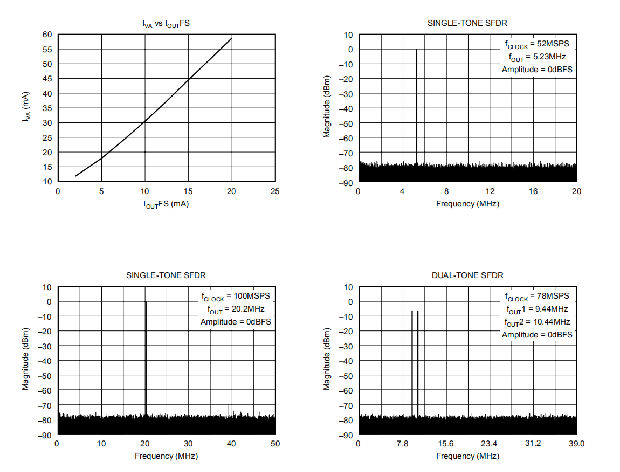

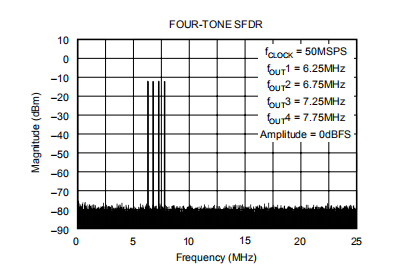

典型特征

TA=25°C,+VD=+3.3V,+VA=+5V,差动变压器耦合,IOUT=20mA,50y双端负载,SFDR高达Nyquist,除非另有说明。

申请信息

操作理论

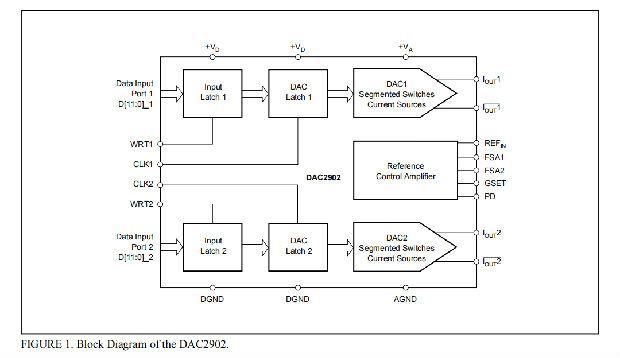

DAC2902的体系结构使用电流控制技术来实现快速切换和高更新率。单片DAC中的核心元件是一个分段电流源阵列,设计用于提供高达20mA的全刻度输出电流,如图1所示。内部解码器在每次DAC更新时寻址差分电流开关,并通过将所有电流转向输出求和节点IOUT或IOUT来形成相应的输出电流. 互补输出提供差分输出信号,与单端操作相比,通过减少偶数次谐波、共模信号(噪声)和双峰输出信号摆幅两倍来改善动态性能。

分段结构显著降低了故障能量,提高了动态性能(SFDR)和DNL。电流输出保持一个非常高的输出阻抗大于200ky。

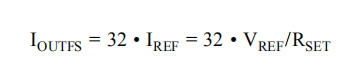

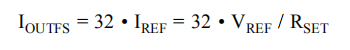

满标度输出电流由内部参考电压(约+1.25V)和外部电阻器RSET的比值决定。所得的IREF在内部乘以系数32,以产生有效的DAC输出电流,该电流的范围可从2mA到20mA,具体取决于RSET的值。

DAC2902分为数字部分和模拟部分,每个部分通过其自己的电源引脚供电。数字部分包括边缘触发的输入锁存器和解码器逻辑,而模拟部分包括电流源阵列及其相关开关和参考电路。

DAC传递函数

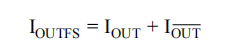

DAC2902中的每个DAC都有一个互补电流输出IOUT1和IOUT2。满标度输出电流IOUTFS是两个互补输出电流的总和:

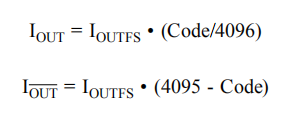

单个输出电流取决于DAC代码,可以表示为:

其中'Code'是DAC数据输入字的十进制表示。此外,IOUTFS是参考电流IREF的函数,它由参考电压和外部设置电阻RSET决定。

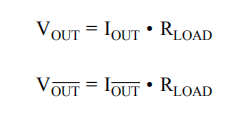

在大多数情况下,互补输出将驱动电阻负载或终端变压器。信号电压将根据以下条件在每个输出端产生:

负载电阻值受DAC2902输出符合性规范的限制。为了保持规定的线性性能,IOUT和IOUT的电压不应超过最大允许合规范围。

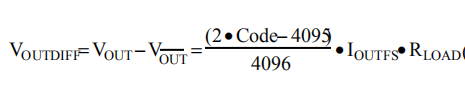

可以将两个单端输出电压组合起来,得出总差分输出摆幅:

模拟输出

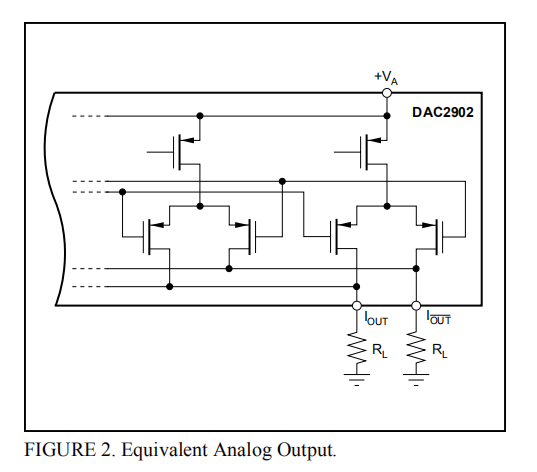

DAC2902提供两个互补电流输出,IOUT和IOUT。表示差分拓扑的模拟输出级的简化电路如图2所示。IOUT和IOUT的输出阻抗由差动开关、电流源和相关寄生电容并联组合而成。

在IOUT和IOUT两个输出端可能产生的信号电压摆幅受到正负顺应性的限制。负限值-1V是由CMOS工艺的击穿电压给出的,超过该限值将影响DAC2902的可靠性,甚至造成永久性损坏。满标度输出设置为20mA时,正合规性等于1.25V,使用+VA=5V的模拟电源工作。请注意,对于IOUTFS=2mA的选定输出电流,合规范围减小至1V左右。应注意,DAC2902的配置不超过合规范围,以避免失真性能和整体线性度下降。

当最大满标度输出信号限制在约0.5Vp-p时,通常可获得最佳失真性能。50Ω双端接负载和20mA满标度输出电流就是这种情况。通过选择合适的变压器,同时保持IOUT和IOUT的最佳电压水平,可以使各种负载适应DAC2902的输出。此外,将差分输出配置与变压器结合使用将有助于实现优异的失真性能。共模误差,如偶数阶harmon IC或噪声,可以大大减少。在高输出频率的情况下尤其如此。

对于那些需要最佳失真和噪声性能的应用,建议选择20mA的满标度输出。对于需要低功耗,但可以容忍稍有降低的性能水平的应用,可以考虑将满量程范围降低到2mA。

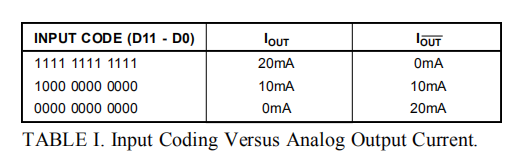

输出配置

DAC2902的电流输出允许多种配置,其中一些配置如表1所示。如前所述,利用转换器的差分输出将产生最佳的动态性能。这种差分输出电路可以由RF变压器或差分放大器配置组成。变压器配置是大多数交流耦合应用的理想配置,而运算放大器将适用于直流耦合配置。

对于需要单极输出电压的应用,可以考虑单端配置。将一个电阻从任一个输出端连接到接地,将输出电流转换为一个接地参考电压信号。为了通过保持虚拟接地来改善直流线性,可以考虑I-To-V或运放配置。

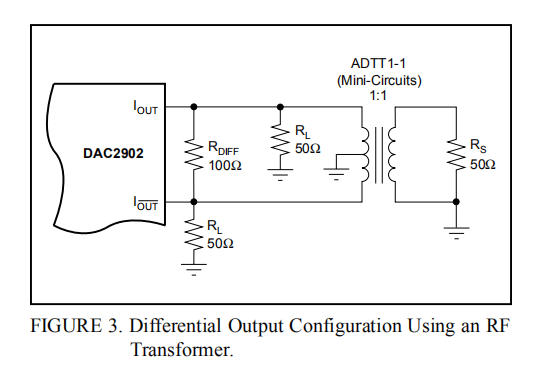

变压器差动

使用射频变压器提供了一种将差分输出信号转换为单端信号的便捷方法,同时实现了出色的动态性能(见图3)。应根据输出频谱和阻抗要求仔细选择合适的变压器。差分变压器配置的优点是显著减少共模信号,从而改善在较宽频率范围内的动态性能。此外,通过选择合适的阻抗比(绕组比),变压器可以提供最佳的阻抗匹配,同时控制转换器输出的柔顺电压。所示型号ADTT1-1(通过微型电路),具有1:1的比率,可用于连接DAC2902和50Ω负载。这将导致每个输出IOUT和IOUT的负载为25Ω。输出信号是交流耦合的,并且由于其磁耦合而固有的隔离。

如图3所示,变压器的中心抽头接地。这迫使电压在IOUT和IOUT上摆动以0V为中心。在这种情况下,两个电阻RL可替换为一个RDIFF,或完全省略。只有当所有部件彼此靠近,且驻波比不重要时,才应使用这种方法。可以实现从DAC输出到负载的完整功率传输,但应遵守输出符合性范围。或者,如果中心抽头未连接,信号摆动将位于RL•IOUTFS/2的中心。但是,在这种情况下,必须使用两个电阻器(RL)来为两个输出启用必要的直流电流。

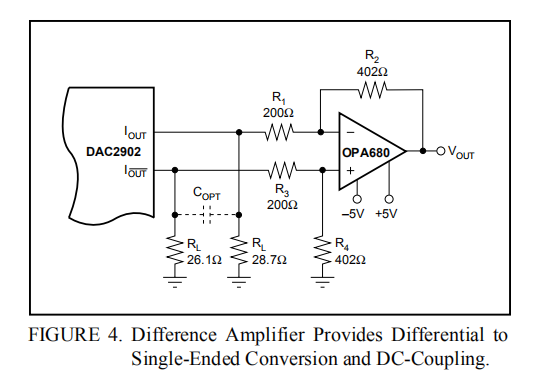

使用运算放大器的差分配置

如果应用需要直流耦合输出,可以考虑使用差分放大器,如图4所示。配置差分放大器需要四个差分反馈放大器作为运算放大器。在所示配置下,DAC2902在负载电阻器RL处生成0.5Vp-p的差分输出信号。选择显示的电阻值是为了使每个电流输出产生25Ω的对称负载,因为差分放大器的输入阻抗与电阻RL并联,因此应予以考虑。

OPA680配置为增益为2。因此,使用20mA满标度输出操作DAC2902将产生±1V的电压输出。这需要放大器在双电源(±5V)的情况下工作。电阻器的公差通常设置可实现共模抑制的极限。通过微调电阻R4可以得到改进。

这种配置通常比前面讨论的变压器解决方案提供更低的交流性能水平,因为放大器引入了另一个失真源。应根据其转换率、谐波失真和输出摆幅来选择合适的放大器能力。高-可以考虑使用像OPA680或OPA687这样的速度放大器。该电路的交流性能可以通过在输出端和输出端之间增加一个小电容器(CDIFF)来提高,如图4所示。这将引入一个实极点来创建一个低通滤波器,从而限制DAC的快速输出信号阶跃,否则可能会驱动放大器进入转换限制或过载状态;两者都会导致过度扭曲。这个差分放大器可以很容易地修改,以增加一个电平漂移的应用需要单端输出电压为单极性,即在0V和+2V之间摆动。

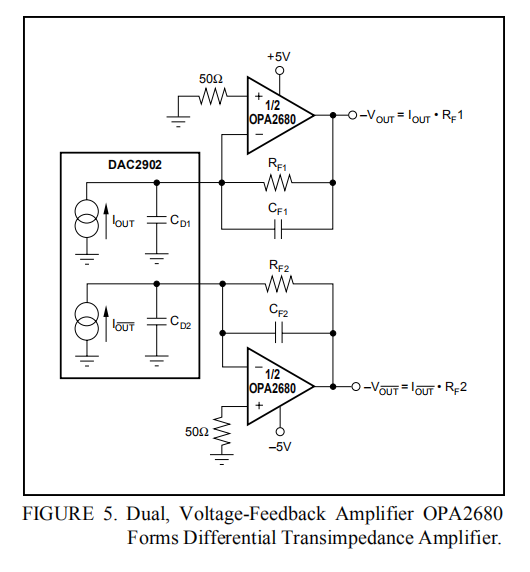

双跨阻输出配置

图5的电路示例显示了连接到双电压反馈运算放大器OPA2680的求和结的信号输出电流,该运算放大器被设置为跨阻级或“I-to-V转换器”。利用该电路,DAC的输出将保持在一个虚拟地上,使输出阻抗变化的影响最小化,从而获得最佳的直流线性度(INL)。如前所述,应注意不要将放大器驱动到转换速率限制中,并产生不必要的失真。

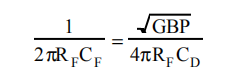

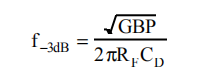

该电路的直流增益等于反馈电阻RF。在高频下,DAC输出阻抗(CD1,CD2)将在OPA2680的噪声增益中产生0,这可能导致闭环频率响应的峰值。增加射频增益以补偿峰值噪声。为了实现平坦的跨阻频率响应,每个反馈网络中的极点应设置为:

使用GBP=OPA的增益带宽积,

其转角频率f-3dB约为:

满标度输出电压仅由IOUTFS•RF的乘积定义,并具有负单极漂移。为了提高该电路的交流性能,需要考虑射频和/或输出功率的调整。此应用实例的进一步扩展可包括在OPA2680的输出处添加差分滤波器,然后添加变压器,以便转换为单端信号。

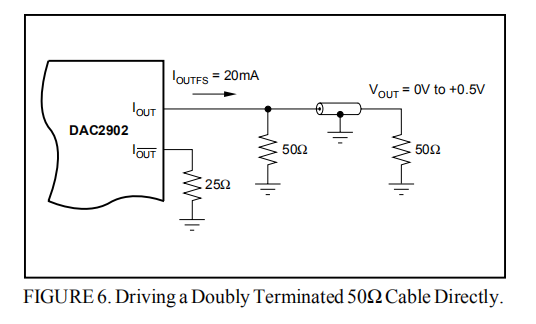

单端配置

使用一个连接到一个DAC输出的负载电阻,一个简单的电流电压转换可以完成。图6中的电路显示了连接到IOUT的50Ω电阻器,为进一步连接的50Ω电缆提供终端。因此,当标称输出电流为20mA时,DAC会在25Ω负载中产生0V到0.5V的总信号摆幅。

只要不超过输出符合范围,就可以选择不同的负载电阻值。此外,输出电流IOUTFS和负载电阻可以相互调节,以提供所需的输出信号摆幅和性能。

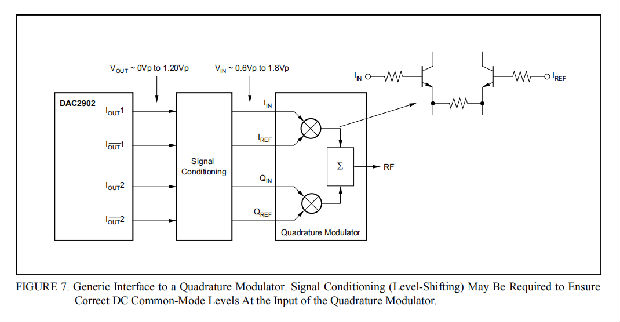

接口模拟正交调制器

双通道DAC的主要应用之一是用于数字通信的基带I和Q通道传输。在这个应用中,DAC之后是模拟正交调制器,用基带数据调制IF载波,如图7所示。通常,这些正交调制器的输入级由npn型晶体管组成,这些晶体管需要大于0.8V的直流偏压(基极)电压。宽的输出顺应范围(–10V到+1.25V)允许DAC2902和正交调制器之间的直接直流耦合。

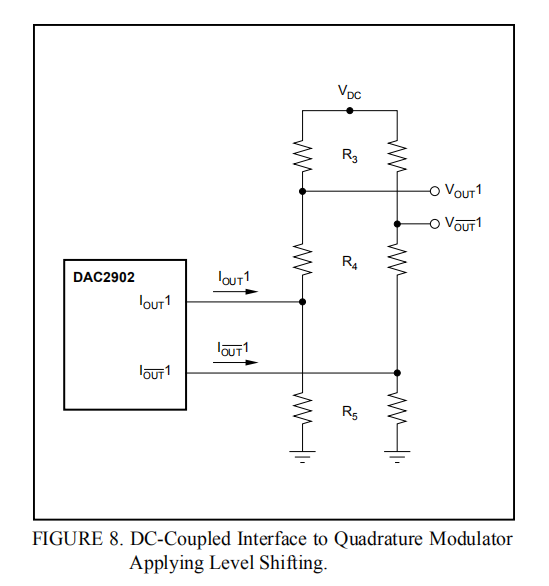

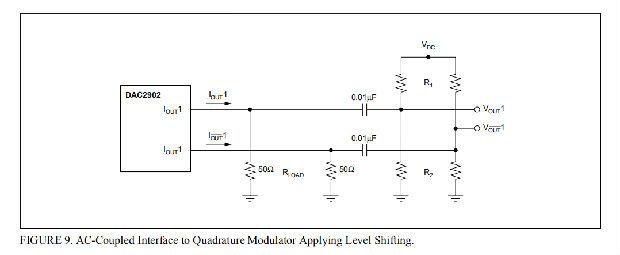

图8显示了一个使用精密电阻网络的直流耦合接口和直流电平偏移的示例。如图9所示,耦合接口的优点是调制器输入端的共模电平可以独立于DAC输出端的共模电平进行设置。

此外,在该装置中没有电压损失。

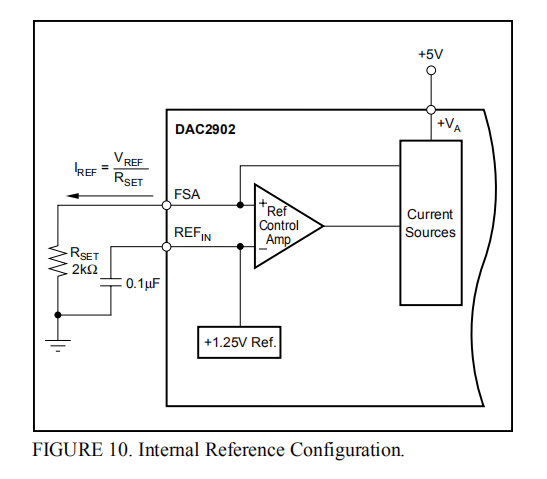

内部参考操作

DAC2902有一个片上参考电路,该电路包括1.25V带隙基准和两个控制放大器,每个DAC一个。DAC2902的满标度输出电流IOUTFS由参考电压确定,VREF,以及电阻RSET的值。IOUTF可通过以下公式计算:

外部电阻RSET连接到FSA引脚(满标度调整),见图10。参考控制放大器作为V-I转换器工作,产生参考电流,IREF,由VREF和RSET之比确定(如等式10所示)。满标度输出电流IOUTFS是由IREF乘以一个固定因子32得到的。

使用内部参考时,2kΩ电阻值会产生大约20mA的满标度输出。应考虑公差为1%或更高的电阻器。选择更高的值,输出电流可以从20mA调整到2mA。出于降低总功耗、优化失真性能或观察给定负载条件下的输出顺应性电压限制的原因,在低于20mA的输出电流下操作DAC2902可能是可取的。

建议使用0.1μF或更高的陶瓷芯片电容器绕过REFIN引脚。控制放大器内部补偿,其小信号带宽约为0.3MHz。

增益设置选项

DAC2902上的满标度输出电流可以通过两种方式设置:单独为两个DAC通道中的每一个通道设置,或者同时为两个通道设置。对于独立增益设置模式,GSET引脚(引脚42)必须低(即连接到AGND)。在此模式下,需要两个外部电阻器-一个RSET连接到FSA1引脚(引脚44),另一个连接到FSA2引脚(引脚41)。在这种配置中,用户能够灵活地独立地设置和调整每个DAC的满标度输出电流,允许补偿发射信号路径内其他地方可能的增益不匹配。

或者,使GSET引脚高(即连接到+VA),DAC2902将切换到同步增益设置模式。现在,两个DAC通道的满标度输出电流仅由连接到FSA1引脚的一个外部RSET电阻器决定。FSA2引脚处的电阻器可以被移除,但是这不是必需的,因为该引脚在这种模式下不起作用,并且电阻器对增益方程没有影响。推导正确RSET的公式保持不变,例如RSET=2ky将为两个dac产生20mA输出。

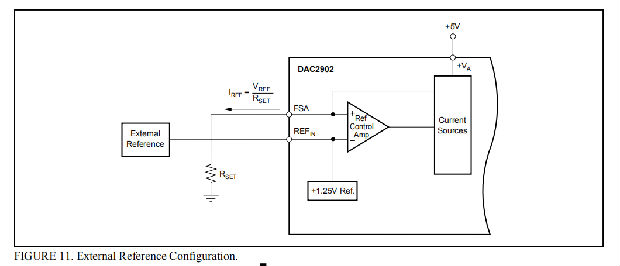

外部参考操作

只需在REFIN管脚上施加一个外部参考电压,就可以禁用内部参考,在本例中,该引脚起到输入的作用,如图11所示。对于需要更高精度和漂移性能的应用,或者增加动态增益控制能力,可以考虑使用外部基准。

虽然建议将0.1μF电容器用于内部基准,但对于外部基准操作,电容器是可选的。参考输入REFIN具有高输入阻抗(1MΩ),可以很容易地由各种电源驱动。注意,外部基准的电压范围应保持在参考输入的合规范围内(0.5V至1.25V)。

断电模式

DAC2902具有断电功能,可用于将总电源电流降低至6mA以下。在PD引脚上应用逻辑高将启动断电模式,而逻辑低则启用正常操作。当保持断开连接时,内部有源下拉电路将使转换器能够正常工作。

接地、解耦和布局信息

正确的接地和旁路、短引线长度和接地层的使用对于高频设计尤为重要。多层印刷电路板被推荐为最佳性能,因为它们具有显著的优点,如最小化接地阻抗、信号层与接地层分离等。

DAC2902为其模拟和数字电源和接地连接使用单独的引脚。去耦电容器的位置应确保模拟电源(+VA)旁路至模拟接地(AGND),数字电源旁路至数字接地(DGND)。在大多数情况下,每个电源引脚处的0.1μF陶瓷片电容器足以提供低阻抗去耦路径。请记住,它们的有效性在很大程度上取决于与单个电源和接地引脚的接近程度。因此,这些导线应尽可能靠近设备。只要可能,电容器应位于pc板背面每对电源/接地引脚的正下方。这种布局方法将最小化元件引线和PCB线路的寄生电感。

可根据需要在转换器附近添加与表面贴装钽电容器(1μF至4.7μF)的进一步电源去耦。

DAC2902的所有电源和接地连接都需要低噪声。建议使用利用独立电源和接地层的多层PCB。混合信号设计需要特别注意不同电源电流和信号轨迹的布线。一般来说,模拟电源和接地层只应延伸到模拟信号区域,如DAC输出信号和参考信号。数字电源和接地层必须限于覆盖数字电路的区域,包括连接到转换器的数字输入线以及时钟信号。模拟和数字接地层应在DAC下方的一个点连接在一起。这可以通过大约1/8英寸(3毫米)的短轨迹实现。

应通过使用宽PCB线路或平面向DAC2902供电。宽电流将提供较低的跟踪阻抗,进一步优化电源解耦。转换器的模拟和数字电源只能通过pc板的电源连接器连接在一起。在只有一个电源电压可用于为DAC供电的情况下,可以使用铁氧体磁珠和旁路电容器来创建LC滤波器。这将产生一个低噪声模拟电源电压,然后可以连接到DAC2902的+VA电源引脚。

在设计布局时,重要的是保持模拟信号轨迹与任何数字线路分离,以防止噪声耦合到模拟信号路径上。

包装图纸