DAC7551-Q1点击型号即可查看芯片规格书

特点

•适合汽车应用

•相对精度(INL):±0.35 LSB

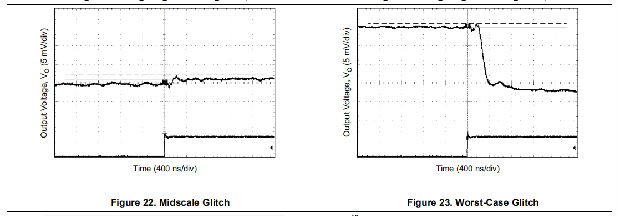

•超低故障能量:0.1 nV-s

•低功率运行:2.7 V时为100μA

•上电复位至零刻度

•电源:2.7-5.5-V单电源

•断电:2.7 V时为0.05μA

•12位线性度和单调性

•轨间电压输出

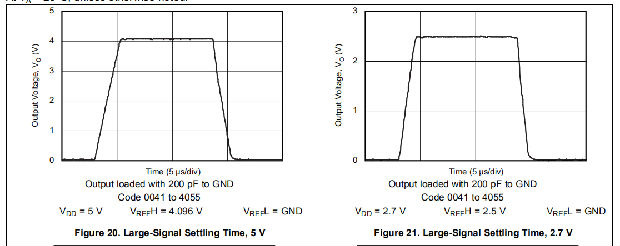

•沉降时间:5μs(最大)

•SPI兼容串行接口,带施密特触发器输入:最高50 MHz

•菊花链功能•异步硬件清晰到零刻度

•规定温度范围:–40°C至+105°C

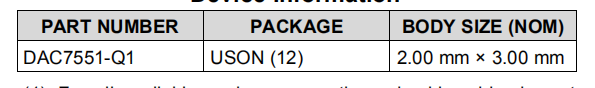

•小型,2-mm×3-mm,12引线USON封装

•Z-Suffix提供改进的分层

应用

•便携式电池供电仪器

•数字增益和偏移调整

•可编程电压和电流源

•可编程衰减器

•工业过程控制

•ADAS雷达应用

•碰撞警告

•盲点检测

说明

DAC7551-Q1器件是一种单通道、电压输出的数模转换器(DAC),具有卓越的线性度和单调性,以及将故障能量最小化的专有结构。低功耗DAC7551-Q1设备可从单个2.7伏到5.5伏电源供电。DAC7551-Q1输出放大器可驱动2-kΩ、200 pF的轨对轨负载,稳定时间为5μs。输出范围使用外部参考电压设置。

3线串行接口以高达50兆赫的时钟频率工作,并与SPI兼容™,QSPI™、microwire和DSP接口标准。该设备包含一个加电复位(POR)电路,以确保DAC输出功率高达0 V,并保持在该电压下,直到对该设备进行有效的写入循环。该设备具有断电功能,可将设备的电流消耗降低到2μa以下。

DAC7551-Q1设备体积小、功耗低,非常适合电池操作的便携式应用。5v时的功耗通常为0.5mw,3v时为0.23mw,在断电模式下功耗降低到1μW。

DAC7551-Q1设备采用12针USON封装,规定温度为-40°C至+105°C。与标准设备相比,Z后缀可减少分层。

设备信息

(1)、有关所有可用的软件包,请参阅数据表末尾的订购附录。

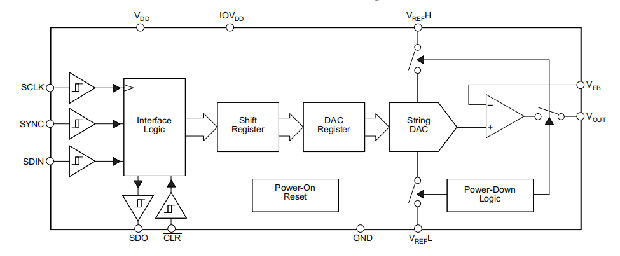

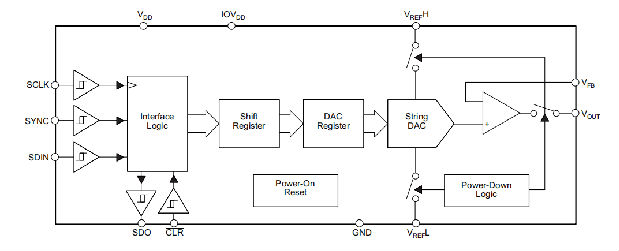

功能框图

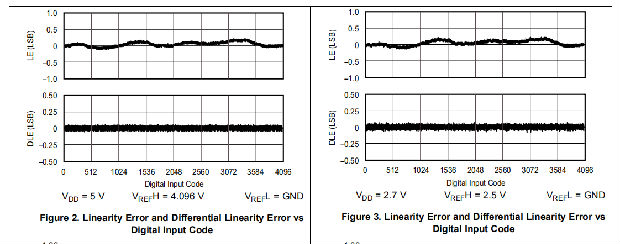

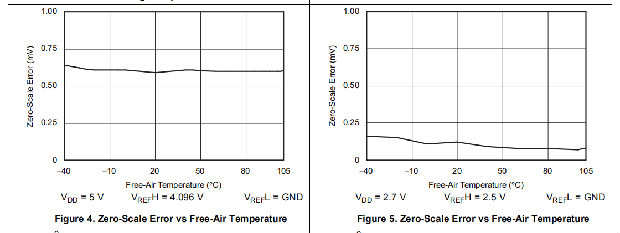

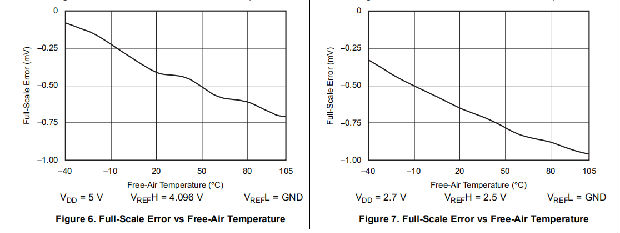

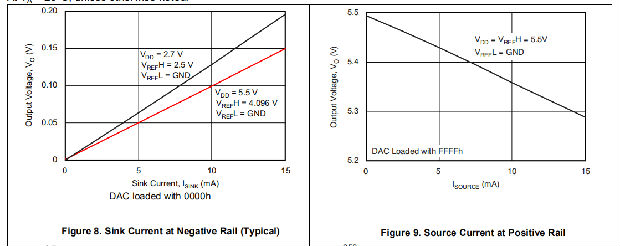

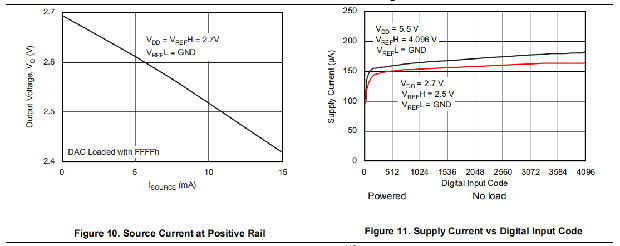

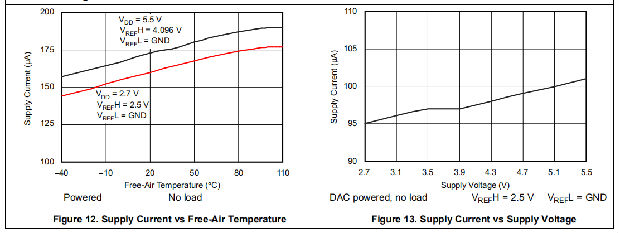

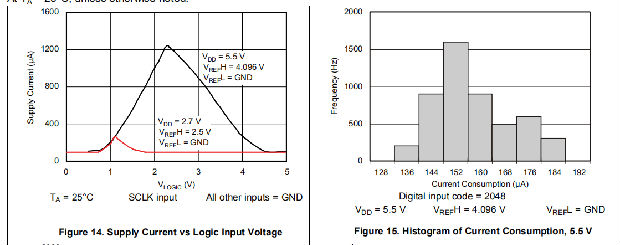

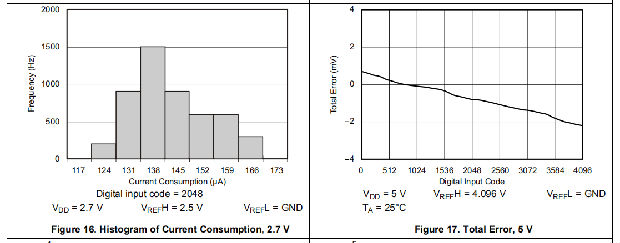

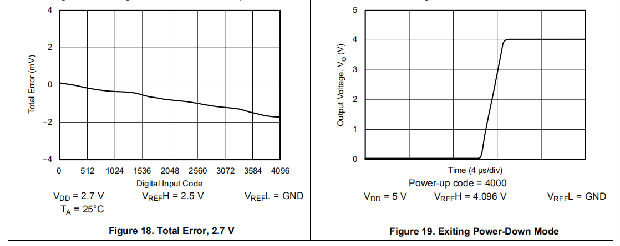

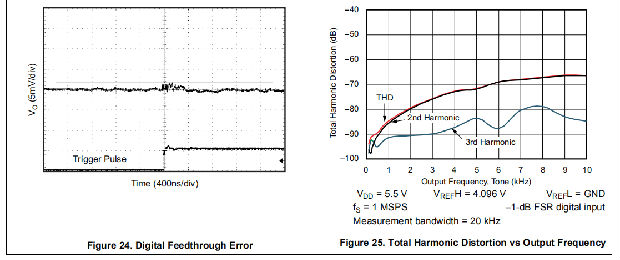

典型特征

TA=25°C时,除非另有说明。

详细说明

概述

DAC7551-Q1设备是一个12位电阻串数模转换器(DAC)。无缓冲外部参考输入允许正电压参考低至0.25 V,高达VDD。放大器反馈输入在负载点有更好的直流精度。该设备通过16位字三线串行外围接口(SPI)控制,最高可达50兆赫,并可选择菊花链多个设备。异步清除功能和断电功能允许软件控制复位和低功耗。一个独立的逻辑电源输入意味着该设备可以在广泛的电源电压范围内与不同的逻辑系列一起使用。

功能框图

特性描述

数模转换器

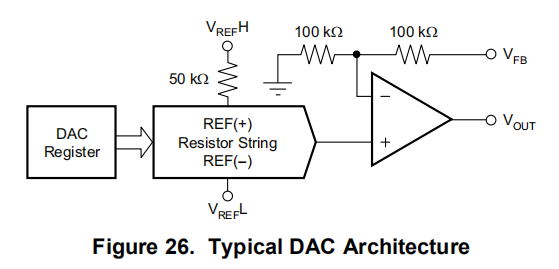

DAC7551-Q1器件的结构由一个串DAC和一个输出缓冲放大器组成。图26显示了DAC体系结构的通用框图。

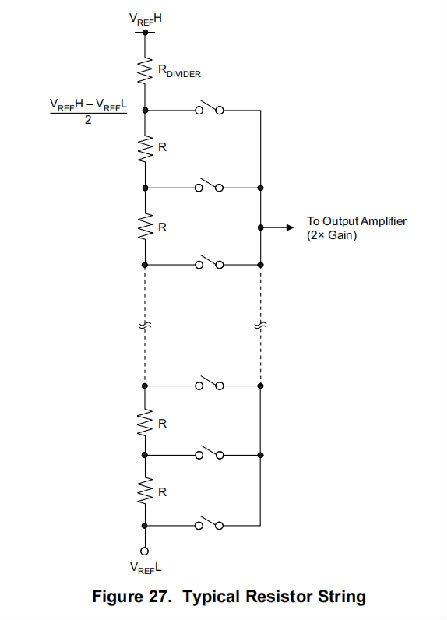

DAC7551-Q1器件的输入编码是无符号二进制,它给出了理想的输出电压,如等式1所示。

其中:

•D是加载到DAC寄存器的二进制代码的十进制等效值,范围从0到4095。

电阻串

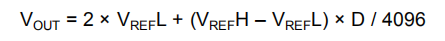

图27显示了电阻串部分。这个部分只是一个电阻串,每个电阻值为R。加载到DAC寄存器的数字代码决定在串上的哪个节点上,电压被分接到输出放大器中。通过关闭一个连接到放大器的开关,电压被分接。DAC的输出是单调的,因为它是一串电阻。

输出缓冲放大器

输出缓冲放大器能够在输出端产生轨对轨电压,提供0 V到VDD的输出范围。该放大器能够驱动2kΩ的负载,并对地高达1000pf。图8、图9和图10显示了输出放大器的汇和源能力。在输出空载的情况下,转换速率为1.8v/μs,半刻度稳定时间为3μs。

DAC外部参考输入

DAC7551-Q1设备包含无缓冲的VREFH和VREFL参考输入。VREFH参考电压可低至0.25V,高达VDD,因为没有任何参考放大器的净空和脚部空间限制。

建议在外部电路中使用缓冲基准(例如,REF3140装置)。输入阻抗通常为100kΩ。

放大器检测输入

DAC7551-Q1设备包含一个放大器反馈输入引脚VFB。对于电压输出操作,VFB必须外部连接到VOUT。对于直流点,应作更准确的直流连接。VFB引脚也适用于各种应用,包括数字控制的电流源。反馈输入引脚通过100-kΩ电阻器内部连接到DAC放大器负极输入端子。放大器负极输入端子通过另一个100-kΩ电阻器内部接地(见图26)。这些连接形成了一个增益为2的非互易放大器配置。总增益保持为1,因为电阻串有除以2的配置。在VFB针脚处看到的接地电阻约为200 kΩ。

上电复位

通电时,清除所有寄存器,并用零标度电压更新DAC信道。在写入有效数据之前,DAC输出保持此状态。此设置在设备通电时了解DAC输出状态非常重要的应用程序中特别有用。为避免开启ESD保护装置,应在任何其他引脚(如VREFH)升高之前应用VDD和IOVDD。VDD和IOVDD的加电顺序无关。因此,IOVDD可以在VDD之前提出,或者反过来。

断电

DAC7551-Q1设备具有灵活的断电功能。在断电状态下,用户可以灵活地选择DAC的输出阻抗。在断电操作期间,DAC可以具有1kΩ、100kΩ或Hi-Z输出对地阻抗。

异步清除

在CLR引脚降低后,DAC7551-Q1输出立即异步设置为零标度电压。CLR信号重置所有内部寄存器,因此其功能类似于上电复位。DAC7551-Q1设备在同步信号的第一个上升沿进行更新,该信号发生在CLR引脚回到高电平之后。

IOVDD和电平变换器

DAC7551-Q1器件可用于需要大范围电源电压的不同逻辑系列。为了启用这个有用的功能,IOVDD引脚必须连接到系统的逻辑电源电压。所有的DAC7551-Q1数字输入和输出引脚都配有电平转换电路。输入引脚上的电平移位器确保外部逻辑高压转换为内部逻辑高压,无需额外的功耗。类似地,SDO管脚的电平移位器将内部逻辑高电压(VDD)转换为外部逻辑高电平(IOVDD)。对于单电源操作,IOVDD引脚可连接至VDD引脚。

积分和微分线性度

DAC7551-Q1器件采用精密薄膜电阻,提供卓越的线性度和单调性。积分线性误差通常在±0.35 LSBs内,微分线性误差通常在±0.08 LSBs内。

故障能量

DAC7551-Q1设备采用专有架构,最大限度地减少故障能量。码对码的小故障是如此之低,以至于它们通常隐藏在宽带噪声中,并且不容易被检测出来。这个DAC7551-Q1故障通常低于0.1 nV-s。这种低故障能量比工业替代品提高了10倍以上。

设备功能模式

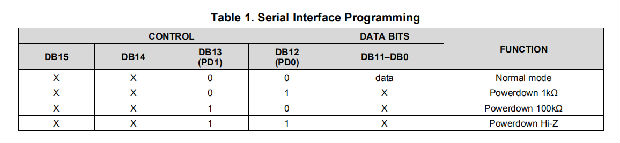

DAC7551-Q1设备使用四种操作模式。通过在控制寄存器中设置位PD0(DB13)和PD1(DB14),可以访问这些模式。表1显示了如何使用数据位PD0(DB13)和PD1(DB14)来控制操作模式。DAC7551-Q1设备将断电情况视为数据;所有操作模式对断电仍然有效。可以向系统中的所有DAC7551-Q1设备广播断电条件。关闭一个通道并更新其他通道上的数据也是可能的。此外,还可以写入断电的DAC信道的DAC寄存器或缓冲器。当DAC通电时,DAC包含此新值。

当PD0和PD1位都设置为0时,设备正常工作,2.7 V下的典型消耗为100μA。对于三种断电模式,电源电流在2.7 V时降至0.05μA。如表1所示,有三种不同的断电选项。VOUT引脚可以通过1-kΩ电阻或100-kΩ电阻内部连接到GND,也可以是开路的(High-Z)。换句话说,DB14和DB13=11表示所选信道具有高Z输出阻抗的断电条件。DB14和DB13=01和10分别代表1-kΩ和100-kΩ输出阻抗的断电条件。

编程

串行接口

DAC7551-Q1设备通过多功能3线串行接口控制,该接口以高达50 MHz的时钟速率工作,并与SPI、QSPI、Microwire和DSP接口标准兼容。

16位字和输入移位寄存器

输入移位寄存器的宽度为16位。在串行时钟输入SCLK的控制下,DAC数据以16位字的形式加载到设备中,如图1所示。表1中列出的16位字由4个控制位和12位DAC数据组成。数据格式为直接二进制,所有0对应0-V输出,所有1对应满标度输出(VREF–1 LSB)。数据首先加载MSB(位15),其中前两位(DB15和DB14)是不重要的位。位13和位12(DB13和DB12)确定正常模式操作或断电模式(见表1)。

同步输入是一个电平触发输入,用作帧同步信号和芯片启用。数据只能在同步管脚低的情况下传输到设备中。要开始串行数据传输,同步引脚应取低,观察最小同步到SCLK下降沿设置时间t4。同步引脚变低后,串行数据被转移到SCLK下降沿上的设备输入移位寄存器中,持续16个时钟脉冲。

在同步管脚变低后,SPI被启用,数据被连续地转移到SCLK输入的每个下降沿的移位寄存器中。当同步管脚被调高时,存储在移位寄存器中的最后16位被锁存到DAC寄存器中,并且DAC更新。

菊花链操作

菊花链操作用于更新同步输入上升沿上的串行连接设备。

只要同步引脚为高电平,SDO引脚就处于高阻抗状态。当同步引脚降低时,内部移位寄存器的输出与SDO引脚相连。只要同步引脚为低电平,SDO引脚就以16周期延迟复制SDIN信号。为了支持菊花链中的多个设备,SCLK和同步信号在所有设备之间共享,并且一个DAC7551-Q1设备的SDO引脚应该绑定到下一个DAC7551-Q1设备的SDIN引脚。对于这种菊花链中的n个设备,需要16n个SCLK周期来移动整个输入数据流。在接收到16n个SCLK下降沿之后,在下降同步信号之后,数据流变得完整,同步管脚可以被调高以同时更新n个设备。SDO操作的最大SCLK速度为10 MHz。

在菊花链模式下,建议在SDO输出引脚上使用一个弱下拉电阻器,该电阻为链中的下一个设备提供SDIN数据。对于独立操作,最大时钟速度为50 MHz。对于菊花链操作,最大时钟速度为10 MHz。

应用与实施

注意

以下应用章节中的信息不是TI组件规范的一部分,TI不保证其准确性或完整性。TI的客户负责确定组件的适用性。客户应验证和测试其设计实现,以确认系统功能。

申请信息

波形生成

由于DAC7551-Q1器件具有优异的线性度和低故障,因此该器件非常适合于波形生成(从直流到10kHz)。DAC7551-Q1大信号稳定时间为5μs,支持200ksps的更新速率。然而,如果要生成的波形由连续DAC更新之间的小电压阶跃组成,则更新速率可以超过1msps。为了获得高动态范围,建议使用REF3140装置(4.096V)或REF02装置(5V)来产生参考电压。

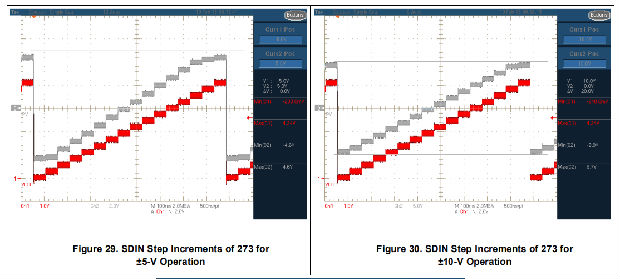

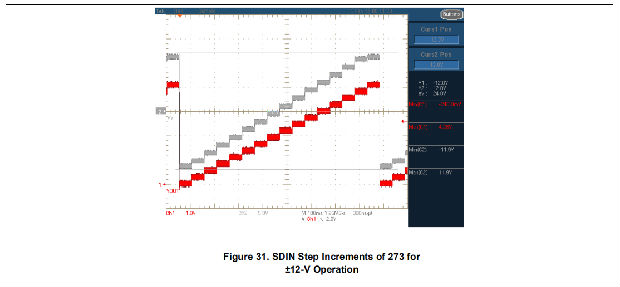

产生±5-V、±10-V和±12-V输出,用于精密工业控制

工业控制应用需要多个反馈回路,包括传感器、模数转换器(ADC)、微控制器(MCU)、DAC和执行器。环路精度和环路速度是此类控制回路的两个重要参数。

回路精度

DAC偏移、增益和积分线性误差不是决定环路精度的因素。只要在单调数模转换器的传输曲线中存在一个电压,环路就可以找到该电压并加以调整。另一方面,DAC分辨率和微分线性度确实决定了环路的精度,因为每个DAC步骤都决定了环路可以产生的最小增量变化。DNL误差小于–1 LSB(非单调性)会导致环路不稳定。DNL误差大于1 LSB意味着不必要的大电压阶跃和错过的电压目标。当DNL误差较大时,回路将失去稳定性、分辨率和精度。DAC755x器件具有12位保证的单调性和±0.08-LSB的典型DNL误差,是精密控制回路的最佳选择。

环路速度

许多因素决定了控制回路的速度,如ADC转换时间、MCU速度和DAC设置时间。通常,ADC转换时间和MCU计算时间是控制环路时间常数的两个主要因素。由于ADC转换时间通常超过DAC转换时间,所以DAC的稳定时间很少是主要因素。DAC偏移、增益和线性误差只能在启动过程中减慢环路速度。当环路达到稳态运行时,这些误差不会进一步影响环路速度。根据环路传输函数的振铃特性,DAC故障也会减慢环路速度。DAC7551-Q1具有1-MSPS(小信号)最大数据更新率,可支持高速控制回路。DAC7551-Q1器件的超低故障能量显著提高了环路稳定性和环路稳定时间。

典型应用

产生工业电压范围

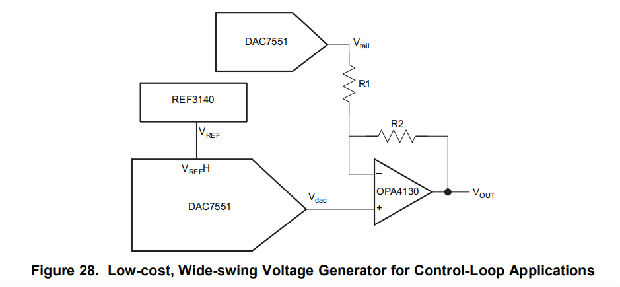

对于控制回路应用,DAC增益和偏移误差不是重要参数。这种考虑可以用来降低高压控制电路设计中的微调和校准成本。使用四路运算放大器(OPA4130)和电压基准(REF3140),DAC7551-Q1可以产生控制回路所需的宽电压波动。

设计要求

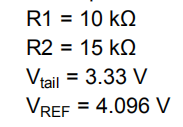

对于±5-V操作:

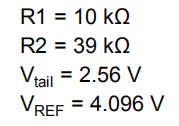

对于±10-V操作:

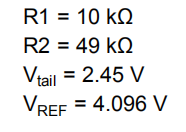

对于±12-V操作:

详细设计程序

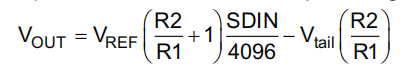

使用方程式2计算配置的输出电压。

固定的R1和R2电阻可用于粗略设置方程第一项所需的增益。当R2和R1将增益设置为包括一些最小的超量程增益时,可以使用单个DAC7551-Q1设备来设置所需的偏移电压。残余误差不是环路精度的问题,因为偏移和增益误差是可以容忍的。一个DAC7551-Q1设备可以提供Vtail电压,而另外四个DAC7551Q1设备可以提供Vdac电压以产生四个高压输出。一个SPI足以控制菊花链配置中的所有五个DAC7551-Q1设备。

应用曲线

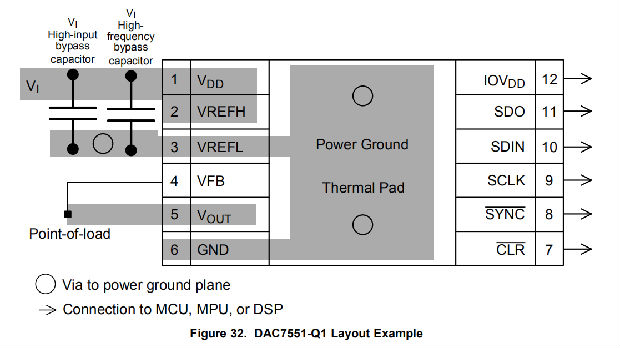

电源建议

施加在VDD引脚上的电源应调节良好,噪音低。开关电源和DC-DC变换器的输出电压经常出现高频故障或尖峰。此外,数字元件可以产生与内部逻辑开关状态类似的高频尖峰。这种噪声可以很容易地通过电源连接和模拟输出之间的各种路径耦合到DAC输出电压中。与GND连接一样,VDD引脚应连接到与数字逻辑连接分离的迹线电源平面,直到它们在电源入口点连接。此外,强烈建议使用1-μF和10-μF电容器以及0.1-μF旁路电容器。在某些情况下,可能需要额外的旁路,例如100μF电解电容器,甚至是由电感器和电容器组成的Pi滤波器。这些旁路方法都是为低通滤波电源和消除高频噪声而设计的。

布局

布局指南

一个精密的模拟元件需要仔细的布局,足够的旁路,以及干净、调节良好的电源。DAC7551-Q1设备提供单电源操作,通常与数字逻辑、微控制器、微处理器、数字信号处理器或组合使用。设计中的数字逻辑越多,开关速度越高,就越难防止输出端出现数字噪声。由于DAC7551-Q1设备的单个接地引脚,所有回路电流(包括DAC的数字和模拟回路电流)必须流经一个单点。理想情况下,GND应直接连接到模拟接地层。该平面应与数字部件的接地连接分开,直到这些部件在系统的电源入口连接。

布局示例