特征

•14位分辨率

•2.4-GSPS最大更新速率数模转换器

•双差分输入端口

–偶数/奇数解复用数据

–每个端口最多1.2-GSPS,总共2.4-GSPS

–双14位输入+1个参考位

–DDR输出时钟

–与参考位同步的DLL优化时钟定时

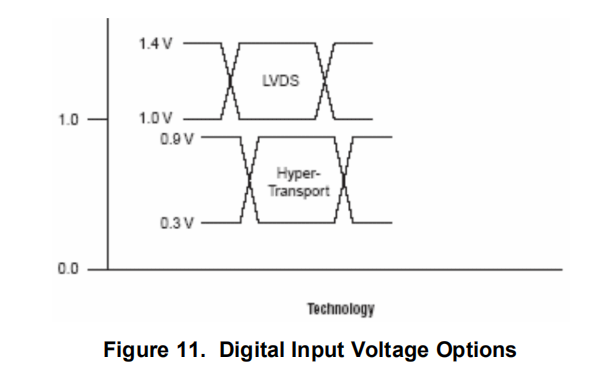

–LVDS和超级运输™ 电压电平兼容

–用于数据和参考位输入的内部100Ω终端

•可选择2次插值和Fs/2混合

•差分可缩放电流输出:5至30 mA

•片上1.2-V基准

•3.3-V模拟电源操作

•功耗:2 W•252 Ball GDJ封装

应用

•测试和测量:任意波形发生器

•通信

说明

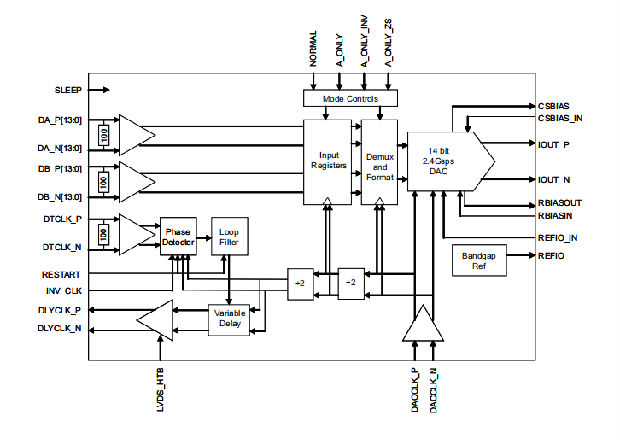

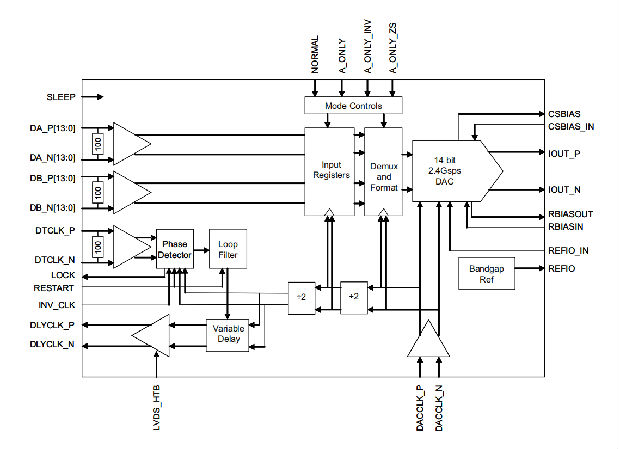

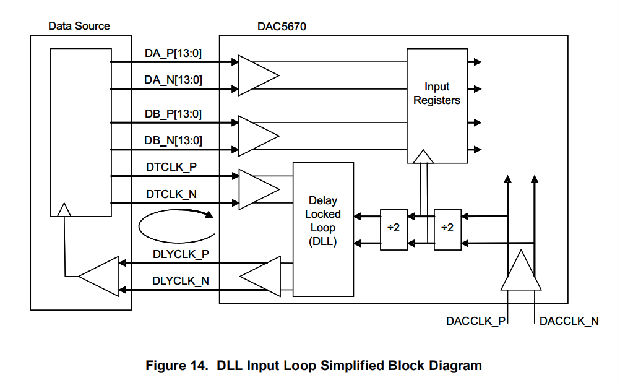

DAC5670是一个14位2.4-GSPS数模转换器(DAC),具有双解复用差分输入端口。DAC5670以DAC采样率计时,两个输入端口以最大1.2 GSPS的速度运行。一个附加的参考位输入序列被用来调整到数据源的输出时钟延迟,通过延迟锁定环(DLL)优化相对于该参考位的内部数据锁存时钟。或者,可以绕过DLL,并通过控制数据设置和保持DLYCLK的定时来管理定时接口。

DAC5670还可以在同一时钟配置的一个输入端口上接受高达1.2gsps的数据。在单端口模式下,通过重复输入采样(仅A U模式)、通过零填充进行2次插值(仅A_ZS模式)或通过重复和反转输入样本进行2次插值(A_ONLY_INV),可以将输入采样率提高一倍,达到2.4 GSPS。

DAC5670使用单个3-V至3.6-V电源电压工作。在最大工作条件下,功耗为2瓦。DAC5670提供20毫安的标称满标度差分电流输出,支持单端和差分应用。片上1.2V温度补偿带隙基准和控制放大器允许用户将满标度输出电流从标称20毫安调整到低至5毫安或高达30毫安。输出电流可以直接供给负载,不需要额外的外部输出缓冲器。该装置是专为差动变压器耦合输出和50Ω双端接负载而设计的。

DAC5670提供252球GDJ包。该装置的特点是可在-40°C至85°C的温度范围内工作。

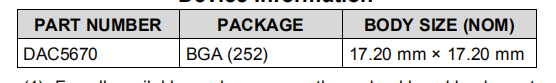

设备信息

(1)、有关所有可用的软件包,请参阅数据表末尾的订购附录。

简化示意图

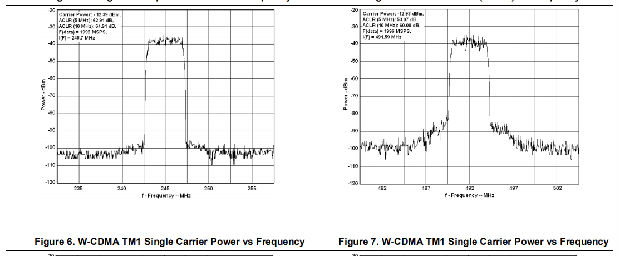

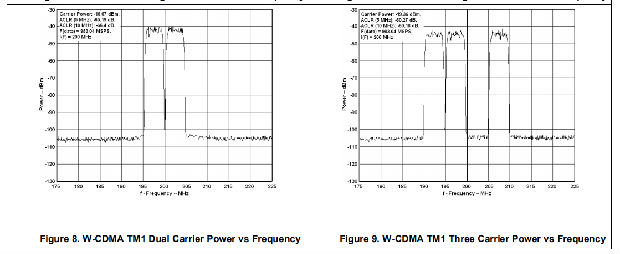

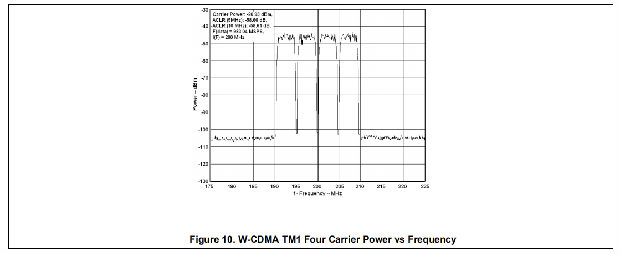

典型特征

详细说明

概述

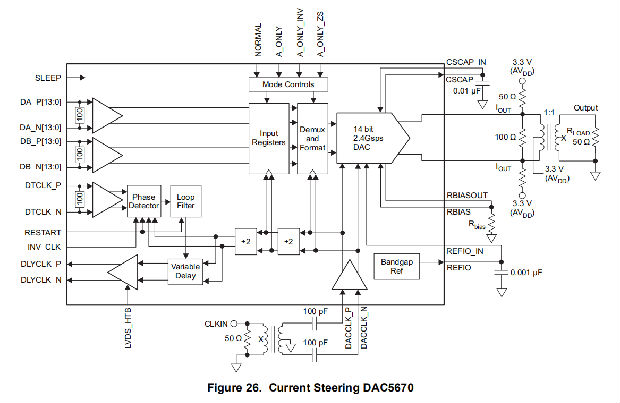

图26显示了当前转向DAC5670的简化框图。DAC5670由NPN晶体管电流汇分段阵列组成,能够提供高达30毫安的全刻度输出电流。差分电流开关将每个电流汇的电流引向互补输出节点IOUT_P或IOUT峎N之一。互补电流输出可实现差分操作,消除共模噪声源(数字馈通、片上和PCB噪声)、直流偏移和偶数阶失真分量,信号输出功率加倍。

满标度输出电流由一个外部电阻器(RBIAS)与片上带隙基准电压源(1.2V)和控制放大器相结合来设置。通过电阻RBIAS的电流(IBIAS)在内部镜像,以提供等于32×IBIAS的满标度输出电流。通过使用适当的偏置电阻值,满标度电流可在30至5 mA之间调节。

功能框图

特性描述

数字输入

DAC5670差分数字输入与LVDS和超级传输电压电平兼容。

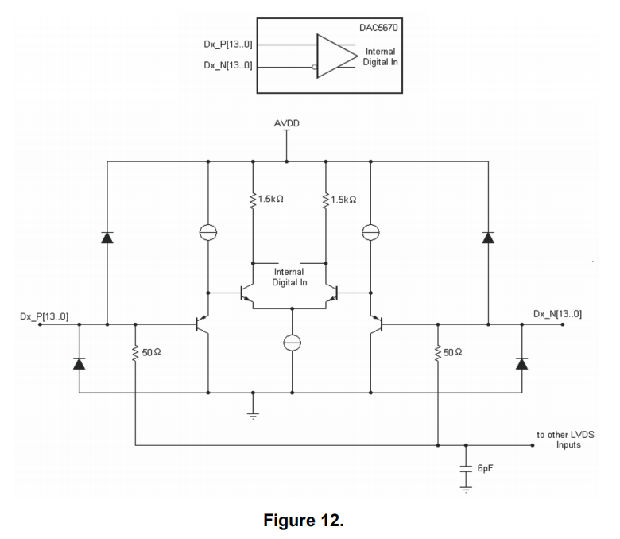

DAC5670使用低压差分信号(LVDS和超级传输)作为总线输入接口。LVDS和HyperTransport输入模式具有低差分电压摆幅的特点。LVDS和超级传输模式的差异特性允许在低电磁干扰(EMI)水平下进行高速数据传输。图12显示了DAC5670的等效互补数字输入接口,适用于引脚DA_P[13:0]、DA_N[13:0]、DB_P[13:0]和DB_N[13:0]。

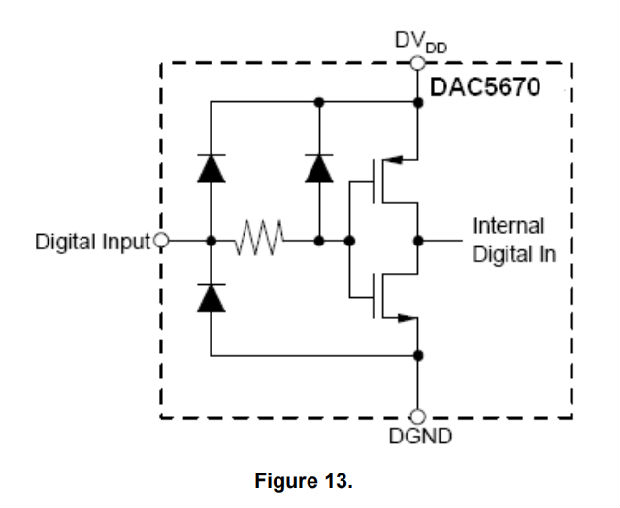

图13显示了DAC5670的等效CMOS/TTL兼容数字输入的示意图,适用于以下引脚:RESTART、LVDS_HTB、INV_CLK、SLEEP、NORMAL、a_ONLY、a_ONLY_INV和a_ONLY_ZS。

DLL使用

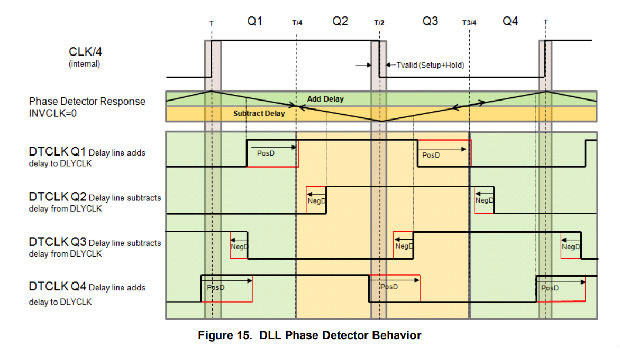

DAC5670以DAC采样率计时。每个输入端口的最大运行速度为1.2gsps。DAC5670以输入端口数据速率(DACCLK/4)的一半提供一个输出时钟(DLYLK),并监视一个附加的参考位(DTCLK)。DTCLK作为反馈时钟来调整接口时序。为了实现这一点,DAC5670实现了一个DLL来帮助管理来自外部数据源的定时接口。与所有DLL一样,DLL在延迟链长度、相位检测器的实现和控制回路的带宽方面的能力都有限制。DAC5670实现了基于正交的相位检测器。这种方案允许动态链接库在达到正交时提供最大的设置或保持延迟裕度。当内部CLK/4与DTCLK相位相差90°时,达到正交。此外,随着操作频率的降低,延迟线的固定长度限制了其改变延迟路径以达到正交的能力(见图15)。请注意,延迟线具有非对称属性。NegD范围小于PosD范围。从它的名义(重启)位置,它可以延迟比它能减去的更多。

图15显示了相位检测器和延迟线相对于DTCLK上升沿的初始位置的行为。有四个不同的象限来定义行为。每个象限表示DDR时钟速率(2.4-GSPS情况下为600 MHz)除以4的周期。理想位置在象限1中具有DTCLK(因此数据位)的初始延迟。动态链接库的稳定锁定点在T/4,介于Q1和Q2之间。如果DTCLK的初始延迟在象限3或4,则可以断言INV_ckpin以提高DLL获得正交的能力。这个断言将稳定的求积点移到3T/4vs T/4的中心,如图15所示。本质上,增加延迟的区域变成减去延迟的区域,反之亦然。CLK/4的时钟相位也会反转。

在不适合使用DLL来管理定时接口的情况下,当DLL保持在重新启动时,可以使用相对于生成的DLYCLK输出的DA和DB信号的固定设置和保持值。这是通过将RESTART断言为logic high,并在使用DLL时使用外部定时接口的定时输入条件来实现的。当使用外部设置和保持定时时,用户不需要提供DTCLK。在这种情况下,DTCLK应该偏向于有效的LVDS级别(参见图3)。

设置/保持值是非传统的,因为它们表示对生成时钟的输入的设置/保持(DLYCLK)。另外,设置/保持数字表示可能比DACCLK或DACCLK/2周期更长的延迟。要计算到最近相邻dlyck转换的设置/保持值,用户必须减去DACLCK/2周期的倍数,直到设置小于DACCLK/2周期。可以从保持时间中减去相同的量。这些新的设置/保持值将取决于频率。

时钟输入

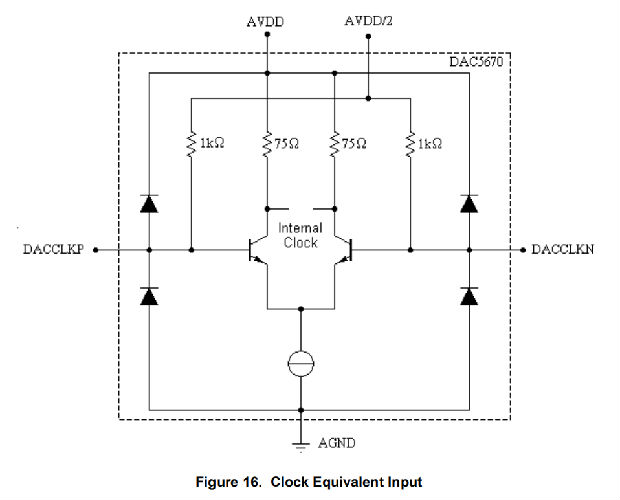

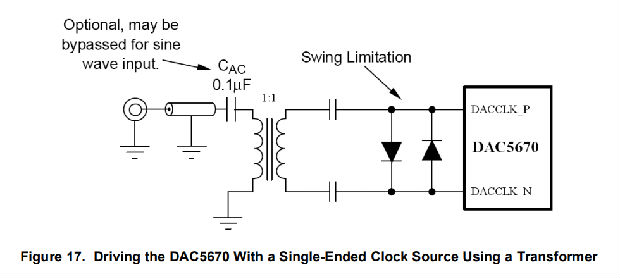

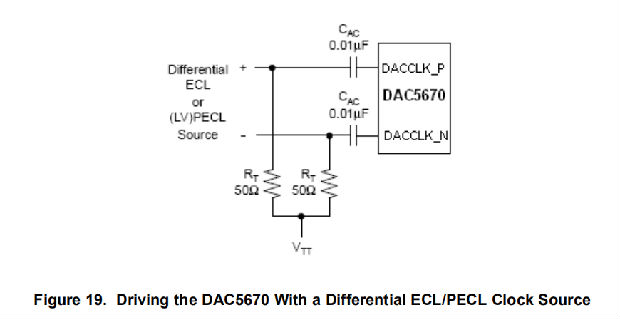

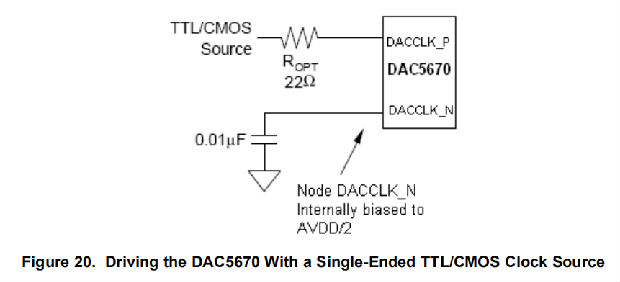

DAC5670具有与LVPECL兼容的差分时钟输入(DACCLKΜP、DACCLK_N)。图16显示了时钟输入缓冲器的等效示意图。内部偏置电阻将输入共模电压设置为AVDD/2,而输入电阻通常为1kΩ。各种时钟源可以与设备耦合,包括正弦波源(见图17)。

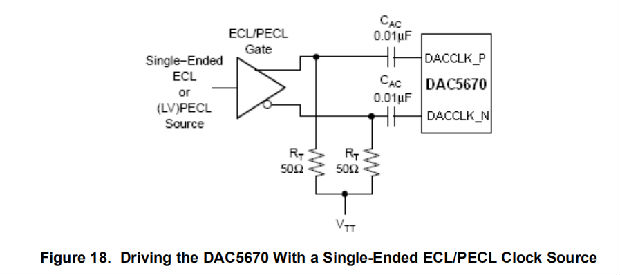

为了获得最佳的交流性能DAC5670,用差动LVPECL或正弦波源驱动时钟输入,如图18和图19所示。在这里,电压互感器的电位应设置为驱动器所需的端接电压以及适当的端接电阻(RT)。DAC5670时钟输入也可以使用TTL/CMOS电平进行单端驱动,以获得较低的时钟速率(参见图20)。

DAC传输功能

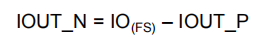

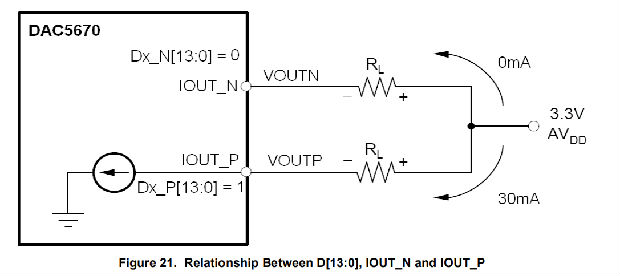

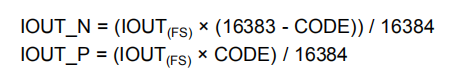

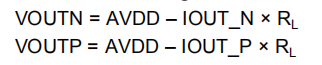

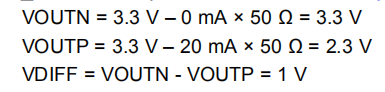

DAC5670具有电流汇输出。电流通过IOUT_P和IOUT_N由Dx_P[13:0]和Dx_N[13:0]控制。为了便于使用,D[13:0]表示为Dx_P[13:0]及其补码Dx_N[13:0]的逻辑位等价物。DAC5670支持直接二进制编码,D13作为MSB,D0作为LSB。当所有D[13:0]输入设为高时,满标度电流流过IOUTP;当所有D[13:0]输入设为低时,满标度电流流过IOUTN。IOUT_P和IOUT帴N之间的关系可表示为方程式1。

电流为全标度输出(5毫安)。因为输出级是一个电流汇,电流只能从AVDD通过负载电阻RL流入IOUT峎N和IOUT_P引脚。

驱动电阻负载的每个引脚中的输出电流可以表示为图21、方程式2和方程式3。

其中:

•CODE是DAC输入字的十进制表示

这转化为IOUT_N和IOUT_P处的单端电压,如方程式4和方程式5所示。

例如,假设D[13:0]=1且RL为50Ω,则引脚IOUT_N和IOUT_P之间的差分电压可以表示为等式6到方程8,其中IO(FS)=20 mA。

如果D[13:0]=0,则IOUT_P=0 mA,IOUT_N=20 mA,差分电压VDIFF=–1 V。

输出电流和输出电压是互补的。与单独测量每个输出相比,差分测量的电压将增加一倍。小心不要超过IOUT峈N和IOUT峎P引脚的合规电压,以保持低信号失真。

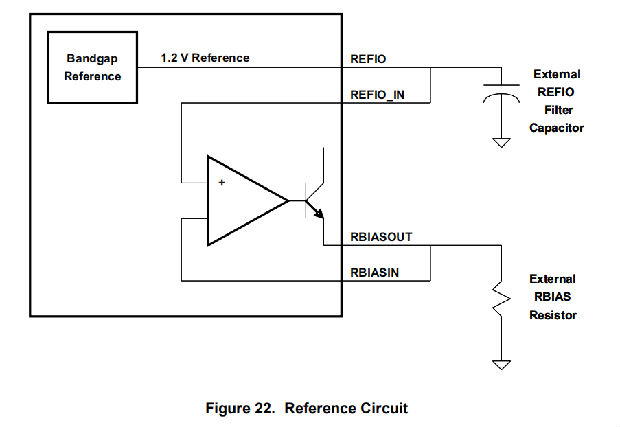

参考操作

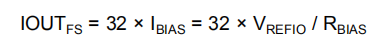

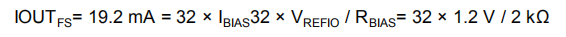

DAC5670包括用于偏置满标度输出电流的带隙基准和控制放大器。满标度输出电流通过在引脚RBIASOUT和RBIASIN上施加一个外部电阻器RBIAS来设置。偏置电流IBIAS,通过电阻RBIAS,由片上带隙基准电压和控制放大器定义。满标度输出电流等于该偏置电流的32倍。因此,满标度输出电流IOUTF可表示为:

其中:

•引脚REFIO和REFIO_IN处的VREFIO电压

带隙参考电压提供1.2V的精确电压。设计者应将0.1μF的外部REFIO滤波器电容器连接到REFIO和REFIO_-IN引脚上进行补偿。

通过改变外部电阻RBIAS,满标度输出电流可以从30毫安调整到5毫安。

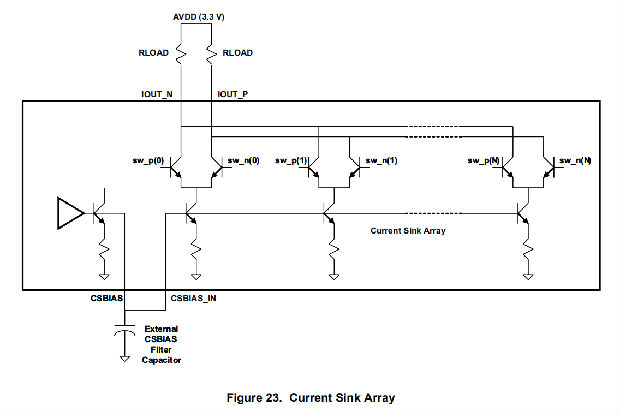

模拟电流输出

图23是带有相应开关的电流汇阵列输出的简化示意图。差分NPN开关将每个单独NPN电流汇的电流引导至正输出节点IOUT_P或其互补的负输出节点IOUT_N。在DA_P[13:0]、DA_N[13:0]、DB_P[13:0]和DB_N[13:0]处显示的输入数据被解码以控制sw_P(N)和sw_N(N)电流开关。

外部输出电阻RLOAD连接到正极电源AVDD。

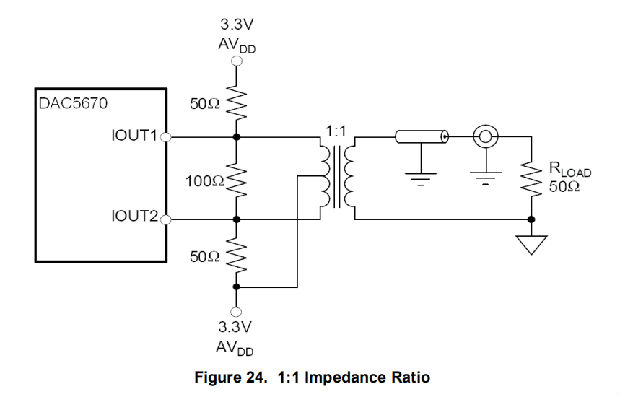

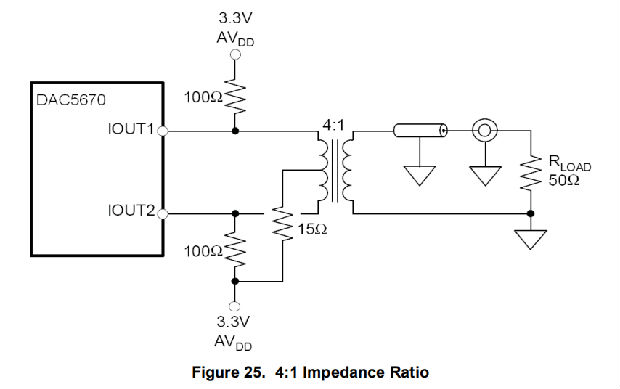

DAC5670可以很容易地配置为使用正确选择的变压器驱动双端接50Ω电缆。图24和图25分别显示了1:1和4:1阻抗比配置。这些配置提供对共模噪声源和偶数阶失真分量的最大抑制,从而使DAC的输出功率加倍。变压器一次侧的中心抽头端接至AVDD,使IOUT帴N和IOUT帴P都能获得直流电流。

睡眠模式

当休眠引脚被断言(高)时,DAC5670进入低功耗模式。

设备功能模式

输入格式

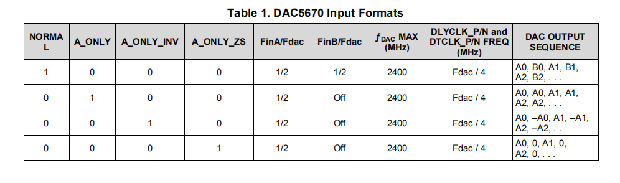

DAC5670有四种由四个互斥配置引脚选择的输入模式:正常、仅A U、A U ONLY U INV和A U ONLY U ZS。表1列出了每个配置的输入模式、输入采样率、最大DAC采样率(CLK输入)和产生的DAC输出序列。对于所有配置,DLYCLK_P/N输出和DTCLK_P/N输入都是dacclu P/N频率除以4。

应用与实施

注意

以下应用章节中的信息不是TI组件规范的一部分,TI不保证其准确性或完整性。TI的客户负责确定组件的适用性。客户应验证和测试其设计实现,以确认系统功能。

申请信息

DAC5670是一个14位的DAC,最大输入速率为2.4 GSPS。DAC5670也适合在较低的采样率下工作,而无需使用DLL进行输入接口计时。

典型应用

设计要求

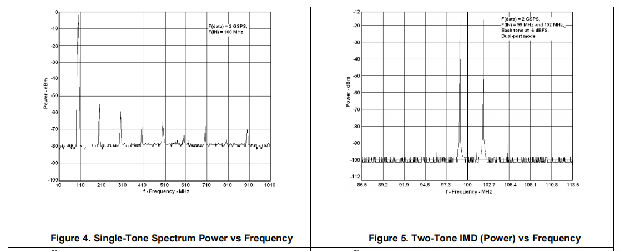

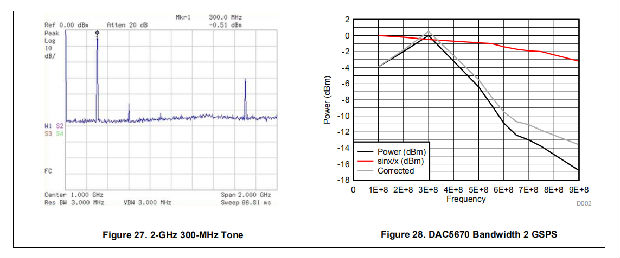

此示例使用2 GHz的DACCLK速率,信号输出为300 MHz。

详细设计程序

这个例子是以2-GHz的采样率输出300兆赫的音调。数据以1GHz双数据速率应用于A和B端口。满标度输出电流设置为19.2 mA。

设备设置:

•低重启

•LVDS U HTB(模式发生器源相关)

•DLL锁定所需的INV_CLK

•低睡

•正常高

•仅A_低

•仅A_INV低

•仅限于低

•dau P[0:13]、DA_N[0:13]、DB_P[0:13]、DB_N[0:13],源于模式发生器,产生300 MHz音调,采样深度65536

•RBIAS 2 kΩ接地

应用曲线

电源建议

DAC5670使用单一的3.3V电源简化了设计要求。电源应过滤掉可能存在的任何其他系统噪音。滤波应特别注意输出的相关频率。

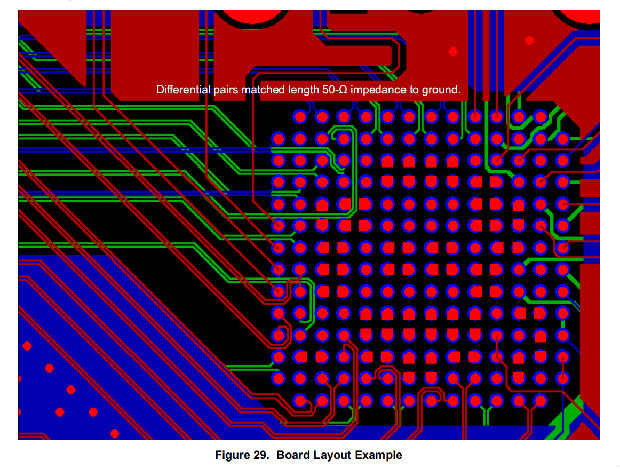

布局

布局指南

•DAC输出端应尽可能靠近输出端。

•保持RBIA的路由短。

•去耦电容器应尽可能靠近电源引脚。

•数字差分输入必须为50Ω对地松散耦合,或100Ω差分紧密耦合。

•数字差分输入必须长度匹配。

布局示例