特征

•直接测量64的单片机解决方案低电平电流

•经验证的高精度,真正的集成100%收费架构

•为现有DDC系列轻松升级应用

•极低功率:3mW/通道

•极线性:进口=读数的±0.025%±1.0ppm FSR

•低噪音:FSR 6.3ppm

•可调满标度范围

•可调速度

–数据速率高达6kSPS,20位性能

–微秒集成时间低至160

•菊花链串行接口

•封装内旁路电容器简化了PCB设计

应用

•CT扫描仪

•光电二极管传感器

•X射线探测系统

说明

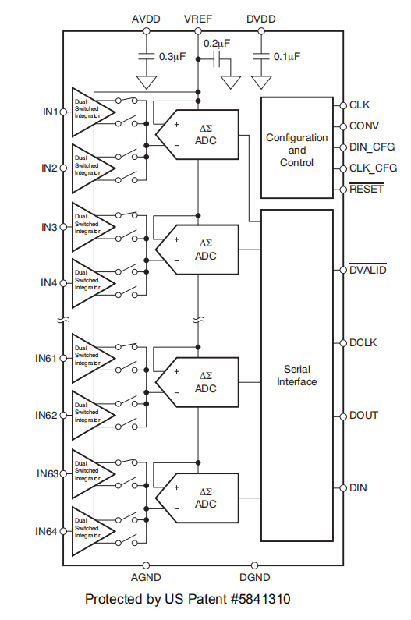

DDC264是一个20位,64通道,电流输入模数转换器。它结合了电流电压转换和A/D转换,使得64个独立的低电平电流输出设备,如光电二极管,可以直接连接到它的输入端并数字化。

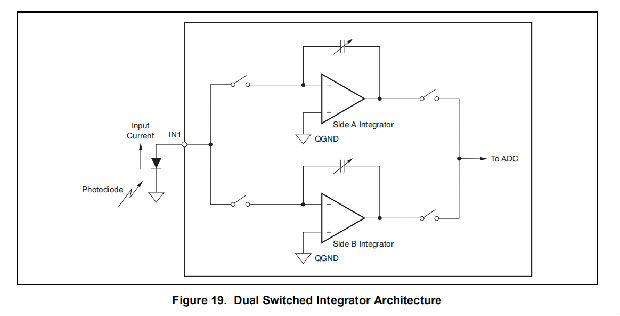

对于64个输入端中的每一个,DDC264都使用经过验证的双开关积分器前端。这种配置允许连续电流积分:当一个积分器被板载A/D转换器数字化时,另一个积分器对输入电流进行积分。这种结构提供了一个非常稳定的偏移和无损耗的输入电流收集。积分时间可调范围从160μs到1s,允许以优异的精度连续测量从fAs到μAs的电流。

DDC264有一个串行接口,设计用于多设备系统中的菊花链。只需将一个设备的输出连接到下一个设备的输入即可创建链。普通时钟为链中的所有设备供电,因此多DDC264系统中的数字开销最小。

DDC264使用+5V模拟电源和+2.7V至+3.6V数字电源。DDC264封装中的旁路电容器有助于最大限度地降低外部元件的要求。DDC264 BGA-100封装在0°C到+70°C的温度范围内工作,有两种版本:DDC264C用于低功耗应用,DDC264CK用于需要更高速度时。

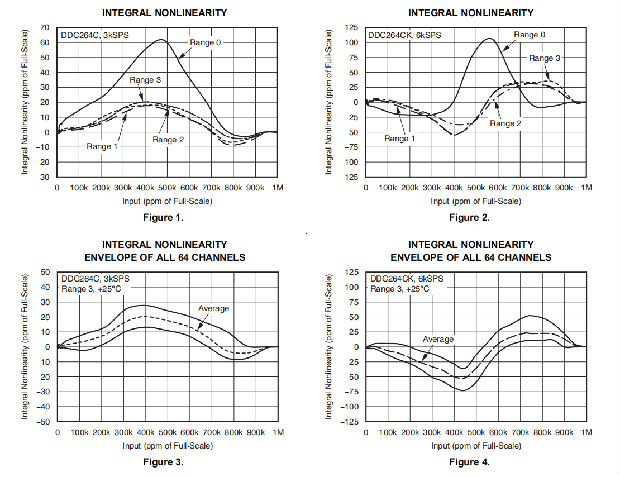

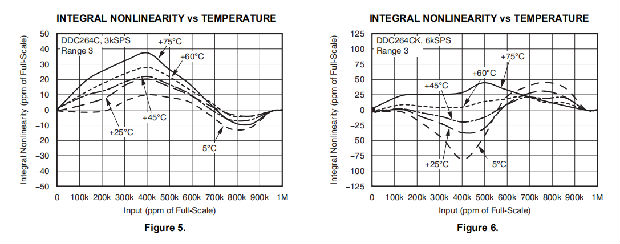

典型特征

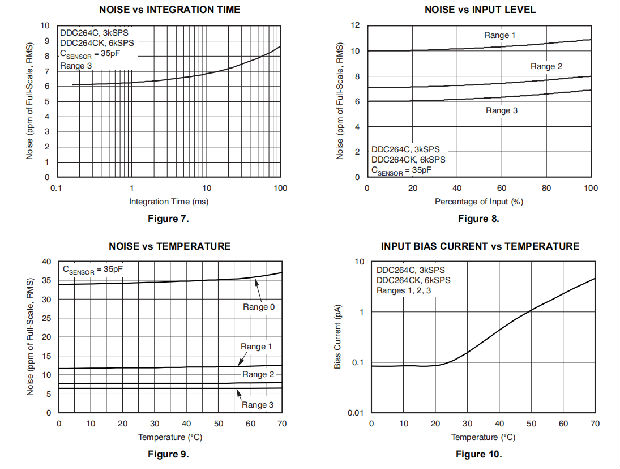

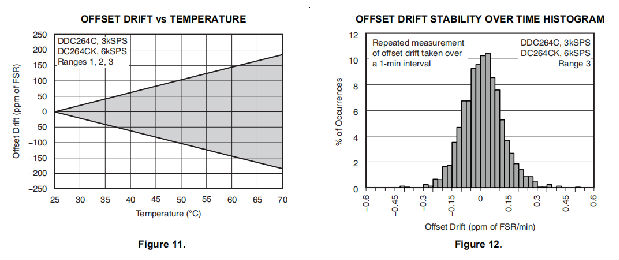

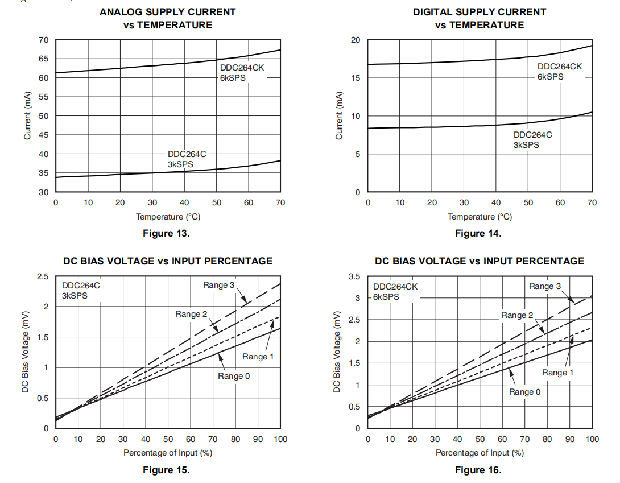

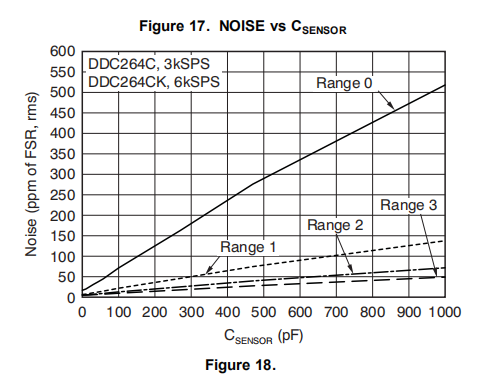

TA=+25°C时,除非另有说明。

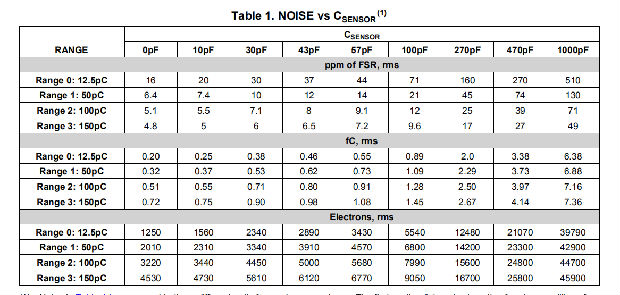

(1)、为了方便读者阅读,表1中的噪声用三种不同的单位表示。第一部分以满标度范围的百万分之一为单位列出噪声;第二部分将噪声表示为等效输入电荷(单位:fC);第三部分将噪声转换为电子。

一般说明

DDC264的双开关积分器输入通道如图19所示。DDC264包含64个相同的输入通道,这些通道执行电流到电压积分以及多路a/D转换的功能。每个输入端都有两个积分器,这样电流电压积分就可以在时间上连续进行。DDC264通过在A侧和B侧之间切换积分来连续集成输入信号。

例如,当A侧集成输入信号时,B侧输出由车载数字化ADC。这个积分和A/D转换过程由转换引脚CONV控制。每个信号输入的A侧和B侧的结果存储在串行输出移位寄存器中。当移位寄存器数据准备好检索时,DVALID输出变低。

基本积分周期

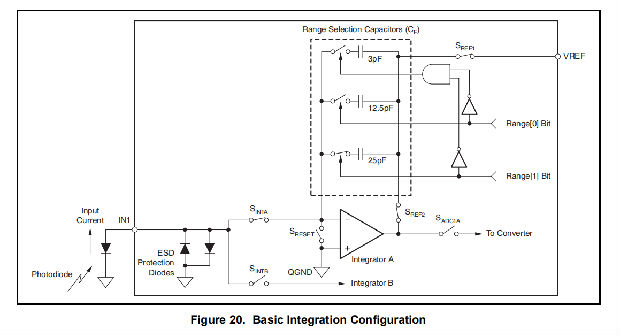

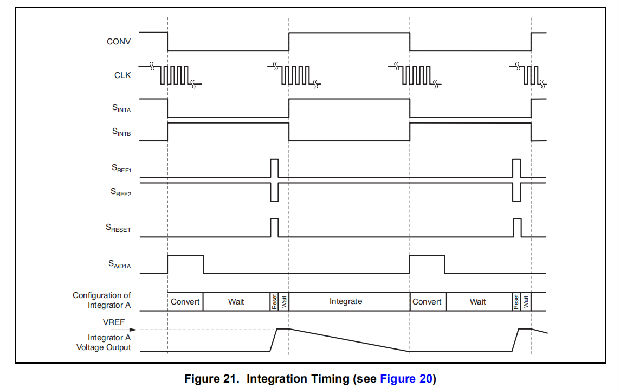

DDC264前端的拓扑结构是一个模拟积分器,如图20所示。在这个图中,只显示IN1输入。输入级由一个运算放大器、一个可选择的反馈电容网络(CF)和几个实现积分循环的开关组成。图20所示的所有开关的时序关系如图21所示。图21对DDC264的积分器输入级的操作进行了概念化,不应将其用作设计的精确计时工具。

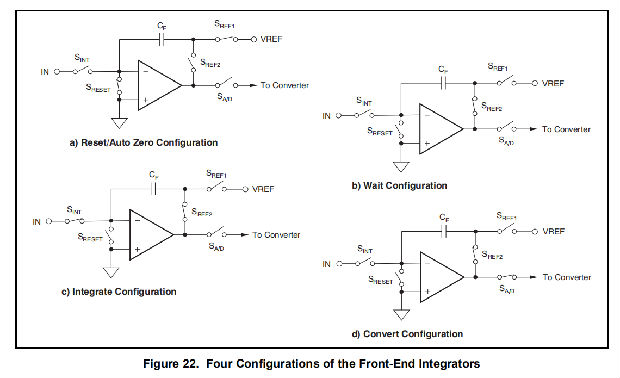

DDC264积分器部分的复位、积分、等待和转换状态的方框图见图22。这种内部交换网络由转换管脚(CONV)和系统时钟(CLK)进行外部控制。为了获得最佳的噪声性能,CONV必须与CLK的下降沿同步。建议在CLK下降沿的±10ns范围内进行CONV切换。

积分器的非转换输入连接到QGND引脚。因此,DDC264模拟接地QGND应尽可能干净。在图20中,反馈电容器(CF)显示在运算放大器的反向输入和输出之间并联。在转换开始时,设置开关SA/D、SINTA、SINTB、SREF1、SREF2和SRESET(见图21)。

在A/D转换完成时,电荷积分电容器(CF)用SREF1和SRESET复位(见图21和图22a)。此过程在重置期间完成。以这种方式,所选电容器被充电到参考电压VREF。一旦集成电容器充电,SREF和SRESET被切换,以便VREF在等待开始积分时不再连接到放大器电路(见图22b)。随着CONV的上升,SINTA关闭,开始对A侧进行集成。这一过程将积分器阶段置于其集成模式(参见图22c)。

来自输入信号的电荷被收集到集成电容器上,导致放大器的电压输出降低。CONV的下降沿通过将输入信号从A侧切换到B侧(SINTA和SINTB),停止积分。在CONV下降沿之前,B侧的信号被A/D转换器转换,并在A侧积分期间复位。随着变频器下降沿,B侧开始对输入信号进行积分。此时,A侧运算放大器的输出电压被提供给A/D转换器的输入端(见图22d)。

特殊的静电放电(ESD)结构保护输入,但不会增加输入引脚上的电流泄漏。

集成电容器

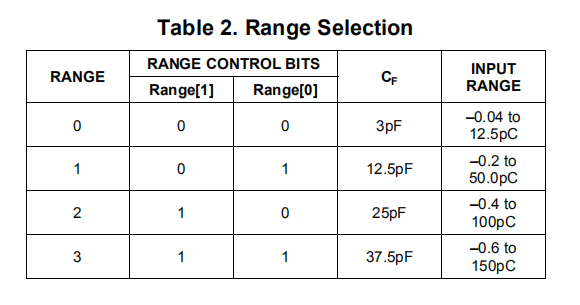

在DDC264中,每个通道的两侧都有四种不同的电容器配置。这些内部电容器在生产中进行了微调,以达到DDC264的量程误差规定性能。量程控制位(量程[1:0])设置所有电容器的值积分器。因此,所有输入和每个输入的两侧始终具有相同的满标度范围。表2显示了为每个量程选择选择的电容值。

电压基准

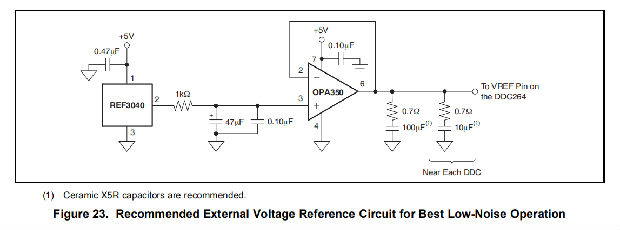

外部参考电压用于在积分循环开始之前重置积分电容器。当A/D转换器测量积分周期结束后积分器上存储的电压时,它也被A/D转换器使用。在这个采样过程中,外部基准必须提供A/D转换器所需的电荷。对于333μs的积分时间,该电荷转化为约825μA的平均VREF电流。A/D转换器所需的电荷量与积分时间无关;因此,增加积分时间会降低平均电流。例如,800μs的积分时间将平均VREF电流降低到340μA。

在不同的操作模式下,VREF必须稳定(见图22)。A/D转换器测量积分器上相对于VREF的电压。因为积分器电容器最初被重置为VREF,从电容器复位到转换器测量积分器输出时,VREF的任何下降都会引入偏移。同样重要的是,VREF在较长时间内保持稳定,因为VREF的变化直接对应于满标度范围的变化。最后,VREF应该引入尽可能少的附加噪声。

出于这些原因,强烈建议使用运算放大器缓冲外部参考源,如图23所示。在该电路中,参考电压由+4.096V参考电压产生。低通滤波器用于降低噪声,将基准连接到配置为缓冲器的运算放大器。该放大器应具有低噪声和支持VREF的输入/输出共模范围。尽管图23中的电路可能因为输出电容量大而显得不稳定,但它对于OPA350来说工作得很好。不建议在输出引线中放置串联电阻以提高稳定性,因为这会导致VREF下降,从而产生较大的偏移。

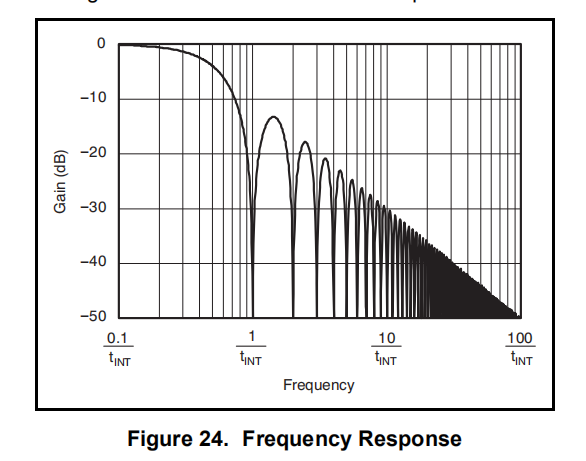

频率响应

DDC264的频率响应由前端积分器设置,是传统的连续时间积分器的频率响应,如图24所示。通过调整积分时间t INT,用户可以改变3dB带宽和响应中缺口的位置。跟随前端积分器的A/D转换器的频率响应不重要,因为转换器从积分器中采集保持信号。也就是说,A/D转换器的输入总是直流信号。对前端积分器的输出进行采样;因此,可能会出现混叠。每当输入信号的频率超过采样率的一半时,信号就会折回到较低的频率。

数字接口

DDC264的数字接口通过由数据时钟(DCLK)、有效数据引脚(DVALID)、串行数据输出引脚(DOUT)和串行数据输入引脚(DIN)组成的同步串行接口发送数字结果。集成和转换过程基本上独立于数据检索过程。因此,CLK和DCLK频率不必相同,尽管为了获得最佳性能,强烈建议它们来自相同的时钟源以保持相位关系恒定。DIN仅在多个转换器级联时使用,否则应与DGND连接。根据tINT、CLK和DCLK,可以菊花链多个转换器。此选项大大简化了中数字输出的互连和路由需要大量转换器的应用。DDC264的配置由一个专用寄存器设置,该寄存器使用DIN U CFG和CLK U CFG引脚寻址。

系统和数据时钟(CLK和DCLK)

系统时钟提供给CLK,数据时钟提供给DCLK。建议CLK引脚由自由运行的时钟源驱动(即,在转换之间不要启动和停止CLK)。确保时钟信号干净,避免过冲或响铃。为了获得最佳性能,请从同一个时钟源生成两个时钟。在数据移出后,在CONV转换时,通过将其调低来禁用DCLK。

当使用多个DDC264时,请密切注意印刷电路板(PCB)上的DCLK分布。特别是,确保尽量减少DCLK信号中的偏差,因为这可能导致串行接口规范中的时序冲突。有关详细信息,请参阅级联多个转换器部分。

数据有效(DVALID)

数据有效信号表明数据准备好了。数据检索可能在DVALID变低后开始。该信号是使用从系统时钟CLK中分离出来的内部时钟产生的。内部时钟和时钟周期之间的相位关系是在首次通电时设置的,并且是随机的。由于用户必须使CONV与CLK同步,DVALID信号与CONV具有随机相位关系,不确定度为±1/fCLK。投票DVALID消除了对这种关系的任何顾虑。如果数据回读是从CONV定时的,请确保等待所需的时间。

复位(Reset)

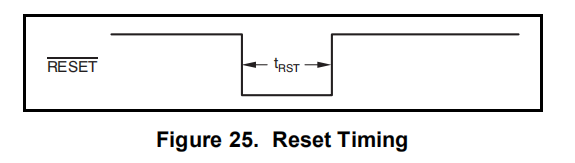

DDC264通过将重置输入设为低值异步重置,如图25所示。确保释放脉冲至少为tRST宽度。这是非常重要的,复位是无故障的,以避免无意的复位。之后必须立即对配置寄存器进行编程。对DDC264编程后,在使用数据之前,至少等待四次转换。

计时示例

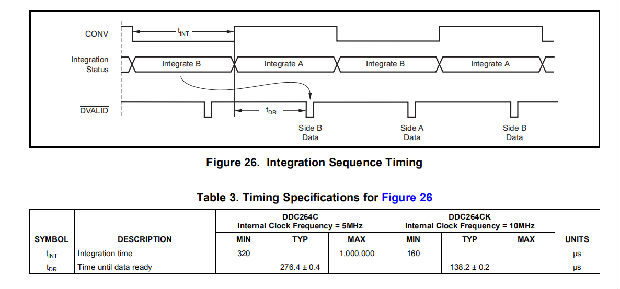

图26显示了在设备通电、复位和配置寄存器编程之后开始的几个集成周期。顶部信号为CONV,由用户提供。集成状态跟踪指示哪一方正在集成。如数据表所述,当数据准备好从DDC264检索时,DVALID变为低电平。它会一直保持在低水平,直到用户将DCLK设为高位,然后又回到低位。DVALID脉冲下方的文本表示可供读取的数据侧。箭头用于将数据与相应的集成相匹配。表3显示了图26的定时规范。

积分时间

最小色调取决于所使用的设备。最小时间直接与内部时钟频率成比例。对于内部时钟频率为5MHz的DDC264C,最小时间为320μs;对于内部时钟频率为10MHz的DDC264C,最小时间为166μs。如果违反最小积分时间,DDC264将停止对输入信号的连续积分。要在违反最小色调规范后恢复正常操作(即连续积分),请执行三次积分,每次至少持续5000个内部时钟周期。换言之,当使用5MHz的内部时钟频率时,每次积分至少持续1ms,进行三次积分。在此期间,忽略DVALID pin。三次集成完成后,恢复正常的连续操作,并可检索数据。

数据格式

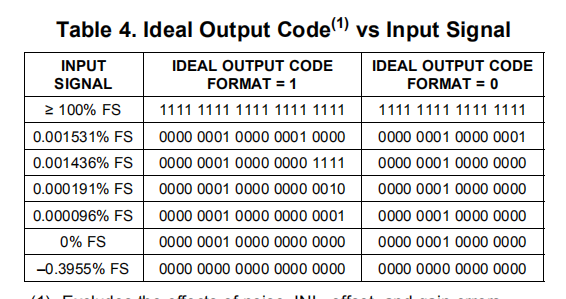

串行输出数据以偏移二进制代码的形式提供,如表4所示。配置寄存器中的格式位选择输出字中使用的位数。当Format=1时,使用20位。当Format=0时,低位四位被截断,因此只使用16位。注意,当Format=0时,LSB的大小是原来的16倍。输出中包含一个偏移量,以允许从限幅读数中输入稍负的输入(例如,来自板泄漏的输入)。此偏移约为正满标度的0.4%。

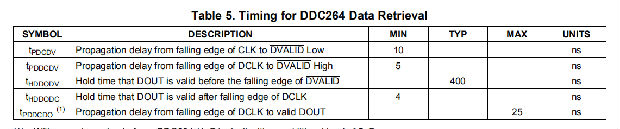

数据检索

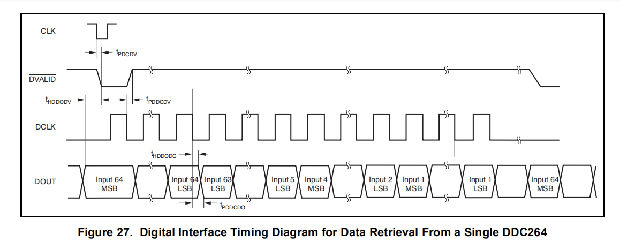

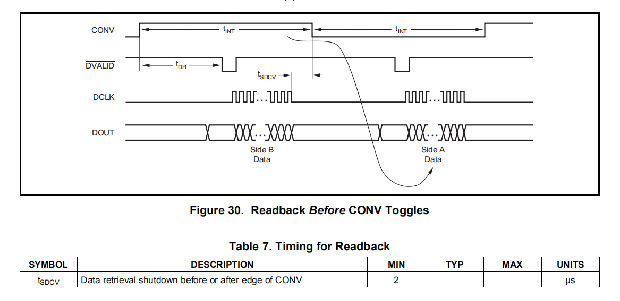

最后一次转换的数据可在DVALID的下降沿检索(见图27和表5)。数据在数据时钟DCLK的下降沿向外移动。

确保不要在CONV中检索有关更改的数据,因为此更改可能会引入噪音。停下在CONV转变之前或之后,DCLK的活性至少为2μs。

设置格式bit=0(16位输出字)可将检索数据所需的时间减少20%,因为要移出的位更少。这种技术可用于只需要16位分辨率的多通道系统。

(1)、最大负载为一个DDC264(典型4pF),附加负载为5pF。

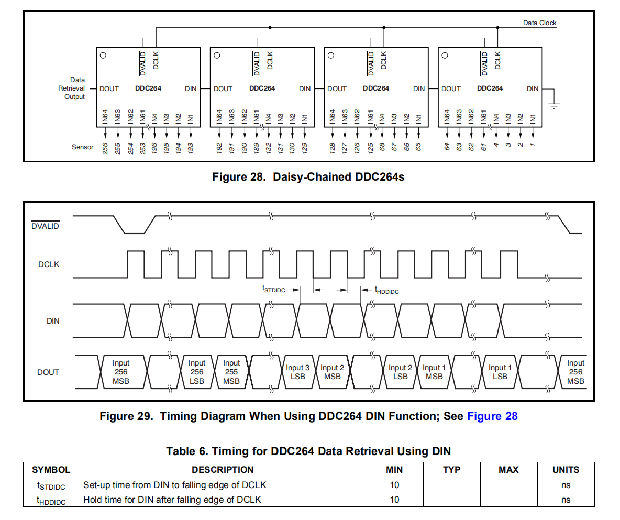

级联多个转换器

在串行配置中可以连接多个DDC264设备;请参见图28。

DOUT可与DIN一起使用,以菊花链多个DDC264设备在一起,以减少布线。在这种操作模式下,串行数据输出通过多个DDC264进行移位;见图28。

图29显示了当DIN输入被用于菊花链几个设备时的时序图。表6给出了使用DIN进行数据检索的时序规范。

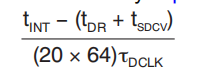

转换前检索

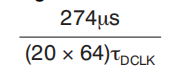

数据检索应该在CONV切换之前进行。数据检索在DVALID变低后很快开始,在CONV切换之前结束,如图30所示。为了获得最佳性能,数据检索必须在CONV切换之前停止tSDCV。这种方法最适合于较长的积分时间。可用于回读的最长时间为(tINT–tCMDR–tSDCV)。可以菊花链连接在一起的DDC264的最大数量(格式=1)为由式1计算:

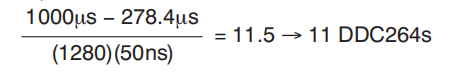

注:(16×64)τDCLK用于格式=0,其中τDCLK是数据时钟的周期。例如,如果tINT=1000μs且DCLK=20MHz,则格式为1的DDC264的最大数量如所示公式2:

(或14 DDC264s格式=0)

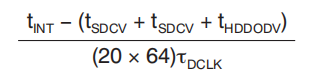

转换开关后检索

对于较短的集成时间,如果数据检索在CONV切换之后开始,而在新数据准备好之前结束,则可以获得更多的时间。数据检索必须在CONV切换后等待tSDCV才能开始。关于这个计时的例子,请参见图31顺序。那个可用于检索的最长时间为tDR–(tSDCV+tHDDODV),与色调无关。可以菊花链连接在一起的DDC264的最大数量(格式=1)由公式3计算:

注:(16×64)τDCLK表示格式=0。

对于DCLK=20MHz,DDC264的最大数量为4(对于格式=0,则为5)。

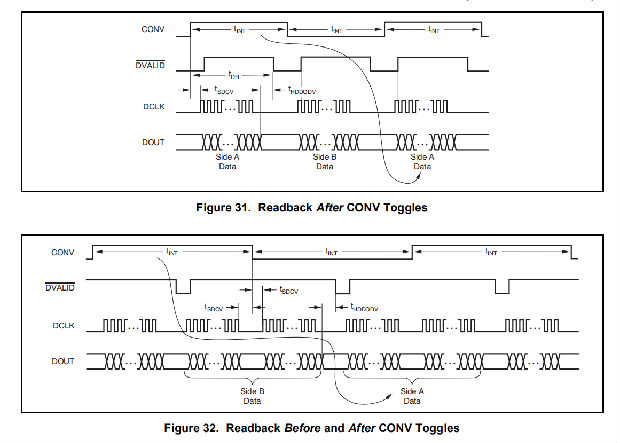

转换前后检索切换

对于数据检索的绝对最大时间,可以在CONV之前和之后检索数据切换。差不多了所有色调可用于数据检索。图32说明了如何通过结合前两种方法来完成此过程。如前所述,在转换切换期间暂停检索以防止数字噪声,并在下一个数据准备就绪之前完成。可以菊花链连接在一起的DDC264的最大数量为:

注:(16×64)τDCLK用于格式=0。

对于tINT=400μs和DCLK=20MHz,DDC264s的最大数量为6(对于Format=0,则为7)。

配置寄存器

读写操作

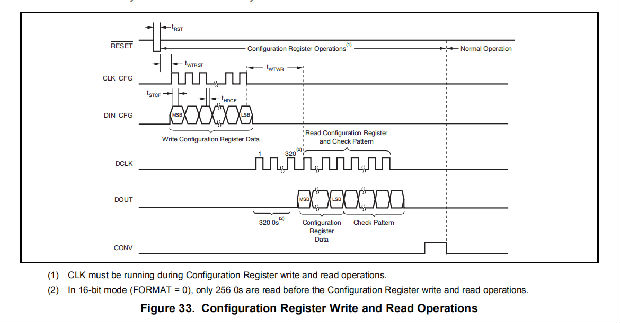

配置寄存器必须在通电或设备复位后进行编程。DIN_CFG、CLK_CFG和RESET引脚用于写入该寄存器。当开始写入操作时,保持CONV low和选通复位;参见图33。然后开始转移DIN上的配置数据_配置数据先写入配置寄存器的最高有效位。数据被内部锁存在CLK_CFG的下降沿。不允许对配置寄存器进行部分写入。请确保在更新寄存器时发送所有16位。

配置寄存器的可选读回在写入后立即可用顺序。期间回读,320'0's,然后16位配置数据后跟4位修订ID和检查模式在DCLK上升边缘的DOUT引脚上向外移动。检查模式可用于检查或验证DOUT功能。

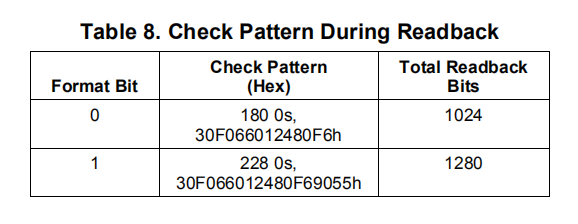

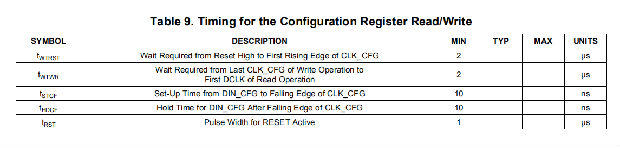

注:Format=1时,校验模式为300位,只有最后72位非零。对于每个DDC264,此输出序列重复两次,配置回读支持菊花链。表8显示了读回期间的检查模式配置。表9显示了配置寄存器读写操作的计时。选通变压器开始正常运行。

布局

电源和接地

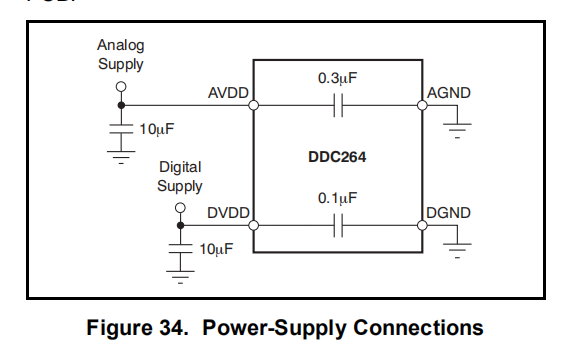

AVDD和DVD都应尽可能安静。消除与DDC264操作不同步的AVDD噪声尤为重要。图34说明了如何为DDC264供电。每个DDC264在AVDD和DVD上都有内部旁路电容器;因此,通常需要的唯一外部旁路电容器是10μF陶瓷电容器,每个PCB一个。建议将模拟和数字接地(AGND和DGND)连接到PCB上的单个接地平面。

屏蔽模拟信号通路

与任何精密电路一样,精心的PCB布局确保了最佳性能。必须进行短距离直接互连,避免杂散布线电容,尤其是在模拟输入引脚和QGND处。模拟输入管脚具有高阻抗,对外界噪声极为敏感。QGND引脚应被视为敏感的模拟信号,并通过适当的屏蔽直接连接到电源接地。如果不进行屏蔽,PCB线路之间的泄漏电流可能超过DDC264的输入偏置电流。数字信号应尽可能远离PCB上的模拟输入信号。

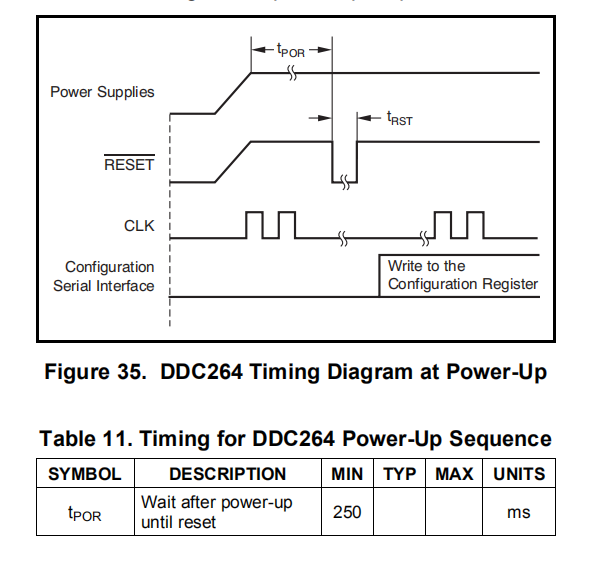

通电顺序

在设备通电之前,所有的数字和模拟输入必须是低的。在通电时,所有这些信号都应该保持在较低的水平,直到电源稳定下来,如图35所示。模拟电源必须在数字电源之前或同时启动。此时,开始向CLK引脚提供主时钟信号。等待时间t或,然后给出复位脉冲。释放复位后,必须写入配置寄存器。表11显示了通电顺序的计时。