BUF602点击型号即可查看芯片规格书

特征

•宽带:1000MHz

•高转换率:8000V/μs

•灵活的供应范围:

±1.4V至±6.3V双电源

+2.8V至+12.6V单电源

•输出电流:60mA(连续)

•峰值输出电流:350mA

•低静态电流:5.8mA

•低静态电流:5.8mA

•可选中间电源参考缓冲器

应用

•低阻抗参考缓冲器

•时钟分配电路

•视频/广播设备

•通信设备

•高速数据采集

•测试设备和仪器

说明

BUF602是一种闭环缓冲器,建议广泛应用。它的宽带宽(1000MHz)和高转换率(8000V/μs)使其成为缓冲非常高频信号的理想选择。对于交流耦合应用,提供了可选的中点参考(VREF),减少了所需的外部组件数量和提供该参考所需的必要电源电流。

BUF602有标准的SO-8表面贴装封装和SOT23-5,后者需要更小的占地面积。

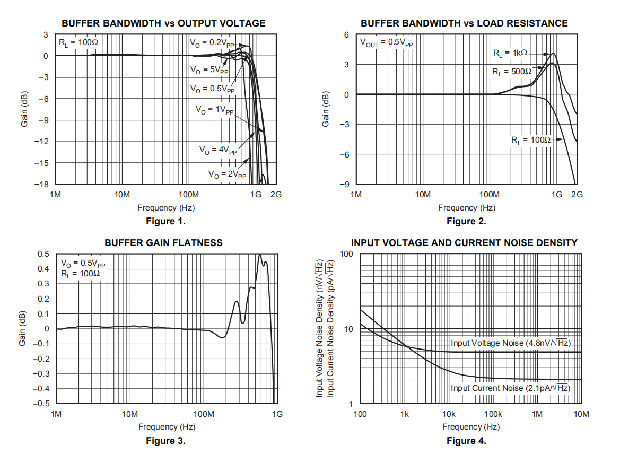

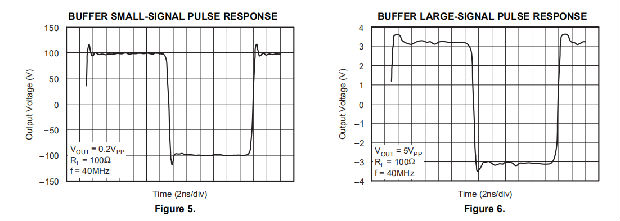

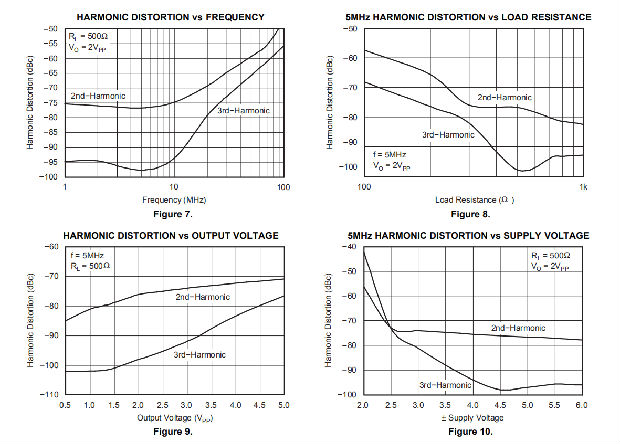

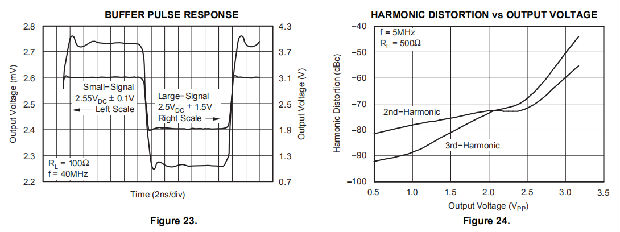

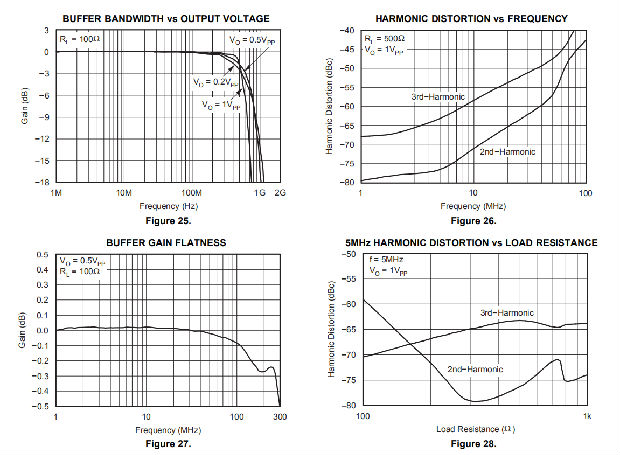

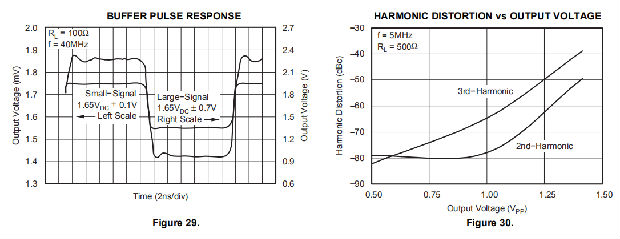

典型特性:VS=±5V

TA=+25°C和RL=100Ω时,除非另有说明。

申请信息

宽带缓冲操作

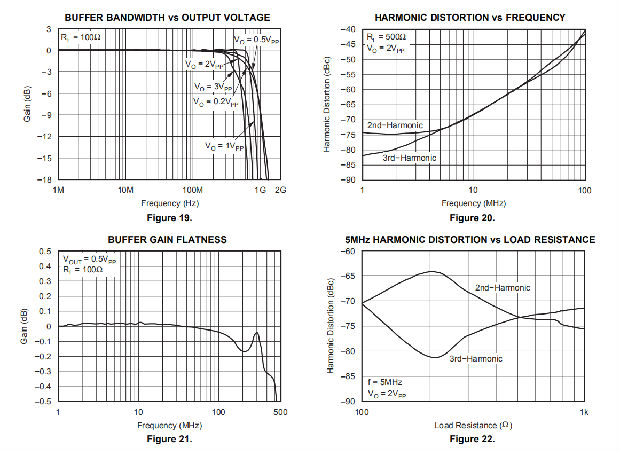

BUF602提供了宽带缓冲器的卓越交流性能。只需要5.8mA的静态电流,BUF602将摆动至任一供电轨的1V范围内,并在室温下提供超过60mA的电流。这种低输出净空要求,加上独立于电源电压的偏压,提供了显著的单(+5V)电源操作。BUF602将提供大于500MHz的带宽,在单个+5V电源上驱动2VPP输出到100Ω。

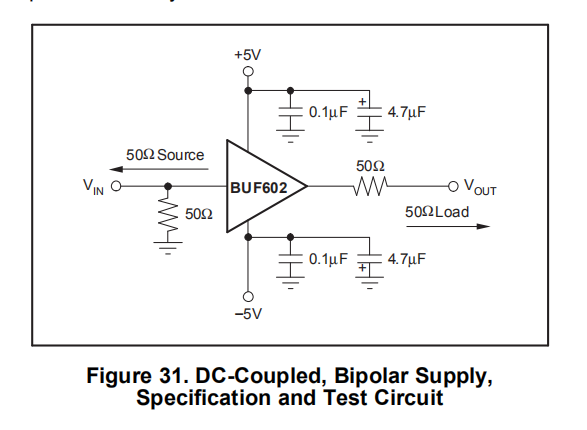

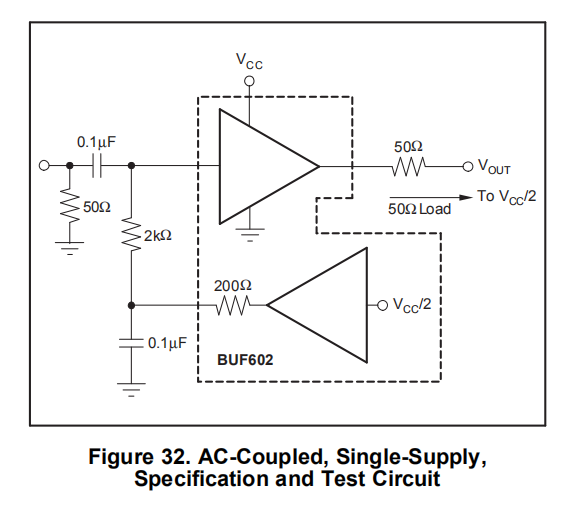

图31显示了作为±5V电气特性和典型特性基础的直流耦合双电源电路配置。出于测试目的,使用接地电阻将输入阻抗设置为50Ω,使用串联输出电阻将输出阻抗设置为50Ω。规范中报告的电压波动直接在输入和输出引脚处获得,而负载功率(dBm)则在匹配的50Ω负载下定义。除了通常的对地电源去耦电容器外,两个电源引脚之间还可以包括一个0.01μF电容器。这种可选的附加电容器通常会提高3dB到6dB的二次谐波失真性能。

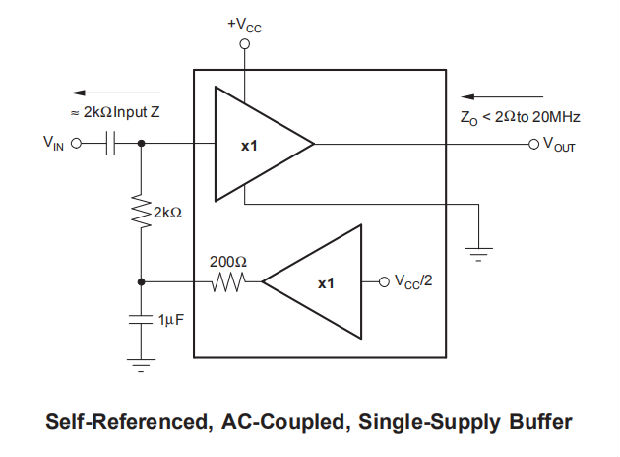

图32显示了作为+5V电气和典型特性基础的交流耦合单电源电路配置。尽管不是一个铁路到铁路的设计,BUF602需要最小的输入和输出电压净空比其他非常宽频带缓冲器。它将在单个+5V电源上提供3VPP输出摆幅,带宽大于400MHz。BUF602宽带单电源运行的关键要求是保持输出信号在可用电压范围内摆动。图32的电路使用内部中点基准建立输入中点偏置。然后输入信号被交流耦合到这个中点电压偏置中。同样,在单个+5V电源上,输出电压可以在任何一个电源引脚的1V范围内摆动,同时提供超过60mA的输出电流。在这个特性化电路中使用了一个要求100Ω的负载到一个中点偏置。

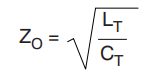

低阻抗传输线

最重要的方程和传输线的技术基础支持这里所介绍的各种驱动电路的结果。理想的零欧姆阻抗传输介质,其电感和电容分布在传输电缆上。电感和电容都会降低线路的传输质量。每个输入端通过菊花链或环路以高阻抗连接到线路,并且每个输入端至少增加几个皮卡天线的电容。典型的传输线阻抗(ZO)定义了线路类型。在方程式1中,阻抗由线路电感(LT)除以线路电容(CT)的平方根计算:

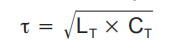

同样,线路电感和电容确定传输线的延迟时间,如等式2所示:

对于对称记录道,ZO的典型值为240Ω,同轴电缆的典型值为75Ω或50Ω。对于印刷电路板(PCB)上的总线线路,在高数据速率总线系统中,ZO有时会降低到30Ω到40Ω。一般来说,公交系统越复杂,ZO就越低。因为它增加了传输介质的电容,一个复杂的系统降低了典型的线路阻抗,从而对这里使用的线路驱动器提出了更高的驱动要求。

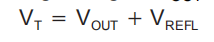

传输线几乎总是端接在发射端,而总是端接在接收机端。未端接的线路会产生信号反射,降低脉冲保真度。驱动电路通过线路传输输出电压(VOUT)。信号出现在线路的末端,当没有正确终止时将被反射。VOUT的反射部分称为VREFL,返回给驱动程序。发射信号是原始信号VOUT和反射的VREFL之和。

反射信号的大小取决于典型的线路阻抗(ZO)和终端电阻Z1的值。

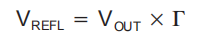

Γ表示反射系数,由式5描述。

Γ的变化范围为-1到+1。

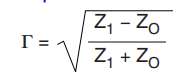

方程5角点处的条件如下:

未端接的驱动电路使情况更加复杂。VREFL第二次反射到驾驶员侧,像乒乓球一样来回游荡在线路上。当这种情况发生时,通常不可能在接收器侧恢复输出信号VOUT。

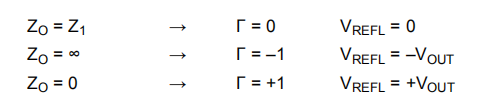

图33所示的图将BUF602用作线路驱动器。BUF602具有高输入阻抗和低输出阻抗,因此无论何时需要缓冲器,它都是理想的选择。

自偏压,低阻抗中间电源电压基准

将中点基准与BUF602结合使用,可以创建从直流到250MHz的低阻抗基准。

图34使用0.1μF外部电容器过滤噪声。

自参考,交流耦合宽带缓冲器

无论何时需要高速交流耦合缓冲器,都应该考虑BUF602。BUF602的一个特点是提供中间参考电压,节省外部元件和功耗。建议在中间电源基准输出端安装一个电容器,以限制由两个50kΩ内部电阻器产生的中间电源参考电压的噪声贡献。

设计工具

演示固定装置

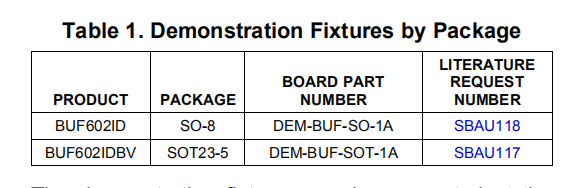

有两块印刷电路板(PCB)可用于辅助使用BUF602在其两个封装选项中对电路性能进行初步评估。这两种产品都是免费提供的未填充多氯联苯,并附有用户指南。这些固定装置的汇总信息如表1所示。

可在德克萨斯仪器公司网站上索取演示装置通过BUF602产品文件夹。

宏模型和应用程序支持

在分析模拟电路和系统的性能时,使用SPICE对电路性能进行计算机模拟是非常有用的。这对于视频和射频放大器电路尤其如此,因为寄生电容和电感会对电路性能产生重大影响。可通过TI网站获得BUF602的SPICE模型(网站). 这些模型可以很好地预测各种运行条件下的小信号交流和瞬态性能。它们在预测谐波失真或dG/dP特性方面做得不好。这些型号并没有试图在其小信号交流性能方面区分封装类型。

输出电流和电压

BUF602提供的输出电压和电流能力通常在宽带缓冲器中没有。在+25°C的空载条件下,输出电压相对于任一供电轨的摆动通常小于1.2V;+25°C的摆动限制在任一供电轨的1.2V范围内。在15Ω负载(最小测试负载)中,测试其输出超过±60毫安。

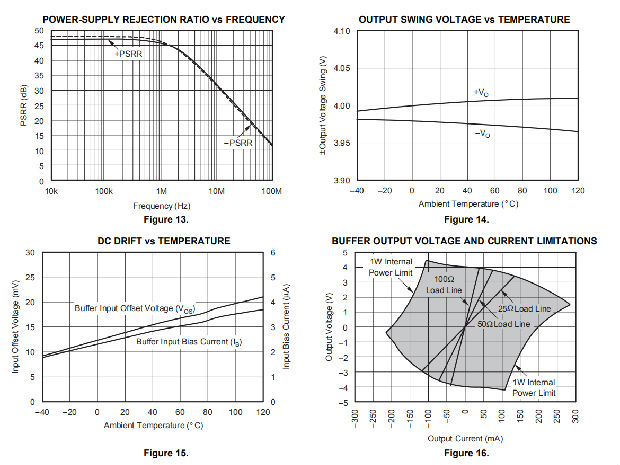

上述规范虽然在行业中很熟悉,但分别考虑了电压和电流限制。在许多应用中,它是电压×电流或V-I乘积,它与电路运行更为相关。参考典型特性中的缓冲器输出电压和电流限制图(图16)。此图的X轴和Y轴分别显示零电压输出电流限制和零电流输出电压限制。四个象限给出了BUF602输出驱动能力的更详细的视图,注意到该图以1W最大内部功耗的安全操作区域为界。将电阻负载线叠加到曲线图上表明,BUF602可以在不超过输出能力或1W功耗限制的情况下,将±3V驱动到25Ω或±3.5V到50Ω。

最小规定的输出电压和电流过温是通过最坏情况模拟在极端低温下设定的。只有在冷启动时,输出电流和电压才会降低到电气特性表中所示的数值。当输出晶体管提供功率时,结温将升高,降低VBE(增加可用输出电压摆幅)和增加电流增益(增加可用输出电流)。在稳态运行中,由于输出级结温将高于规定的最低工作环境温度,因此可用输出电压和电流将始终大于超温规范中所示的值。

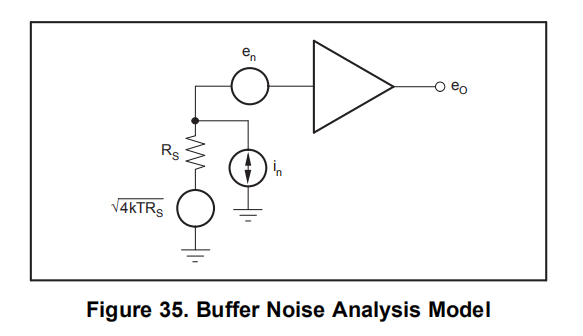

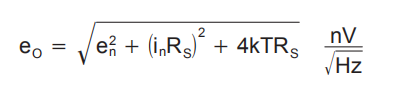

对于缓冲器,噪声模型如图35所示。方程6显示了输出噪声电压的一般形式,如图35所示。

热分析

在极端的工作条件下,可能需要BU602的强制通风或高功率运行。最大期望结温将设置如下所述的最大允许内部功耗。在任何情况下,最高结温不得超过150℃。

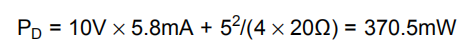

工作结温度(TJ)由TA+PD×θJA给出。总内部功耗(PD)是静态功率(PDQ)和输出级(PDL)消耗的附加功率之和。静态功率就是指定的空载供电电流乘以整个部件的总供电电压。PDL将取决于所需的输出信号和负载,但对于接地电阻负载,当输出固定在等于任一电源电压的1/2时(对于相等的双极电源),PDL将处于最大值。在这种情况下,PDL=VS2/(4×RL)。

注意,决定内部功耗的是输出级的功率而不是负载。

作为最坏情况的例子,使用首页电路中的BUF602IDBV,在最高指定环境温度+85°C并驱动接地20Ω负载的情况下,计算最大TJ。

最大TJ=+85°C+(0.37W×150°C/W)=141°C。

尽管这仍低于规定的最高结温,但出于系统可靠性考虑,可能需要较低的测试结温。如果负载要求电流被强制输入正输出电压的输出端或来自负输出端的电流,则可能出现最高的内部损耗。这使得高电流通过输出晶体管中的一个大的内部电压降。典型特性中显示的输出V-I图(图16)包括在这些条件下1W最大内部功耗的边界。

电路板布局指南

要实现最佳性能与高频放大器,如BUF602需要仔细注意板布局寄生和外部元件类型。优化性能的建议包括:

a)、将所有信号输入/输出引脚对任何交流接地的寄生电容降至最低。输出管脚上的寄生电容会导致不稳定:在不可逆的输入端,寄生电容会与源阻抗发生反应,导致无意中的带宽限制。为了减少不必要的电容,信号I/O引脚周围的所有地面和电源平面上都应该打开一个窗口。否则,地面和动力飞机应该在其他地方保持完整。

b)、缩短距离(<0.25“)从电源引脚到高频0.1μF去耦电容器。在设备引脚处,接地和电源平面布局不应靠近信号输入/输出引脚。避免狭窄的电源和接地痕迹,以尽量减少引脚和去耦电容器之间的电感。电源连接应始终与这些电容器断开连接。两个电源之间的可选电源去耦电容器(0.1μF)(用于双极操作)将改善二次谐波失真性能。主电源引脚上还应使用较大的(2.2μF至6.8μF)去耦电容器,在较低频率下有效。这些可以放置在离设备稍远的地方,并且可以在PCB的相同区域中的多个设备之间共享。

c)、仔细选择和放置外部组件将保持BUF602的高频性能。电阻器应为非常低的电抗类型。表面贴装电阻工作最好,并允许更紧凑的整体布局。金属薄膜或碳成分,轴向引线电阻也能提供良好的高频性能。同样,保持他们的引线和PCB痕迹尽可能短。切勿在高频应用中使用线绕式电阻器。

d)、与板上其他宽带设备的连接可以通过短的、直接的路径或通过板载传输线进行。对于短连接,将跟踪和到下一个设备的输入视为集中电容负载。应使用相对较宽的迹线(50至100 mils),最好在其周围打开地面和动力飞机。如果需要较长的记录道,并且双端接传输线固有的6dB信号损耗是可接受的,则使用微带线或带状线技术实现匹配阻抗传输线(请参阅有关微带和带状线布局技术的ECL设计手册)。50Ω的环境通常不需要在船上,事实上,更高的阻抗环境将改善失真,如失真与负载图所示。

e)、不建议将BUF602这样的高速零件套入。插座引入的额外引线长度和针对针电容会产生一个非常麻烦的寄生网络,几乎不可能实现平滑、稳定的频率响应。将BUF602焊接到电路板上可获得最佳效果。

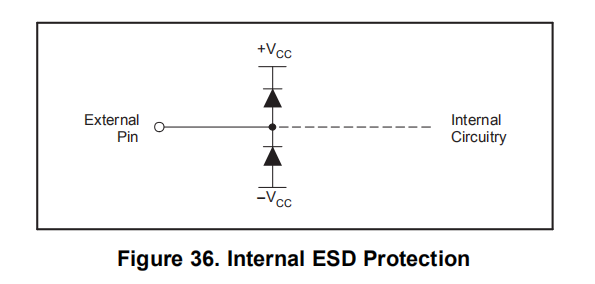

输入和ESD保护

BUF602是建立在一个非常高速互补双极工艺。对于这些非常小的几何器件,内部结击穿电压相对较低。这些细分反映在绝对最大评级表中。如图36所示,所有设备引脚都由内部ESD保护二极管保护电源。

这些二极管提供适度的保护,以输入高于电源的过驱动电压。保护二极管通常可支持30mA连续电流。如果可能有更高的电流(例如,在带有±15V电源部件驱动至BUF602的系统中),应在两个输入端添加限流串联电阻器。保持这些电阻值尽可能低,因为高值会降低噪声性能和频率响应。