DIR1701点击型号即可查看芯片规格书

特征

■标准数字音频接口接收器(EIAJ1201)

■采样率:32/44.1/48/88.2/96 kHz

■恢复128/256/384/512 fs系统时钟

■非常低抖动的系统时钟输出(通常为80ps)

■片上主时钟振荡器,只需要外部12.000 MHz或16.000 MHz晶体

■可选输出PCM音频数据格式

■使用块启动信号输出用户位数据、标志信号和信道状态数据

■单电源+3.3V电源

■包装:28 SSOP

应用

■AV接收器

■ MD播放器

■ DAC单元

说明

DIR1701是一种数字音频接口接收器(DIR),它根据AES/EBU、IEC958、S/PDIF和EIAJCP340/1201消费者和专业格式接口标准接收和解码高达96 kHz的音频数据。DIR1701将信道状态位和用户位直接解复用到串行输出引脚,并为最重要的信道状态位提供专用的输出引脚。

DIR1701的显著优点是具有96 kHz的采样率能力和通过采样周期自适应控制跟踪(SpAct)系统实现的低抖动时钟恢复。输入信号重新锁定与专利采样周期自适应控制跟踪系统,以获得最大质量。这两个功能是最新的消费类和专业音频设备所必需的,其中DIR有一个接口到任何类型的delta-sigma型ADC/DAC,采样率为96khz。

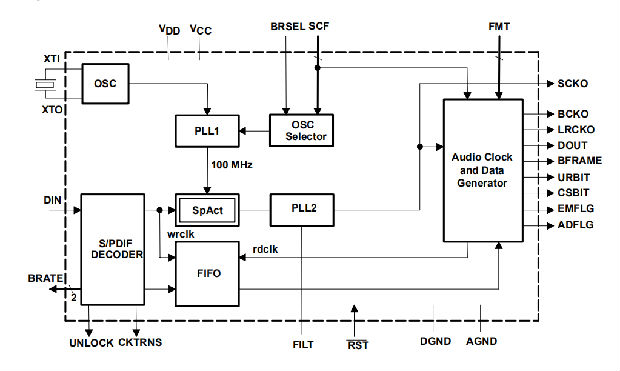

方块图

基本运算理论

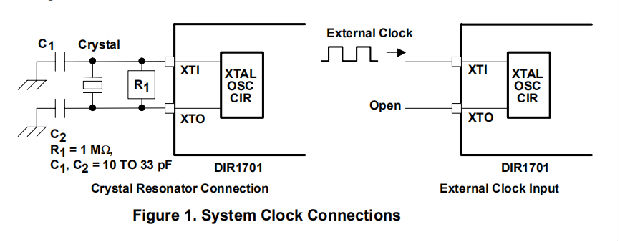

DIR1701有两个PLL,PLL1和PLL2。SpAct(Sampling Period Adaptive Controlled Tracking,采样周期自适应控制跟踪)系统是一种新开发的时钟恢复结构,它能从S/PDIF数据输入中获得非常低的时钟抖动。DIR1701需要一个系统时钟输入来操作SpAct;内部PLL1提供100 MHz的执行时钟。系统时钟可以通过在XTI/XTO引脚上连接合适的晶体谐振器或在XTI引脚上应用外部时钟输入来获得,如图1所示。内部PLL2利用SpAct频率估计器的输出信号生成系统时钟SCKO。

当S/PDIF输入信号停止时,SCKO保持最新跟踪频率。此外,DIR1701通过解锁引脚的高电平输出指示解锁状态。当S/PDIF信号重新启动时,使用SpAct估计器,PLL将以非常低的抖动锁定在1ms左右。然后,DIR1701通过解锁引脚的低电平输出指示锁定状态。在这种状态下,BRATE管脚表示输入S/PDIF信号的实际比特率。

系统时钟输出

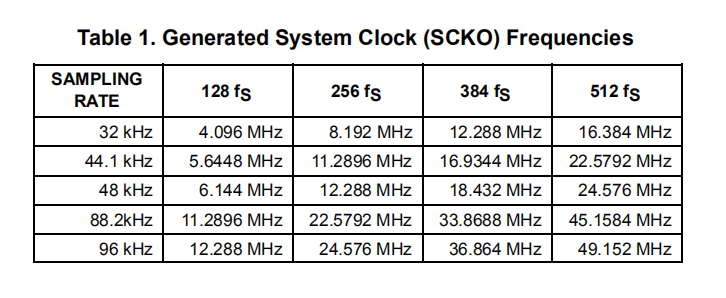

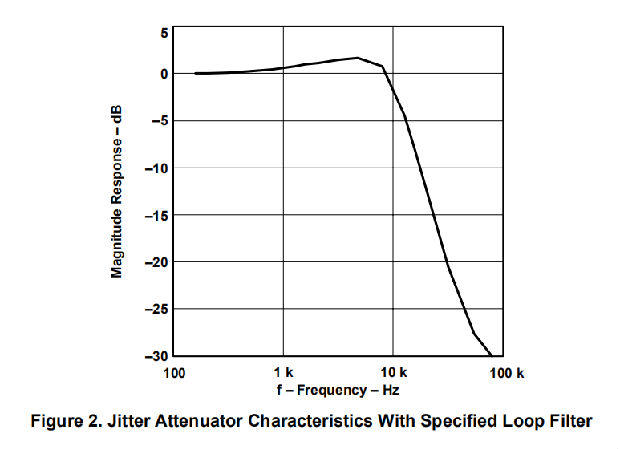

DIR1701的主要功能是从数字音频传输线恢复音频数据和低抖动时钟。可以生成的时钟是SCKO(128/256/384/512fs,如表1所示)、BCKO(64fs)和LRCKO(1fs)。SCKO是模拟锁相环中压控振荡器(VCO)的输出。锁相环功能由压控振荡器、相位和频率检测器以及外部二阶环路滤波器组成。闭环传递函数指定了PLL抖动衰减特性,如图2所示。

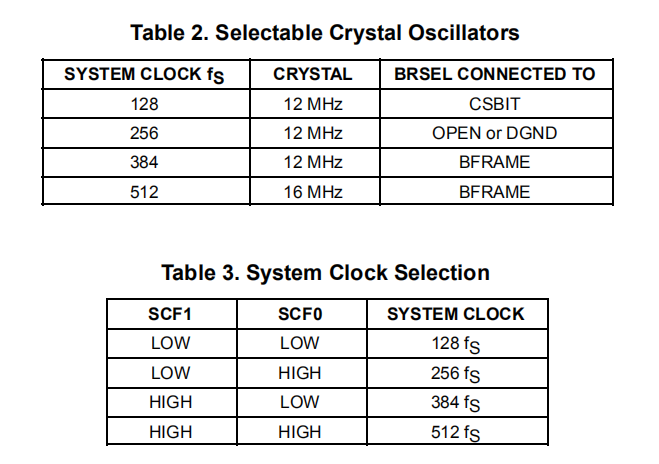

应通过将BRSEL引脚连接到表2中所示的输出引脚BFRAME或CSBIT之一来定义内部PLL的晶体频率。12MHz晶体谐振器可用于128fs(CSBIT)、256fS(开放)和384fs(BFRAME)。512fs(BFRAME)采用16mhz晶体谐振器。系统时钟频率可通过SCF0、SCF1引脚(如表3所示)的控制数据进行设置;在应用复位之前,该数据必须稳定。

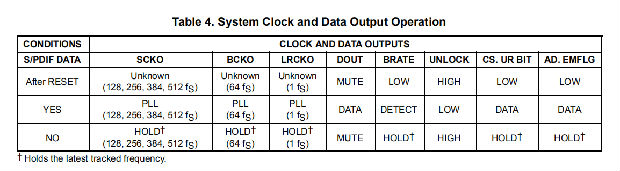

表4显示了系统的状态以及音频时钟和标志的状态。晶体谐振器或外部时钟输入所需的系统时钟精度为±500ppm。

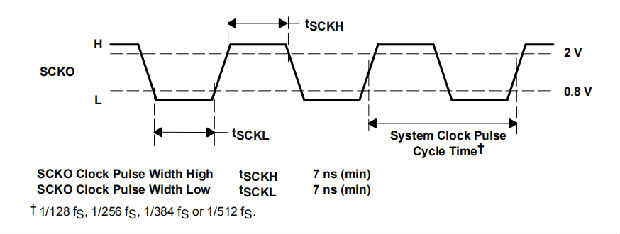

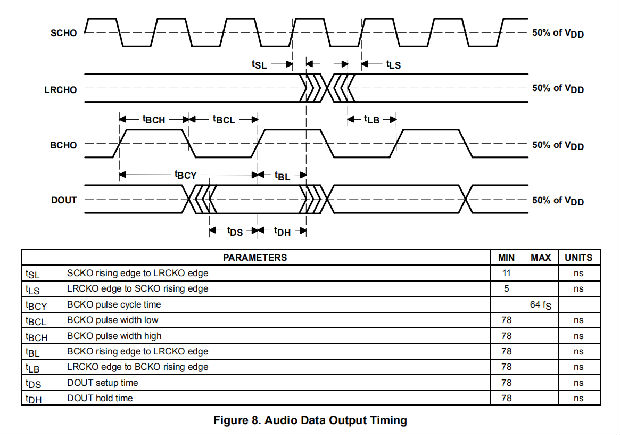

SCKO定时

比特率检测

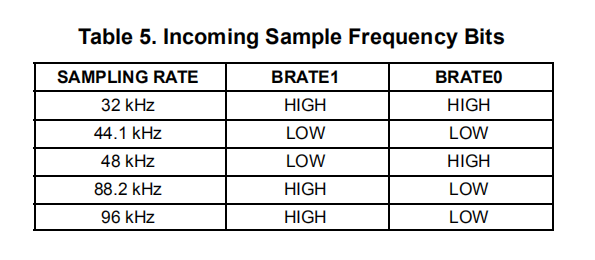

通过使用间隔频率估计器(而不是S/PDIF信道状态位),DIR1701自动检测输入S/PDIF信号的采样率并指示BRATE管脚处的频率。

表5列出了报告的频率范围。除88.2和96 kHz外,这些采样率与S/PDIF规范中定义的信道状态位相同。当比特率为88.2或96 kHz时,指示器显示相同的HL值。S/PDIF规范中未定义此状态。

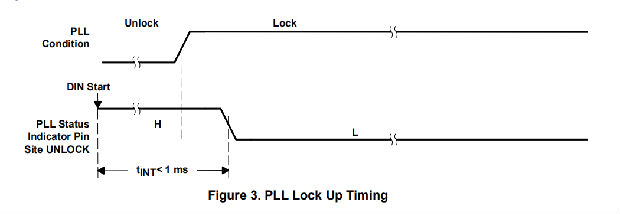

锁相环运行时序规范

锁定时间

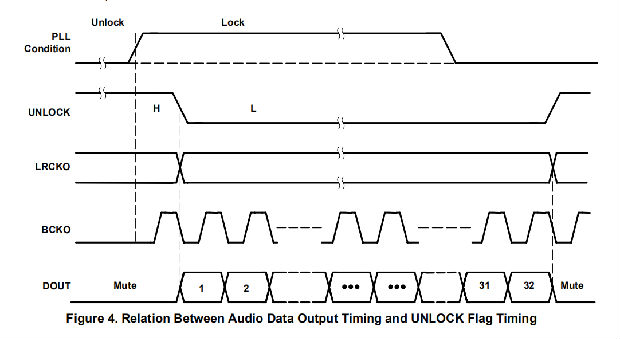

音频数据输出时序与锁相环状态指示时序的关系

当模拟PLL仍然被解锁并且S/PDIF信号开始时,在至少10个上升沿之后,S/PDIF解码器可以检测到输入的S/PDIF信号。DOUT引脚变低(静音),直到模拟锁相环锁定。该静音周期tINT小于1ms(模拟锁相环锁定时间小于0.5ms)。当解码器检测到输入的S/PDIF信号已停止时,UNLOCK在下一个LRCKO转换处变高。SCKO将其频率保持在最新跟踪的比特率。

当移除复位后S/PDIF信号不存在时,DIR1701音频时钟(SCKO、BCKO、LRCKO)的频率未知。

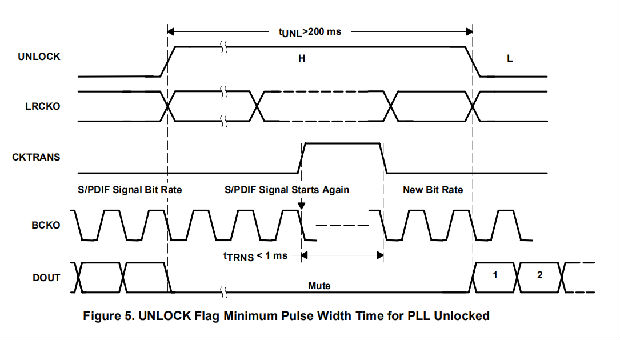

解锁标志最小脉冲宽度时间

案例A PLL解锁时

当锁相环解锁时,解锁标志引脚为高电平,音频数据输出DOUT变低(静音)。静音周期tUNL至少为200 ms。在此期间,SCKO、BCKO和LRCKO频率保持最新跟踪频率。

如果在此解锁周期内再次连接S/PDIF信号,则比特率在至少1毫秒后(在解锁标志变低之前)更改为输入信号频率。CKTRNS引脚表示SCKO的有效性。当CKTRNS较高时,SCKO、BCKO和LRCKO的频率处于状态间的转换状态。

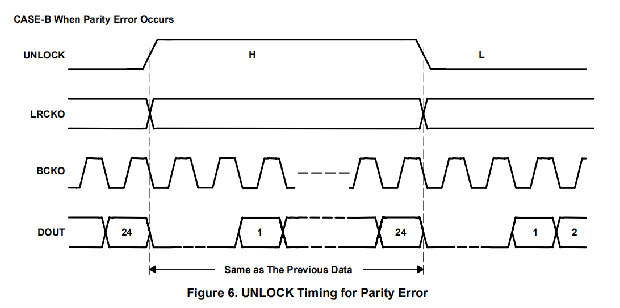

发生奇偶校验错误时的情况B

当在一个子帧间隔中发生奇偶校验错误时,解锁在该子帧期间变为高,然后在下一个到达的子帧处返回低。

在这个奇偶校验错误的子帧期间,数据输出将保存每个信道的先前数据。

PCM音频接口

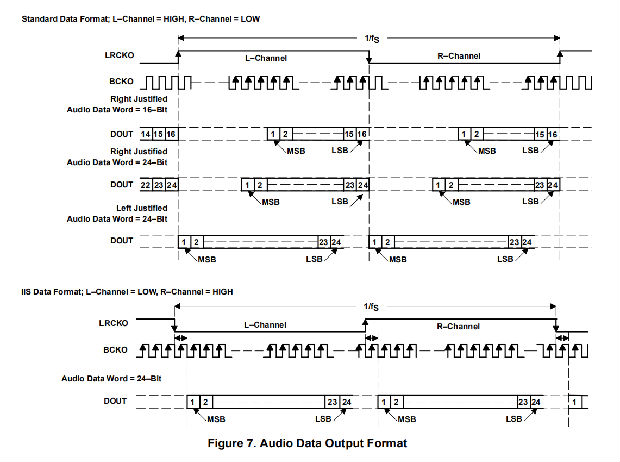

DIR1701可以生成标准格式的16位或24位输出数据和IIS格式的24位输出数据。

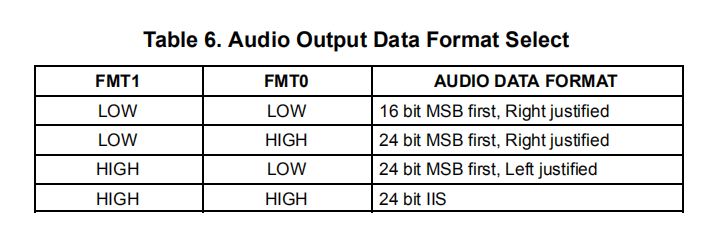

使用格式引脚FMT1、FMT0选择DIR1701的PCM音频接口格式。表6显示了FMT引脚配置。

专业和消费应用的专用输出引脚

DIR1701具有并行输出引脚,适用于专业和消费应用。在专业模式下,去加重标志EMFLG表示50/15-μs的时间常数预加重。当CSBIT字节0的位0为高时,设置专业模式。当CSBIT字节0的第2至4位为110时,EMFLG变为高。在其他情况下,EMFLG较低。音频/非音频标志ADFLG表示S/PDIF数据模式,即CSBIT字节0的第1位。当ADFLG低时,S/PDIF数据包括PCM音频信号。在其他情况下,ADFLG很高。

在消费者模式下,EMFLG表示2通道音频,预加重时间为50/15-μs。当CSBIT字节0的位0为低时,设置消费者模式。当CSBIT字节0的位3到5为100时,EMFLG变为高。在其他情况下,EMFLG较低。ADFLG信号指示S/PDIF是否包括数字数据,例如AC-3。当CSBIT字节0的位1为高时,传入的S/PDIF包括非音频信号。在其他情况下,ADFLG较低。

这些专用输出引脚仅检查L-ch CS信息。DIR1701在专业模式下不支持CRC检查功能。至于其他标志,专业和消费者应用的CS位和用户位直接由CSBIT(引脚15)和URBIT(引脚16)的串行模式提供。这些针脚表示L-ch和R-ch信息顺序。

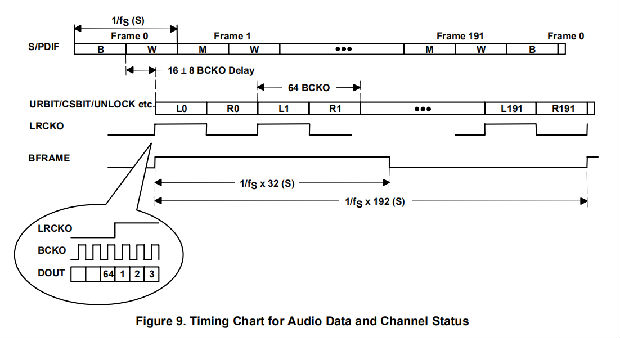

音频数据和时钟定时如下所述。当相应的子帧到达时,串行输出数据在16±8 BCKO时钟之后开始。当B子帧到达时,BFRAME pin在1/fs x 32(s)期间变为高,然后BFRAME在32帧后返回低。

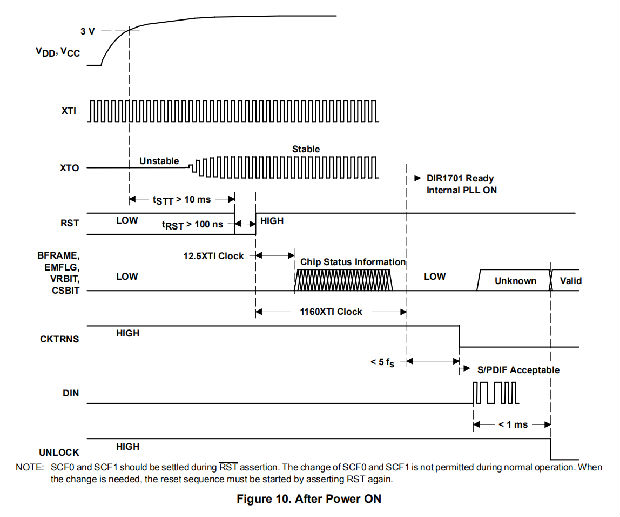

复位顺序

DIR1701需要在上电后进行外部复位操作。图10显示了通电后的重置顺序。当内部复位序列完成且CKTRNS变为低电平时,DIR1701已准备好接收S/PDIF信号。BFRAME、EMFLG、URBIT和CSBIT引脚用于RST上升沿到CKTRN下降沿的配置。当CKTRNS变低后,S/PDIF信号被接受。RST,tRST的最小脉冲宽度为100ns。电源达到3V后的RST延迟应至少为10ms。RST低时,除CKTRN和UNLOCK外的所有输出引脚均为低。

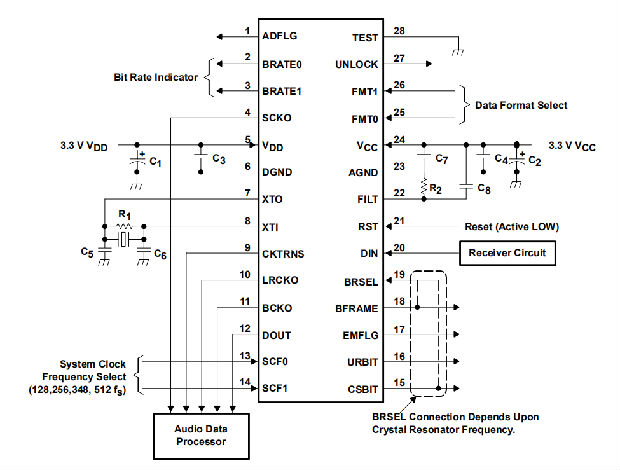

典型电路连接

C1、C2:旁路电容器,1μF至10μF

C3,C4:旁路电容器,0.01μF至0.1μF

C5,C6:OSC电容器,10至33 pF

C7:回路滤波电容器,0.022μF

C8:纹波电容器,0.0022μF

R1:OSC电阻器,1 MΩ

R2:回路滤波电阻,6.8 kΩ++

注:A.所有线性尺寸单位均为毫米。

B、 本图纸如有更改,恕不另行通知。

C、 主体尺寸不包括不超过0.15的模具飞边或突出物。

D、 属于JEDEC MO-150。