DS92001点击型号即可查看芯片规格书

特征

●单电源+3.3V电源

●B/LVDS接收器输入接受LVPECL信号

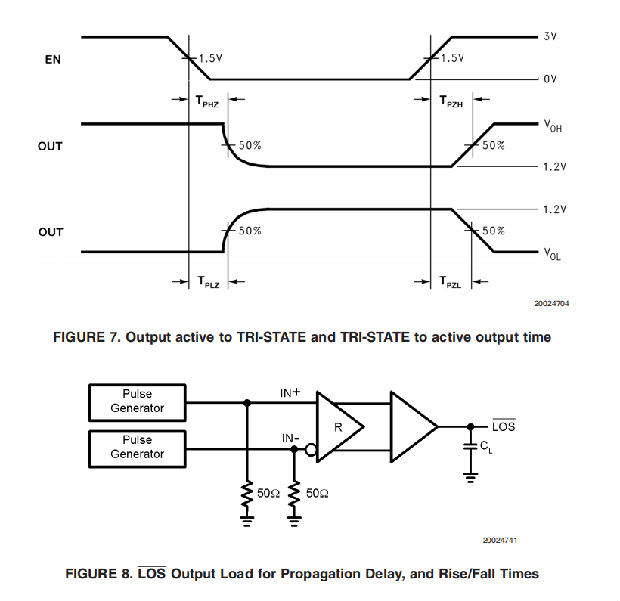

●三态输出

●信号丢失(LOS)引脚检测非驱动总线

●接收器输入阈值<±100 mV

●1.4ns的快速传播延迟(典型值)

●低抖动400 Mbps全差分数据路径

●兼容BLVDS 10位SerDes(40MHz)

●兼容ANSI/TIA/EIA-644-A LVDS标准

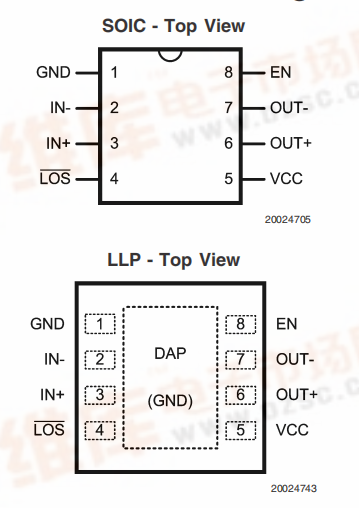

●提供SOIC和节省空间的LLP封装

●工业温度范围

一般说明

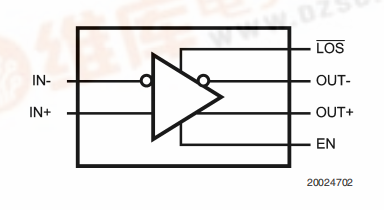

DS92001 B/LVDS-BLVDS缓冲器接收BLVDS输入信号并提供BLVDS输出信号。在许多大型系统中,信号分布在背板上,系统速度的限制因素之一是“存根长度”或传输线与单个卡上的非标准接收器之间的距离。尽管人们普遍认为,为了最大限度地提高系统性能,这个距离应该尽可能短,但现实世界中的封装连接器通常很难使存根尽可能短。

DS92001的边缘转换针对开关频率在200 MHz或以下的多点背板进行了优化。在一些可能存在长存根的系统中,输出边缘速率非常关键,利用慢转换可以获得更长的存根长度。

在LLP(无铅引线框架封装)封装中提供的DS92001将允许接收器输入非常靠近主传输线,从而提高系统性能。

宽输入动态范围允许DS92001接收来自LVPECL和LVDS的差分信号消息来源。这个将允许设备同时充当LVPECL BLVDS转换器的角色。

LOS引脚在输入端检测非驱动B/LVDS总线状态,并提供有效的低输出。当输入未被驱动时,LOS引脚可与设备的输出使能引脚(EN)相连,以产生三态输出状态。LOS引脚也可在本地用于通知系统总线状态。

连接和方框图

功能操作

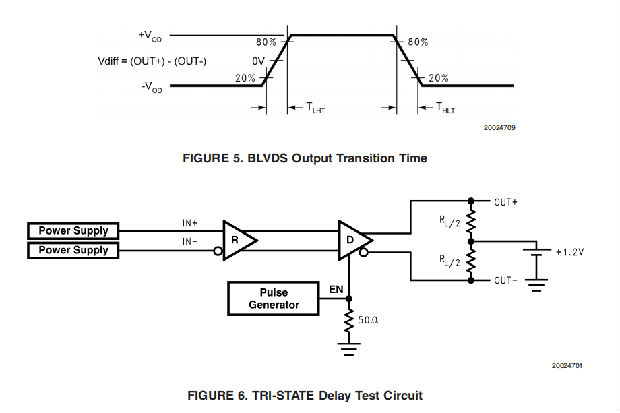

订购信息

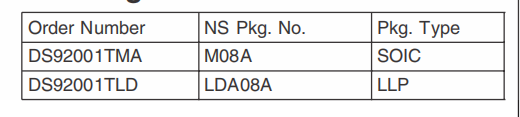

直流测试电路

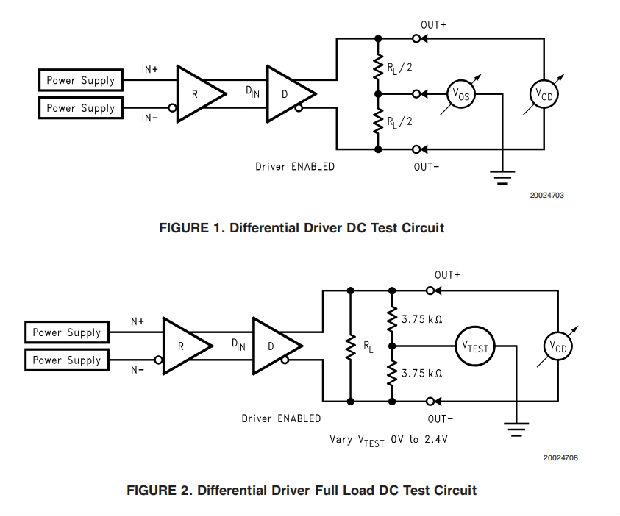

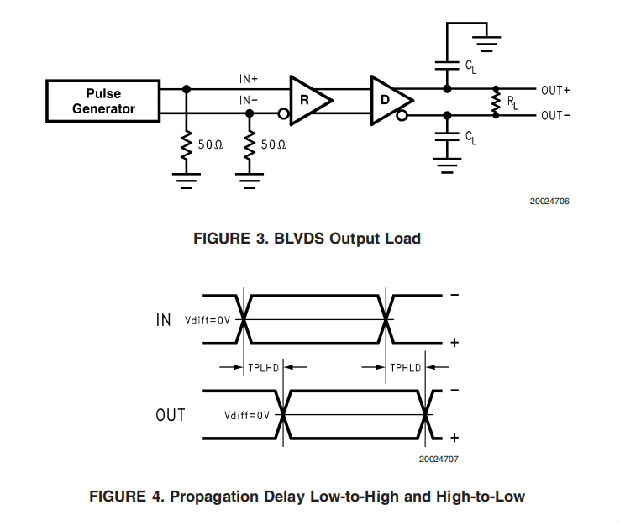

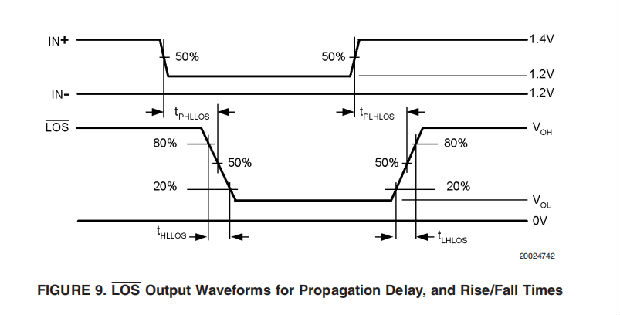

交流测试电路和时序图

典型应用

申请信息

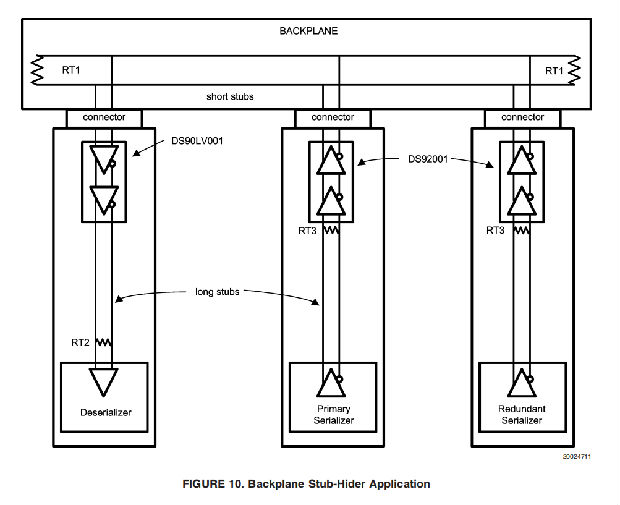

DS92001可用作“存根隐藏器”。在许多系统中,信号分布在背板上,系统速度的限制因素之一是“存根长度”或传输线与单个卡上未受限制的接收器之间的距离。见图10。虽然人们普遍认为,为了最大限度地提高系统性能,这个距离应该尽可能短,但现实世界中的封装问题和PCB设计往往使存根很难像设计者希望的那样短。DS92001是LLP(无铅引线框架封装)封装中提供的,它允许将接收器放置在离主传输线非常近的背板上,或者非常靠近卡上的连接器,从而提高系统性能。到LVDS接收器的较长记录道可以放在DS92001之后。这种非常小的LLP封装比SOIC封装节省了75%的空间。

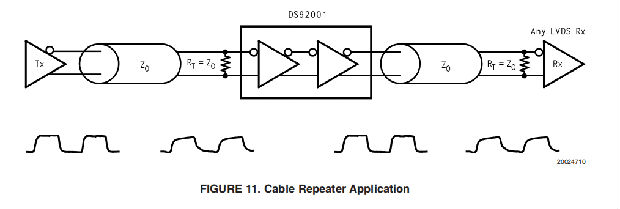

DS92001也可以用作中继器,如图11所示。信号被恢复,并以最大强度重新驱动下一段。DS92001还可以用作电平转换器,因为它接受LVDS、BLVDS和LVPECL输入。

视距探测

LOS引脚在设备正常运行(| 100 | mV≤VID≤| 2 | V)期间呈现逻辑高电平。当正常传输停止时,LOS引脚被断言为低。当信号源被移除或关闭时(三态)。当输入信号电压(VID)小于| 10 |毫伏时,LOS引脚被断言为低。对于正常操作,提供给B/LVDS输入的上升和下降时间必须快于20纳秒(20%到80%),以避免信号检测丢失。典型的输入跃迁在1-3纳秒范围内。在信号衰减的情况下(如有效信号到三态信号),斜率应该是单调的,以避免视线检测中的小故障。

视距检测-输出低

电源去耦建议

旁路电容器必须用在电源引脚上。在电源引脚处并联使用高频陶瓷(建议采用表面贴装)0.1μF和0.01μF电容器,最小值电容器最靠近设备电源引脚。印刷电路板上附加的分散电容器将改善去耦。应使用多个通孔将去耦电容器连接到电源平面。10μF(35V)或更大的固体钽电容器应连接在电源和接地之间的印刷电路板上的电源入口点。

PC板注意事项

至少使用4个PCB板层(从上到下):LVDS信号、接地、电源、TTL信号。

将TTL信号与LVDS信号隔离,否则TTL信号可能耦合到LVDS线路上。最好将TTL和LVDS信号放在不同的层上,这些层由电源/地平面隔离。

使驱动器和接收器尽可能靠近(LVDS端口侧)连接器。

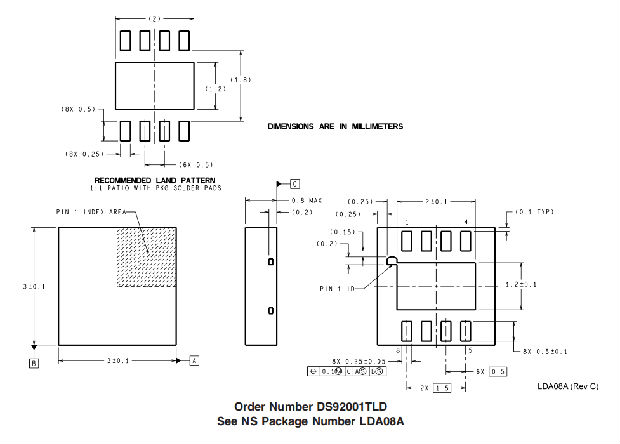

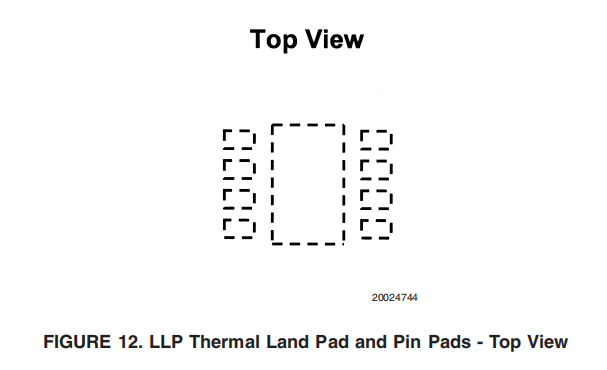

对于LLP封装的PC板考虑,请参考应用说明AN-1187“无铅引线框架封装”。需要注意的是,优化信号完整性(将抖动和噪声耦合降至最低),LLP热接地垫是一个金属(通常是铜)矩形区域,位于封装下方,如图12所示,应连接到地面,并与PCB上暴露的焊盘尺寸匹配(1:1比率)。

微分记录道

使用与传输介质(即电缆)和终端电阻的不同阻抗匹配的受控阻抗轨迹。一旦差分对迹线离开IC,应尽可能靠近它们(短线的长度应小于10毫米)。这将有助于消除反射,并确保噪声耦合为常见现象-模式。输入事实上,我们已经看到,相距1mm的差分信号比相距3mm的迹线辐射的噪声要小得多,因为磁场相消的痕迹越近越好。此外,在差分线路上产生的噪声更有可能表现为接收器所发射的共模。

匹配迹线之间的电气长度以减少歪。歪一对信号之间的相位差意味着信号之间的相位差,这会破坏差分信号的磁场抵消优势,从而产生电磁干扰。对于不同的轨迹,不要仅仅依赖自动布线功能。仔细检查尺寸以匹配不同的阻抗,并为差动提供隔离行。最小化线上过孔和其他不连续的数量。

避免90˚圈(这会导致阻抗不连续)。使用圆弧或45˚斜面。

在一对记录道内,两个记录道之间的距离应最小化,以保持接收器的共模抑制。在印刷电路板上,该距离应保持恒定,以避免微分阻抗的不连续性。允许在连接点处出现轻微违规。

终止

使用与差分阻抗或传输线最匹配的终端电阻。对于点对点链路,电阻应在90Ω和130Ω之间。多点(中间驱动器)或多点配置通常在两端终止。由于负载效应,终端值可能低于100Ω,并且在50Ω到100Ω的范围内。记住,电流模式输出需要终端电阻来产生差分电压。

表面贴装1%-2%的电阻是最好的。PCB存根、元件引线以及从终端到接收器输入的距离应最小化。终端电阻器和接收器之间的距离应小于10毫米(最大12毫米)。

探测LVDS传输线

始终使用高阻抗(>100kΩ)、低电容(<2pf)示波器探头,范围宽(1GHz)。不恰当的探测会产生欺骗的结果。

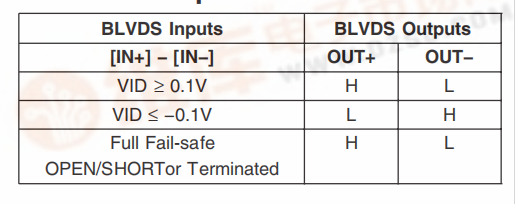

故障保护功能

BLVDS接收器是一种高增益、高速设备,它将一个小的差分信号(30mV)放大到BLVDS输出驱动电平。由于接收机的高增益和严格的阈值,应注意防止噪声作为有效信号出现。

接收器的内部故障安全电路设计用于提供/吸收少量电流,为浮动、端接或短路的接收器输入提供故障保护(高电平输出电压)。

1、终止输入。如果驱动器断开(电缆拔出),或驱动器处于断电状态,BLVDS输出将再次处于高状态,即使电缆100的末端也是如此Ω输入端接电阻器。拔下的电缆可以成为一个浮动天线,可以接收噪音。如果电缆接收到超过10mV的差分噪声,接收器可能会将该噪声视为有效信号并进行切换。为了确保任何噪声都被视为共模而不是差分,应该使用平衡互连。双绞线电缆将提供比扁平带状电缆更好的平衡。

2、输入短路。如果发生使接收器输入短路的故障,从而导致0V差分输入电压,BLVDS输出将保持在高状态。短路输入故障保护电压范围为0伏至2.4伏。

3、外部偏压。外部低值上拉和下拉电阻器(用于更强的偏置)可用于在存在更高噪声水平的情况下提高故障安全性。上拉和下拉电阻应在5k范围内Ω至15kΩ使驱动器的负载和波形失真最小化的范围。共模偏置点应设置为大约1.2V(小于1.75V),以与内部电路兼容。更多信息,请参考应用说明AN-1194“LVDS接口的故障保护偏置”。

物理尺寸英寸(毫米),除非另有说明。