CS42406点击型号即可查看芯片规格书

D/A特征

•24位转换

•5伏时动态范围为102分贝

•-91分贝THD+N

•带软斜坡的数字音量控制

–119分贝衰减

–1分贝步长

–零交叉点击自由转换

•仪控和SPI™ 主机控制端口

•ATAPI混合

•低时钟抖动灵敏度

•Popguard Technology®用于控制点击和弹出

A/D特性

•24位转换

•5 V时105 dB动态范围

•-98分贝THD+N

•先进的多位Delta-Sigma体系结构

•高通滤波器消除直流偏移

•自动模式选择

系统特性

•直接接口,5 V至1.8 V逻辑电平

•支持独立的同步ADC/DAC采样率

•作为时钟主从操作

•支持所有音频采样率,包括192 kHz

•单端输入/输出

•模拟/数字核心电源从3.3V到5V

独立模式功能集

•系统特性

–ADC串行音频端口主或从操作

–独立ADC和DAC复位/断电

–256x或384x MCLK/LRCK比率可选

•D/A特征

–静态样本自动静音

–44.1 kHz 50/15微秒可调

–可选串行音频接口格式

*左对齐最多24位数据

*最多24位数据

*右对齐,16位数据

*右对齐,24位数据

•A/D特征

–串行音频端口主或从操作

–从机模式下的自动模式选择

–高通滤波器

–可选串行音频接口格式

*左对齐高达24位

*最多24位数据

•控制端口模式功能集

•D/A特征

–可选自动静音

–可选32、44.1和48 kHz去加重滤波器

–可配置的ATAPI混合功能

–可配置音量和静音控制

–可选串行音频接口格式

*左对齐高达24位

*最高24位

*右对齐16、18、20和24位

一般说明

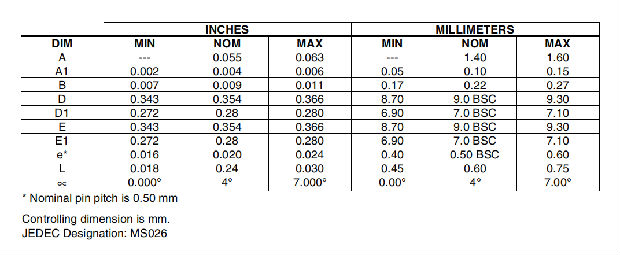

CS42406是一款低成本的集成音频编解码器。CS42406执行立体声模拟到数字(A/D)转换和6个通道的数字到模拟(D/A)转换,最高24位串行值的采样率高达200 kHz。

D/A提供了一个以1db步长运行的音量控制。它结合了可选择的软斜坡和零交叉过渡功能,以消除点击和弹出。

D/A的集成数字混音功能允许多种输出配置,从通道交换到立体声到单声道向下混音。

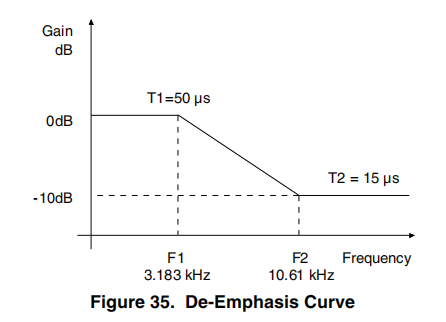

对于32、44.1和48 kHz的采样率,可使用标准50/15μs去加重,以与使用50/15μs预加重技术掌握的数字音频程序兼容。

集成电平转换器允许CS42406和其他在各种逻辑电平上运行的设备之间进行简单的接口。

高通滤波器可用于A/D的左右通道。这允许A/D消除不需要的直流偏移。

CS42406动态范围宽,失真小,噪音低,非常适合A/V接收器、DVD接收器和机顶盒系统。

订购信息

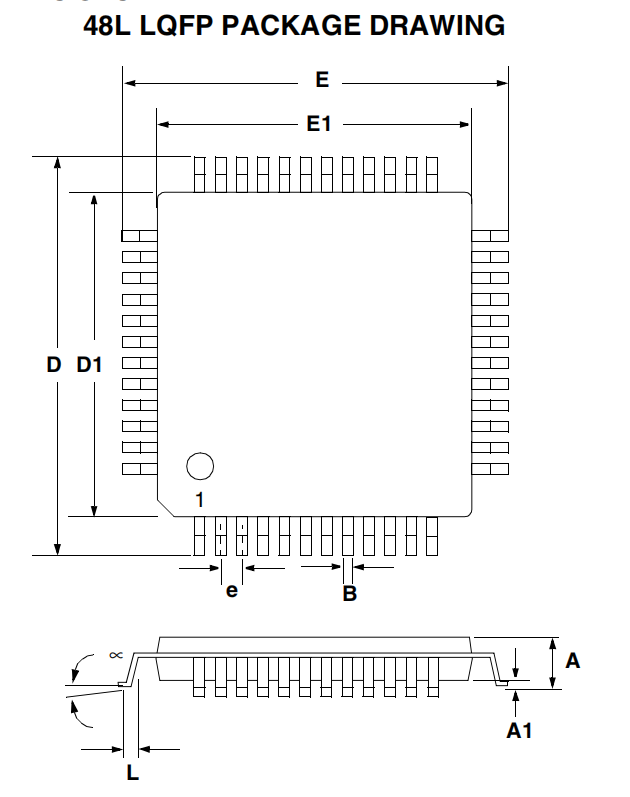

CS42406-CQZ-10°至70°C 48针LQFP

CDB42406评估委员会

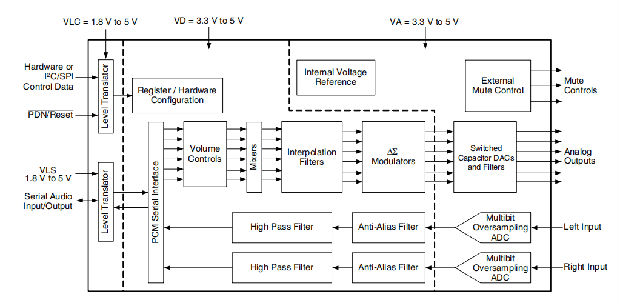

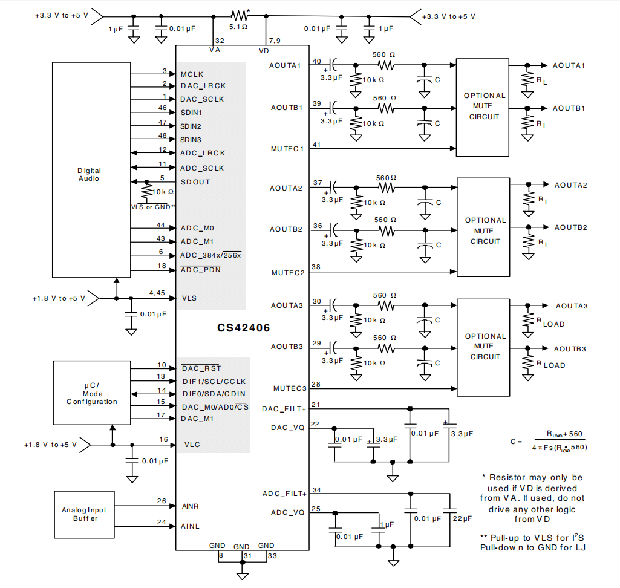

见图1-2。RL和CL反映了内部运放稳定性和信号完整性所需的最小电阻和最大电容。在这种电路拓扑结构中,CL将有效地移动输出级中双极放大器的主极点。将该值增加到推荐的100 pF以上可能会导致内部运算放大器变得不稳定。

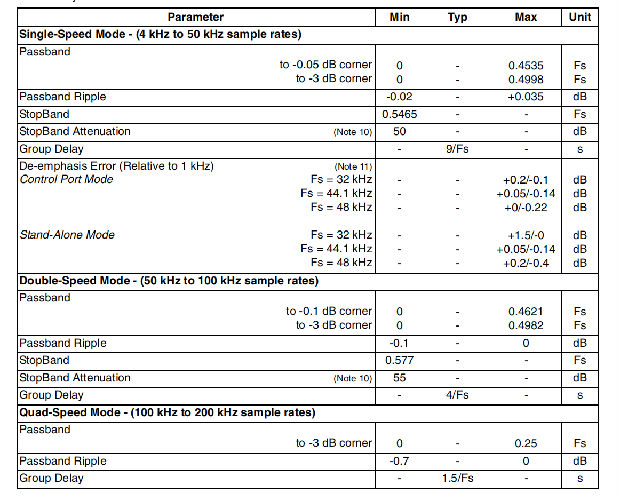

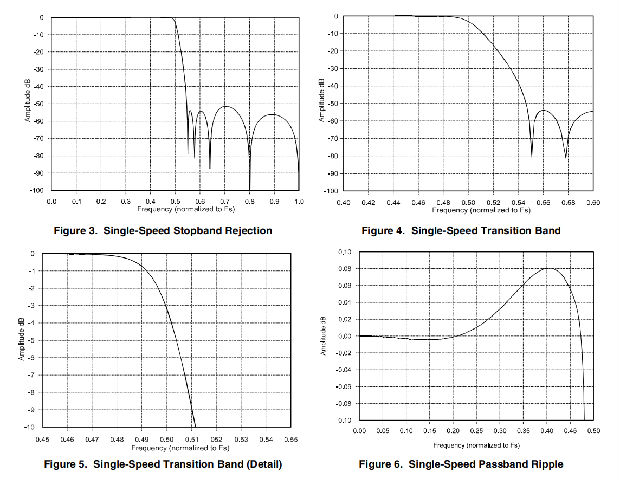

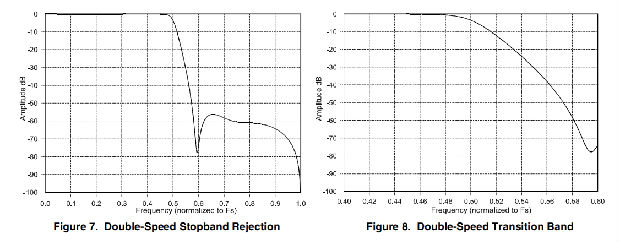

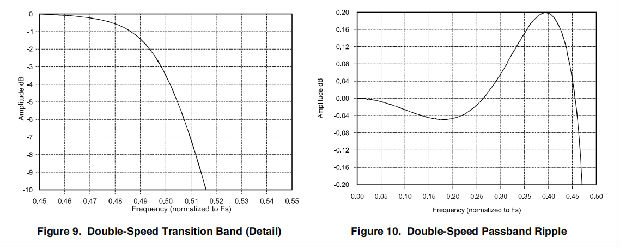

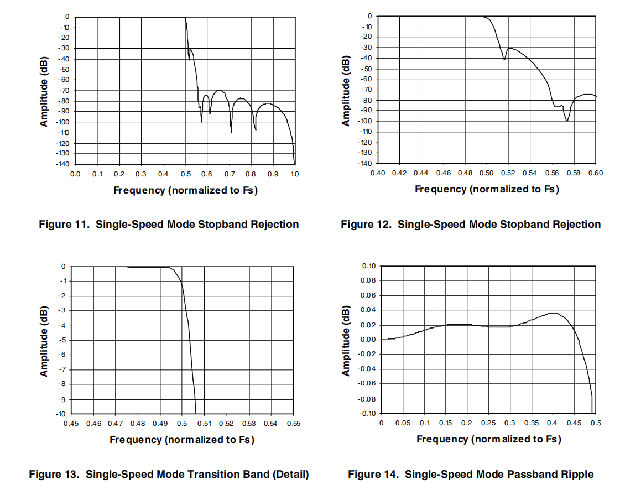

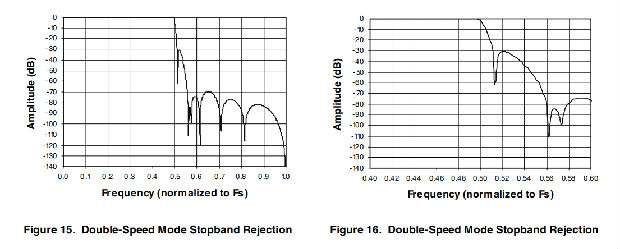

DAC滤波器响应

滤波器特性和响应图的X轴已经被标准化为输入采样率(Fs),并且可以通过将给定特性乘以Fs来参考期望的采样率。

注:1、对于单速模式,测量带宽为0.5465fs至3fs。

2、对于双速模式,测量带宽为0.577fs到1.4fs。

3、仅在单速模式下可取消强调。

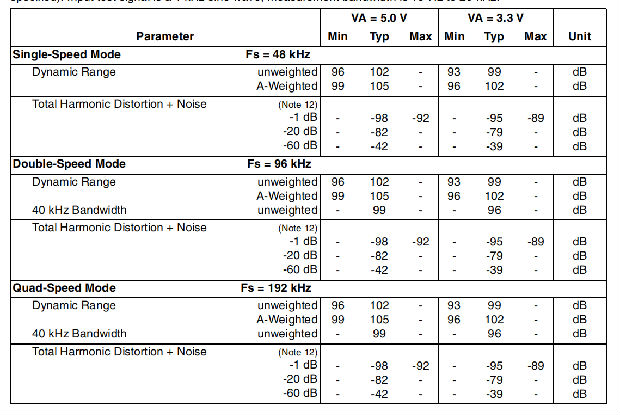

ADC模拟特性(CS42406-CQZ)

测试条件(除非另有规定):输入测试信号为1kHz正弦波;测量带宽为10Hz至20kHz。

注:参考典型的满标度输入电压。

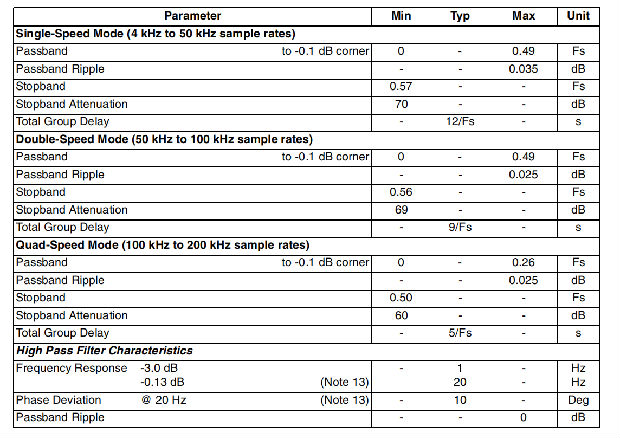

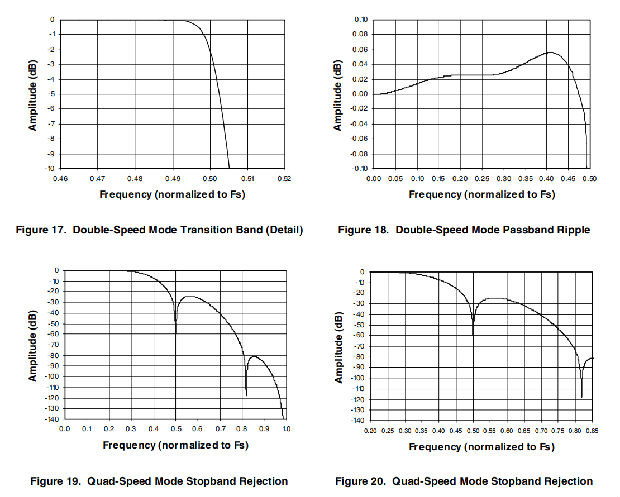

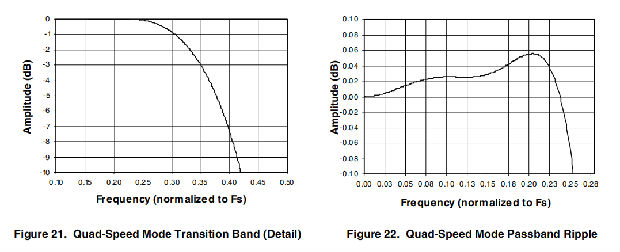

ADC数字滤波器响应

滤波器特性和响应图的X轴已被标准化为采样率(Fs),并且可以通过将给定特性乘以Fs来参考期望的采样率.

注:所示响应为Fs等于48 kHz。

典型接线图

应用

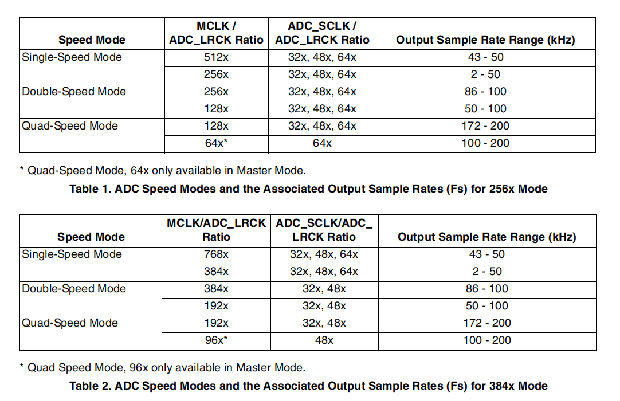

单速、双速和四速模式

ADC串行端口

CS42406内部的ADC可以支持从2 kHz到200 kHz的输出采样率,基本MCLK/ADC校验比为256x或384x。正确的速度模式可以由所需的输出采样率和外部MCLK/ADC校验比确定,如表1和表2所示。

DAC串行端口

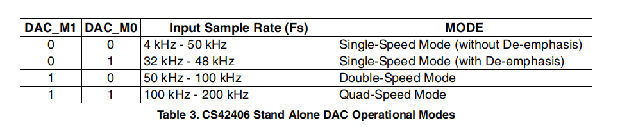

2a独立模式

当处于独立模式时,CS42406内部的DAC以DAC_Mx管脚确定的四种工作模式之一工作。不支持每个模式的采样率超出指定范围。参见表3。

2b控制端口模式

DAC在由控制端口模式中的FM位确定的三种工作模式中的一种下工作。不支持每个模式的采样率超出指定范围。

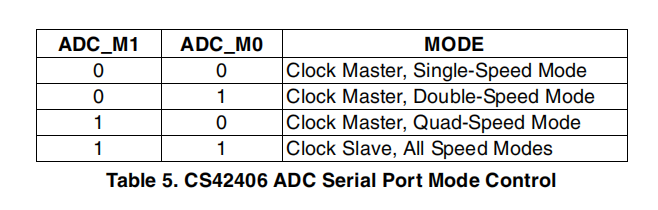

作为时钟主从机的ADC串行端口操作

CS42406 ADC串行端口支持作为时钟主机或从机的操作。作为时钟主机,ADC_LRCK和ADC_SCLK管脚与芯片上同步生成的左/右时钟和串行时钟一起输出。作为时钟从机,ADC_LRCK和ADC_SCLK管脚是输入,需要外部生成左/右时钟和串行时钟。如表5所示,通过ADC Mx引脚选择主时钟或从时钟。

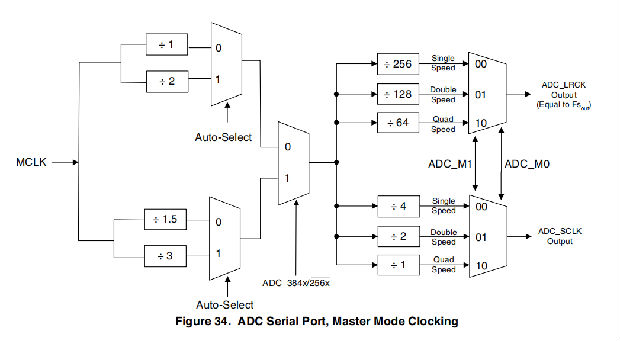

作为时钟主机的操作

作为时钟主机,ADC_LRCK和ADC_SCLK作为输出。左/右和串行时钟从主时钟内部派生,左/右时钟等于Fs,串行时钟等于64x Fs,如图34所示。

作为时钟从机的操作

ADC_LRCK和ADC_SCLK以时钟从模式作为输入。建议左/右时钟从主时钟同步派生,且必须等于Fs。还建议串行时钟从主时钟同步派生,并等于64x Fs,以最大限度地提高系统性能。有关支持的SCLK比率,请参阅表1和表2。

CS42406 ADC串行端口的一个独特功能是在作为时钟从机运行时自动选择单、双或四速模式。自动模式选择功能支持2至200 kHz的所有标准音频采样率。但是,在使用快速MCLK时不支持非标准音频采样率的范围(单速、双速和四速模式分别为512x/768x、256x/384x、128x/192x)。支持的采样率范围见表1和表2。

数字接口格式

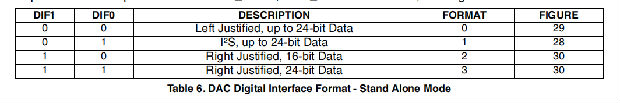

DAC串行端口

CS42406 DAC串行端口将在独立模式下(如表6所示)接受4种数字接口格式中的1种音频样本,在控制端口模式下(如第41页表7所示)接受6种格式中的1种。

独立模式

DAC串行端口的所需格式是通过DIF1和DIF0引脚选择的。有关DAC_LRCK、DAC_SCLK和SDINx之间所需关系的说明,请参见图28-30。

控制端口模式

通过模式控制2寄存器中的DIF2、DIF1和DIF0位选择DAC串行端口的所需格式。有关DAC_LRCK、DAC_SCLK和SDINx之间所需关系的说明,请参见图28-30。

ADC串行端口

CS42406 ADC串行端口支持I?S和左对齐的串行音频格式。启动时,CS42406将检测SDOUT上的逻辑电平。需要一个到VLS的10 kΩ上拉电阻器来选择I?S格式,需要一个到GND的10 kΩ下拉电阻器来选择左对齐格式。有关ADC_LRCK、ADC_SCLK和SDOUT之间所需关系的说明,请参见图28和29。

去重控制

CS42406包括片内数字去重。图35显示了Fs等于44.1khz时的去强调曲线。去强调曲线的频率响应将随采样率Fs的变化成比例。

曲线注意:仅在单速模式下可取消强调。

独立模式

工作模式管脚DAC_M1和DAC_M0选择44.1khz去加重滤波器。

控制端口模式

模式控制位选择32、44.1或48 kHz去强调滤波器。请参阅第6.1.3节了解所需的去重控制。

模拟连接

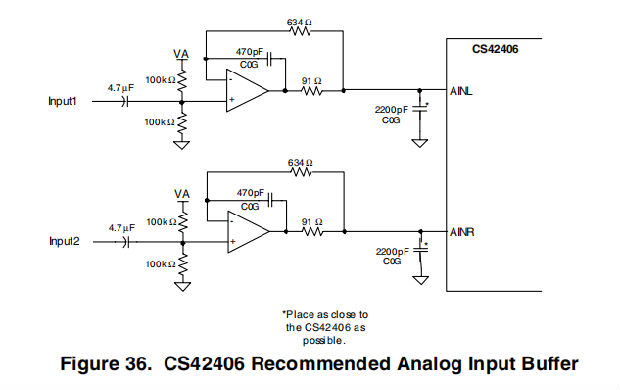

模拟调制器以6.144mhz采样输入。数字滤波器将拒绝滤波器阻带内的信号。然而,对于输入采样频率(n×6.144mhz)的倍数的输入信号没有抑制,其中n=0,1,2。。。参考图36,其中显示了建议的滤波器,该滤波器除了为调制器提供最佳源阻抗外,还将衰减6.144 MHz下的任何噪声能量。必须避免使用具有较大电压系数的电容器(如通用陶瓷),因为这些电容器会降低信号线性度。

参考引脚上的电容器尺寸(FILT+)

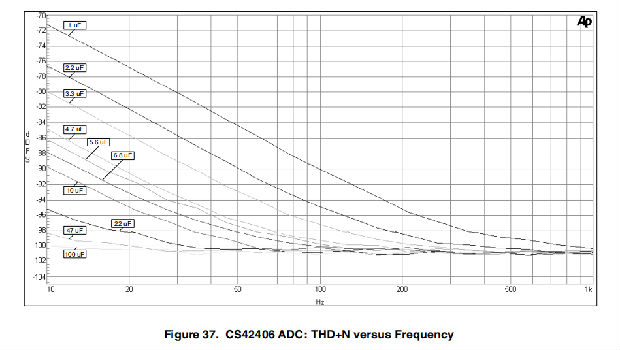

CS42406需要内部参考电压引脚ADC_FILT+上的外部电容。去耦电容器的大小将影响低频失真性能,如图37所示,使用较大的电容器值来优化低频失真性能。

建议的通电顺序

独立模式

1)、将DAC_RST和ADC_PDN保持在低位,直到电源和配置引脚稳定,并且主时钟和左/右时钟锁定到适当的频率。在此状态下,控制端口将重置为其默认设置。

2)、使DAC RST和ADC PDN升高。CS42406 DAC将保持低功率状态,DAC VQ低,并在单速模式下大约512个DAC LRCK周期(双速模式下1024个DAC LRCK周期,四速模式下2048个DAC LRCK周期)后启动独立的加电序列。CS42406 ADC将在ADC PDN变高后立即开始通电序列。

控制端口模式

1)、将DAC_RST和ADC_PDN保持在低位,直到电源稳定,并且主时钟和左/右时钟锁定到适当的频率。在此状态下,控制端口将重置为其默认设置。

2)、使DAC RST和ADC PDN升高。CS42406 DAC将保持低功耗状态,DAC_VQ低。

3)、加载所需的寄存器设置,同时保持PDN位设置为1。

4)、将PDN位设置为0。这将启动DAC的通电序列,当POPG位设置为0时,该序列将持续大约50微秒。如果将POPG位设置为1,请参阅第4.7节以获取有关通电计时的完整说明。

Popguard瞬态控制®

CS42406使用了一种技术来最小化通电和断电期间输出瞬态的影响。该技术与外部直流阻塞电容器串联使用时,可将通常由单端单电源转换器产生的音频瞬变降至最低。当DAC RST引脚或PDN位被启用/禁用时,它在CS42406内部被激活,除了选择合适的直流阻塞电容器外,不需要其他外部控制。

通电

当设备最初通电时,音频输出(AOUTAx和AOUTBx)被固定到GND。在大约1000个DAC_LRCK周期的延迟之后,每个输出开始向静态电压倾斜。大约10000 DAC_LRCK周期后,输出达到DAC_VQ,音频输出开始。这种电压渐变允许外部直流阻塞电容器充电到静态电压的时间,从而使通电瞬态最小化。

断电

为了防止断电时出现瞬变,CS42406必须首先进入断电状态。发生这种情况时,音频输出停止,内部输出缓冲区与AOUTAx和AOUTBx断开连接。取而代之的是软启动电流接收器,它允许直流阻塞电容器缓慢放电。一旦电荷消散,设备的电源可能会关闭,系统准备好下次通电。

放电时间

为防止下一次通电时出现音频瞬变,直流阻断电容器必须在接通电源或退出掉电状态前完全放电。如果没有发生完全放电,当音频输出最初被钳制到GND时,将发生瞬态。设备必须保持断电状态的时间与直流闭锁电容值和输出负载有关。例如,对于3.3μF电容器,最小断电时间约为0.4秒。

静音控制

在通电初始化、复位、静音(见第6.1.1节和第6.4.1节)或MCLK与DAC LRCK比率不正确时,静音控制引脚变高。这些引脚用作外部静音电路的控制,以防止任何单端单电源系统中可能发生的咔嗒声和砰嗒声。

使用静音控制功能不是强制性的,但建议在需要绝对最小的外部点击和弹出的设计。此外,使用静音控制功能可以使系统设计人员实现仅受外部静音电路限制的空闲信道噪声/信噪比。有关建议的静音电路,请参阅CDB42406数据表。

接地和供电安排

与任何高分辨率转换器一样,如果要实现其潜在性能,CS42406需要仔细注意电源和接地安排。图33显示了推荐的电源配置,VA、VD、VLS和VLC连接到清洁电源。如果接地平面分为数字接地和模拟接地,则CS42406的接地引脚应连接到模拟接地平面。

所有信号,尤其是时钟,应远离FILT+和VQ引脚,以避免不必要的耦合到调制器中。CDB42406评估委员会展示了最佳布局和电源安排。

电容器布置

去耦电容器应尽可能靠近CS42406,低值陶瓷电容器最接近。为了进一步降低阻抗,这些电容器应与转换器位于同一层。如果需要,所有电源引脚可以连接到同一个电源,但去耦电容器仍应放置在每个电源引脚上,并参考模拟接地。由于两个VD管脚(管脚7和9)很接近,一组去耦电容器就足以提供数字电源。请参考图33。

控制端口接口

控制端口用于加载所有内部寄存器设置。控制端口的操作可能与音频采样率完全异步。但是,为了避免潜在的干扰问题,如果不需要操作,控制端口引脚应保持静止。

控制端口以两种模式之一工作:I2C或SPI。

注:在所有I2C通信过程中,必须使用MCLK。

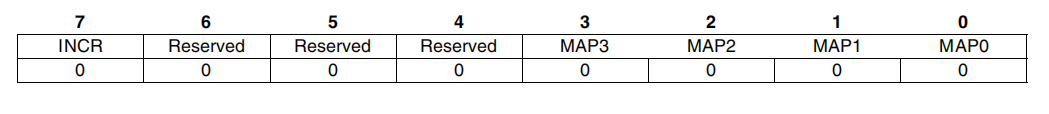

内存地址指针(MAP)

在写操作期间,映射字节位于控制端口寄存器字节之前,并且不再可用直到启动条件之后。在读取操作期间,ACK之后发送的字节将包含MAP所指的寄存器的数据(有关写入/读取的详细信息,请参阅第4.10.2a节和第4.10.2b节)。

增量(自动地图增量)

CS42406具有由映射的增量位(MSB)启用的映射自动增量功能。如果INCR设置为0,MAP将在连续的I?C写入或读取以及SPI写入时保持不变。如果INCR设置为1,MAP将在写入每个字节后自动递增,从而允许对连续寄存器进行块读取或写入。

默认值为“0”

0 -无效

1 -启用

MAP0-3(内存地址指针)

默认设置为“0000”

I2C模式

在I2C模式下,数据通过串行控制端口时钟,SCL。没有CS pin。引脚AD0允许用户更改芯片地址(001000[AD0][R/W]),并应根据需要绑定到VLC或GND,然后再为设备通电。如果设备在通电后在AD0/CS引脚上检测到高低转换,则将选择SPI模式。

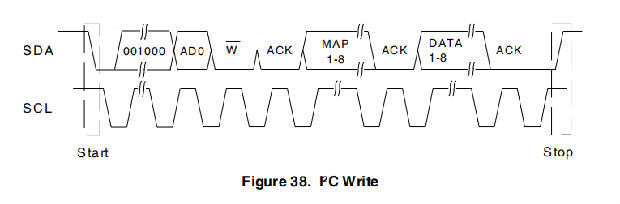

I2C写入

要写入设备,请遵循以下步骤,同时遵循第27页“交换规范-控制端口接口”中所述的控制端口定时。

1)、启动I2C总线的启动条件,后跟地址字节。上面的6位必须是001000。第七位必须与AD0引脚的设置相匹配,第八位必须为0。第八地址字节的位是R/W位。

2)、等待部件的确认(ACK),然后写入内存地址指针MAP。这个字节指向要写入的寄存器。

3)、等待部件的确认(ACK),然后将所需数据写入映射指向的寄存器。

4)、如果INCR位(见第4.10.1a节)设置为1,重复上一步,直到写入所有所需的寄存器,然后启动总线的停止条件。

5)、如果增量位设置为0,并且需要进一步向其他寄存器写入I?C,则需要重复步骤1中详述的过程。如果不需要进一步写入其他寄存器,则启动总线的停止条件。

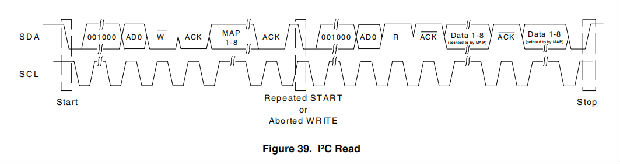

仪表板读数

要读取设备,请遵循以下步骤,同时遵守控制端口交换规范。在此操作期间,首先需要写入设备,通过映射指定适当的寄存器。

1)、在写入MAP(见第4.10.1节)后,启动I?C总线的重复启动条件,然后是地址字节。上面的6位必须是001000。第七位必须与AD0引脚的设置相匹配,第八位必须为1。地址字节的第八位是R/W位。

2)、通过不发出应答来表示地址字节的结束。然后,设备将发送由映射指向的寄存器的内容。映射将包含写入映射的最后一个寄存器的地址。

3)、如果INCR位设置为1,设备将继续发送连续寄存器的内容。继续提供时钟,但不要对设备超时的字节发出ACK。读取所有所需寄存器后,启动总线的停止条件。

4)、如果增量位设置为0,并且需要从其他寄存器进一步读取I?C,则有必要重复步骤1中详述的过程。如果不需要从其他寄存器进一步读取,则启动总线的停止条件。

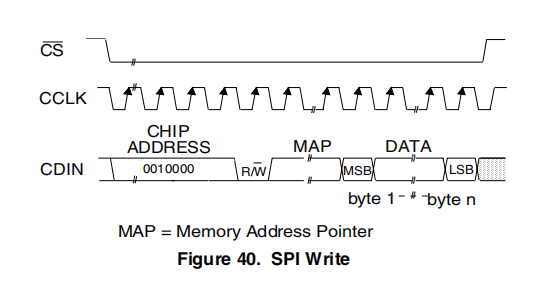

SPI模式

在SPI模式下,数据通过串行控制端口时钟CCLK(时钟与数据的关系见图40)进入串行控制数据线CDIN。没有AD0引脚。Pin CS是芯片选择信号,用于控制SPI对控制端口的写入。当设备检测到AD0/CS引脚通电后,将选择SPI模式。所有信号都是输入,数据在CCLK的上升沿上计时。

SPI写入

要写入设备,请遵循以下过程,同时遵守控制端口交换规范。

1)、降低CS。

2)、CDIN pin上的地址字节必须是00100000。

3)、写入内存地址指针MAP。这个字节指向要写入的寄存器。

4)、将所需数据写入映射指向的寄存器。

5)、如果增量位(见第4.10.1a节)设置为1,则重复上一步,直到所有所需的寄存器写了,然后把CS调高。

6)、如果INCR位设置为0,并且需要进一步向其他寄存器写入SPI,则需要CS高,重复步骤1中的步骤。如果不需要进一步写入其他寄存器,请将CS调高。

参数定义

动态范围

信号的均方根值与指定带宽上所有其他谱分量的均方根和的比值。动态范围是用-60dbfs信号在指定带宽上测量的信噪比。将60分贝加到测量结果中,以将测量结果参考满标度。该技术确保失真分量低于噪声级,且不影响测量。这种测量技术已经被音频工程学会接受,AES17-1991和日本电子工业协会,EIAJ CP-307。以分贝表示。

总谐波失真+噪声

信号的均方根值与指定带宽(通常为10赫兹到20千赫)内所有其他频谱分量的均方根和的比值,包括失真分量。以分贝表示。根据AES17-1991附录A中的建议,在-1和-20 dBFS下测量。

频率响应

相对于1khz的振幅响应,振幅响应变化从10hz到20khz的测量。分贝单位。

通道间隔离

左右声道间串扰的一种测量方法。在转换器输出端对每个通道进行测量,没有信号传输到被测输入端,满标度信号传输到另一个通道。分贝单位。

通道间增益失配

左右声道的增益差。分贝单位。

增益误差

与满标度数字输出的标称满标度模拟输入的偏差。

增益漂移

增益值随温度的变化。单位为ppm/℃。

偏移误差

中尺度跃迁(111…111到000…000)与理想的偏差。单位为毫伏。

包装尺寸