DIT4192点击型号即可查看芯片规格书

特征

●符合AES-3、IEC-60958和EIAJ CP1201接口标准

●支持高达192kHz的采样率

●支持单模式操作

●片上差分线路驱动器

●灵活的音频串行接口:

-主模式或从模式操作

-支持I2S、左对齐和右对齐数据格式

●通过串行控制接口的软件模式:

-通道状态数据的块大小缓冲区

-块大小写和读操作的自动增量模式

●硬件模式允许无微控制器操作

●专业模式CRC码生成

●主时钟速率:128fS、256fS、384fS或512fS

●+5V芯电源(VDD)

●2.7V至VDD逻辑I/O电源(VIO)

●包装:TSSOP-28

应用

●数字调音台

●数字话筒

●数字音频工作站

●广播演播室设备

●效果处理程序

●环绕声解码器和编码器

●A/V接收器

●DVD、CD、DAT和MD播放器

●音频测试设备

说明

DIT4192是一款数字音频发射机,专为专业和消费类音频应用而设计。支持高达192kHz的传输数据速率。DIT4192支持软件和硬件操作,这使得它适合有或没有微控制器的应用。提供了一个灵活的串行音频接口,支持标准音频数据格式,易于与音频DSP串行端口接口。

一般说明

DIT4192是一个完整的数字音频发射器,适用于专业和消费音频应用。支持高达192kHz的采样率。DIT4192符合AES-3、IEC-60958和EIAJ CP1201接口标准的要求。

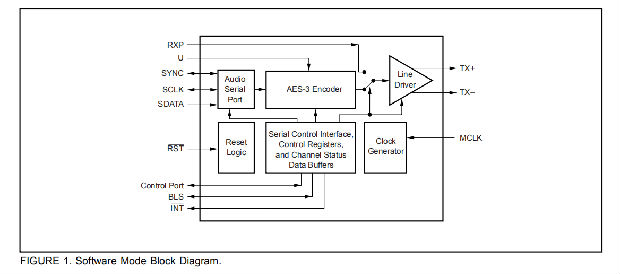

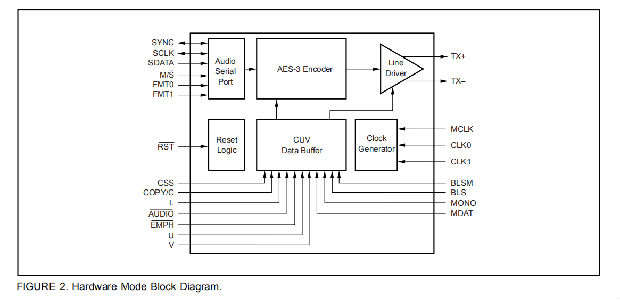

图1和图2显示了在软件和硬件控制模式下使用DIT4192的框图。模式输入(引脚28)确定用于配置DIT4192内部功能的控制模型。在软件模式下,串行控制端口用于写入和读取片上控制寄存器和状态缓冲器。在硬件模式下,为配置和状态输入提供专用控制引脚。

DIT4192包括音频串行端口,用于与标准数字音频源接口,例如模数转换器、数字信号处理器(DSP)和音频解码器。支持左对齐、右对齐和I2S数据格式。

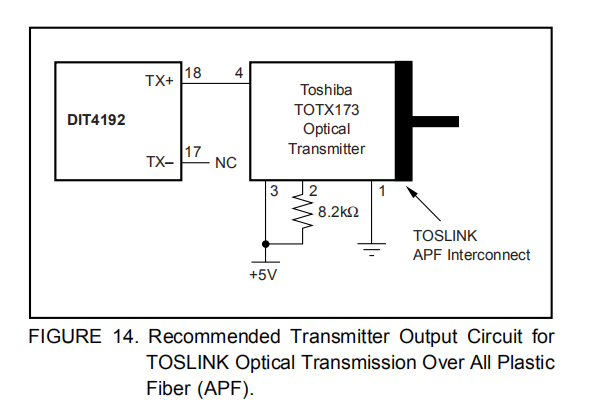

AES-3编码器创建一个多路复用比特流,包含音频、状态和用户数据。多路数据格式见图3。然后对数据进行双相位标记编码并输出到差分线路驱动器。线路驱动器输出连接到传输介质,无论是电缆还是光纤。在双绞线或同轴电缆的情况下,通常使用变压器将驱动器输出耦合到传输线。这提供了隔离和改进的共模抑制。对于光传输,TX+(引脚18)驱动器输出连接到光发射机模块。有关输出驱动电路配置的详细信息,请参阅本数据表的应用信息部分。

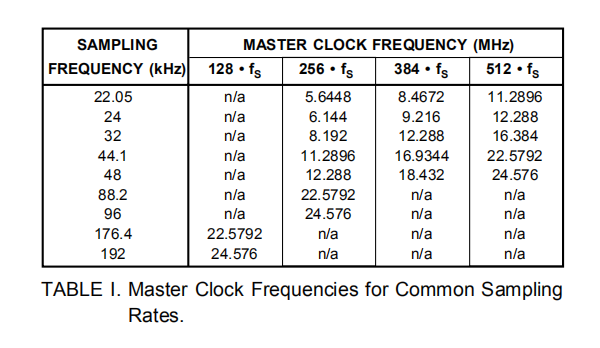

主时钟

DIT4192需要主时钟才能工作。该时钟必须在MCLK输入端(引脚6)提供。可提供给MCLK的最大主时钟频率为25MHz。表1显示了公共输入采样频率的主时钟速率。

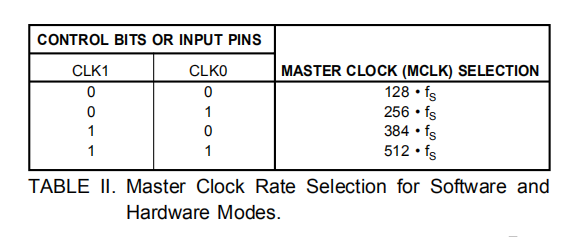

对于软件模式,使用控制寄存器02H中的CLK0和CLK1位编程主时钟频率选择。对于硬件模式,使用CLK0(引脚5)和CLK1(引脚4)输入来选择主时钟频率。表II显示了可用的MCLK频率选择。

复位和断电操作

DIT4192包括复位输入RST(引脚15),用于强制复位序列。当DIT4192首次通电时,用户必须断言RST低才能启动重置序列。RST输入必须低至少500ns。然后,将RST输入强制为高,以启用正常操作。对于软件模式,复位顺序将强制所有内部寄存器为其默认设置。此外,复位序列将在软件模式下强制所有信道状态位为0。

当RST输入低时,变送器输出TX–(引脚17)和TX+(引脚18)被强制接地。

设置RST高时,TX-和TX+输出将保持低,直到在引脚12处检测到同步时钟的上升沿。一旦发生这种情况,TX-和TX+输出将激活,并由AES-3编码器的输出驱动。

在软件模式下,DIT4192还包括位于控制寄存器02H中的软件复位和断电位软件重置位RST和软件断电位PDN都处于高激活状态。

音频串行端口

音频串行端口是一个3线接口,用于将DIT4192连接到音频源,如a/D转换器或DSP。端口支持高达192kHz的采样频率。端口信号包括SDATA(引脚13)、SYNC(引脚12)和SCLK(引脚11)。SDATA pin是端口的串行数据输入。SCLK引脚可以是输入或输出,用于将串行数据时钟输入端口。同步管脚可以是输入或输出,并为端口提供帧同步时钟。同步管脚还用作硬件模式下信道状态、用户和有效性数据输入以及软件模式下用户数据输入的数据锁存时钟。

从模式或主模式操作

音频串行端口支持从模式和主模式操作。在从属模式下,SYNC和SCLK都配置为输入。音频源设备必须在从属模式下同时生成同步时钟和SCLK时钟。在主模式下,SYNC和SCLK都配置为输出。音频串行端口在主模式下生成同步时钟和SCLK时钟,两者都来自主时钟(MCLK)输入。

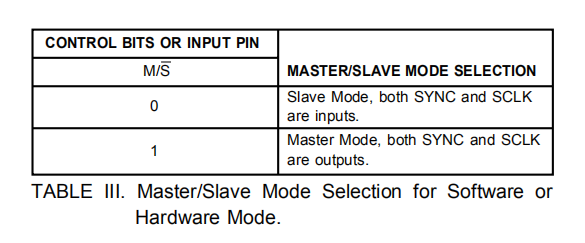

在软件模式下,主/从模式选择根据-使用控制寄存器03H中的M/S位形成(默认为从模式)。在硬件模式下,M/S输入(引脚14)用于选择音频串行端口模式。如表三所示。

同步和SCLK频率

同步时钟速率与采样频率(fS)相同。这对从模式和主模式都适用。DIT4192支持高达192kHz的同步频率。

从模式下的SCLK频率必须为SDATA输入的每个数据位提供至少一个时钟周期。最大SCLK频率为128•fS,如果fS=192kHz,则为24.576MHz。主模式下的SCLK频率由DIT4192自身设置。对于软件模式操作,可使用控制寄存器03HEX中的SCLKR位将SCLK速率编程为64•fS或128•fS。在硬件模式下,主模式的SCLK频率固定在64•fS。

音频数据格式

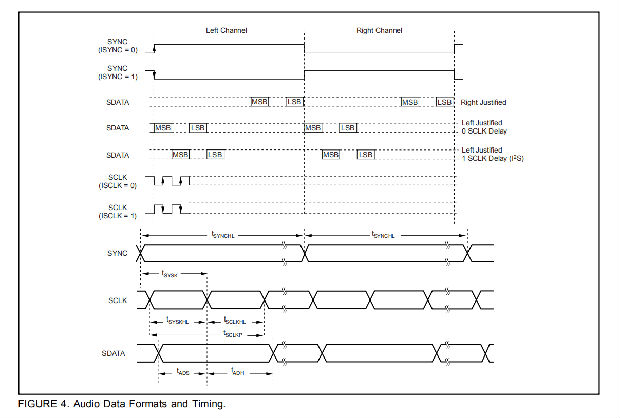

DIT4192支持标准音频数据格式,包括飞利浦I2S、左对齐和右对齐数据。

软件模式提供了最灵活的格式选择,而硬件模式支持有限的软件模式格式子集。在s data输入端的线性PCM音频数据通常以二进制2的补码MSB first格式呈现。可根据使用中的编码方案的要求提供编码或非音频数据。图4显示了音频串行端口使用的常见数据格式。

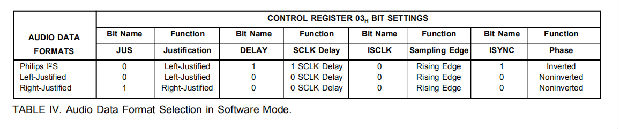

对于软件模式,控制寄存器03H用于设置音频数据格式选择。可以使用WLEN0和WLEN1位将数据字长度设置为16、18、20或24位。可以使用该寄存器编程多个格式参数,包括SCLK采样边缘、从帧开始的数据延迟和同步极性。表四显示了三种标准音频格式的寄存器位设置示例。SCLK采样边缘和同步极性可能因系统实现的不同而不同。有关输出数据格式的详细信息,请参阅音频源设备数据表或技术参考。

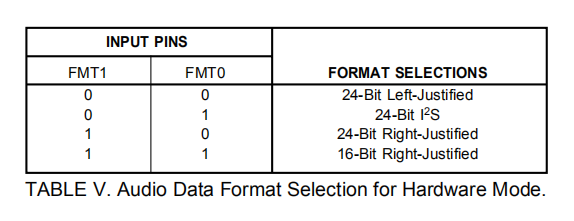

对于硬件模式,使用FMT0(引脚9)和FMT1(引脚10)输入来选择四种音频数据格式之一。有关可用的格式选择,请参阅表V。

AES-3编码器操作

AES-3编码器执行音频、信道状态、用户和有效性数据的多路复用。它还执行多路复用数据流的双相标记编码。本节描述如何将信道状态、用户和有效性数据输入编码器功能。

块启动输入/输出

块开始用于指示信道状态数据块的开始,该数据块以AES-3数据流的帧0开始。对于DIT4192,块启动信号BLS(引脚25)可以是输入或输出。在软件模式下,使用控制寄存器01H(默认为输入)中的BLSM位设置BLS的方向。在硬件模式下,BLS的方向由BLSM输入(引脚24)设置。如果BLSM=0,则BLS引脚是一个输入。如果BLSM=1,则BLS管脚为输出。

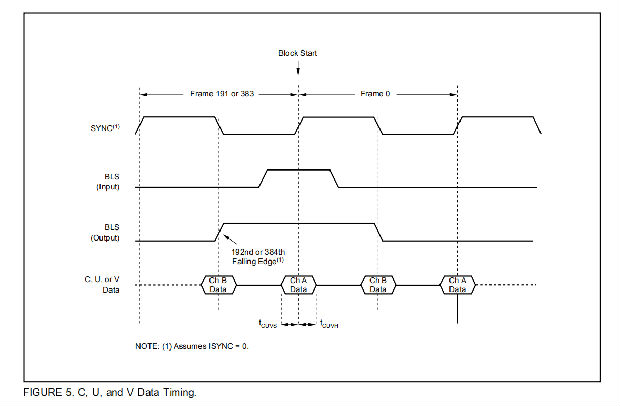

对于软件模式操作,块启动信号与音频串行端口帧同步时钟同步(引脚12)。当BLS被配置为输入管脚时,当控制寄存器03H中的ISYNC位设置为0时,它在SYNC的上升沿上采样。否则,将在ISYNC位设置为1时同步的下降沿。如果采样时BLS为高,则指示块启动条件。当BLS被配置为输出并且ISYNC位被设置为0时,BLS将在立体声模式下的每192nd同步下降沿或单声道模式下的每384同步下降沿处升高。然后BLS将在下面的下降沿上下降。如果ISYNC位设置为1,那么BLS将在SYNC的上升沿上转换。

硬件模式操作与软件模式操作类似,只是音频串行端口的数据格式数量有限。对于左对齐和右对齐格式,BLS的行为与ISYNC=0的软件模式相同。对于I2S数据格式,BLS的行为与ISYNC=1的软件模式一样。

通道状态数据输入

通道状态数据输入由正在使用的控制模式决定。在软件模式下,通过串行控制端口访问信道状态数据缓冲区。缓冲区操作在本数据表标题为信道状态缓冲区操作(仅限软件模式)的章节中有详细说明。在硬件模式下,通道状态数据输入由两种用户可选择的方法之一完成。

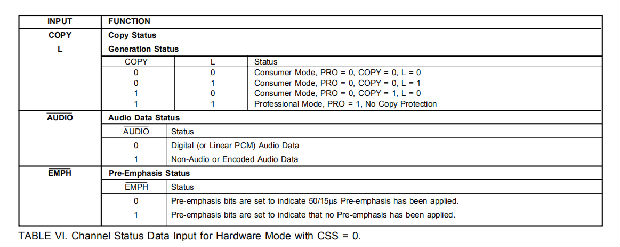

CSS输入

在硬件模式下,CSS输入(pin 1)的状态决定了专用信道状态输入的功能。当CSS=0时,拷贝(pin 2)、L(pin 3)、音频(pin 22),EMPH(引脚23)输入用于设置相关信道状态数据位。复制和L输入用于设置用户操作的复制保护,或指示发射机在没有复制保护的专业模式下运行。音频输入用于指示所发送的数据是PCM音频数据还是非音频数据。EMPH输入用于指示是否使用50/15微秒标准预先强调了PCM音频数据。这些专用信道状态输入的可用选项见表六。

当CSS=1时,信道状态数据以串行方式在C输入端(pin 2)输入。数据在同步输入(引脚12)的上升和下降沿上计时。所有通道状态数据位都可以在这种模式下写入,与以前的CSS=0的硬件模式相比具有更大的灵活性。C输入时序图见图5。

用户和有效性数据输入

AES-3数据流中的用户数据位允许以方便的方式将用户定义的或特定于应用程序的数据传输到包含AES-3接收器的另一设备。U输入(引脚27)用于软件和硬件模式,以串行方式输入用户数据。图5显示了U输入时序图。

有效性数据用于指示样本是无错误的音频数据,或者样本有缺陷且不适合进一步处理。在软件模式下,利用控制寄存器01H中的VAL位来写入有效性数据。在硬件模式下,V输入(引脚26)用于以串行方式输入有效性数据。有关硬件模式的V输入定时,请参阅图5。

当VAL或V=0时,这表示音频数据有效并且适合进一步处理。当VAL或V=1时,则音频样本有缺陷,不应使用。

线路驱动器输出

DIT4192包括一个平衡线路驱动器。线路驱动器输出为TX–(引脚17)和TX+(引脚18)。在软件模式下,线路驱动程序输入来自onchip AES-3编码器的输出,或者来自RXP处的外部AES-3编码源输入(pin 9)。使用控制寄存器01H中的旁路位选择输入源(默认为片上AES-3编码器)。在硬件模式下,线路驱动源始终是片上AES-3编码器。

线路驱动器的输出在正常运行时将遵循AES-3编码的数据源。在硬件或软件重置期间,或当设备处于断电模式时,线路驱动器输出将强制接地。通过在控制寄存器01H中将TXOFF位设置为1,也可以在软件模式下随时强制输出接地。

控制端口操作(仅限软件模式)

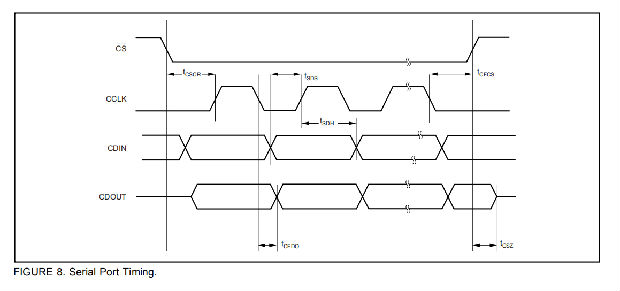

对于软件模式操作,DIT4192包括串行控制端口,用于写入和读取控制寄存器和信道状态数据缓冲器。端口信号包括CS(引脚5)、CDIN(引脚4)、CDOUT(引脚2)和CCLK(引脚3)。

CS是主动低芯片选择。为了写入或读取控制寄存器和信道状态数据缓冲器,必须将该信号驱动为低电平。

CDIN是串行数据输入,CDOUT是串行数据输出。CDOUT管脚是三态输出,当不执行读取操作或CS=1时设置为高阻抗状态。

CCLK是串行控制接口的数据时钟。数据在CCLK上升沿的CDIN处打卡,而数据在CCLK下降沿的CDOUT处打卡。对于CDIN和CDOUT,首先对MSB进行数据计时。

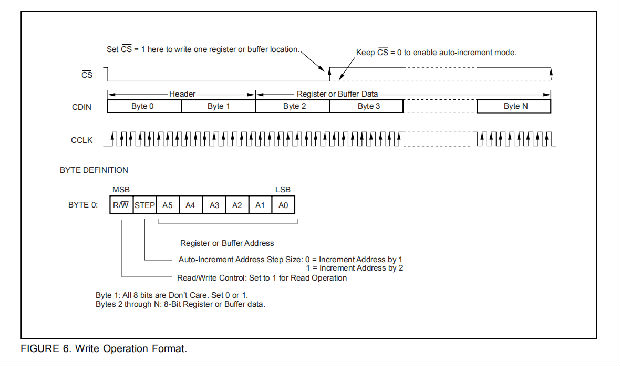

写操作

图6说明了控制端口的写操作。您可以一次写入一个寄存器或缓冲区地址,或者使用控制端口内置的自动增量功能执行块写入。寄存器或缓冲区数据前面有一个16位头,第一个字节用于配置控制端口操作和设置起始寄存器或缓冲区地址。报头的第二个字节由“不关心”位组成,可以设置为0或1,而不影响端口操作。

报头的第一个字节包含两个控制位,R/W和STEP,后跟一个6位地址。对于写操作,R/W=0。步进位决定自动递增操作的地址步进大小。当STEP=0时,地址递增1。当STEP=1时,地址递增2。按顺序写入多个控制寄存器或同时写入这两个寄存器时,递增1很有用按顺序显示左、右通道状态数据。当只按顺序写入一个状态数据通道时,递增2非常有用。

第三个字节包含报头第一个字节指向的寄存器或缓冲区地址的8位数据。要写入单个地址位置,反恐精英在第三个字节的最低有效位进入端口后被调高。对于自动增量模式,反恐精英保持低位以写入连续寄存器或缓冲区地址。

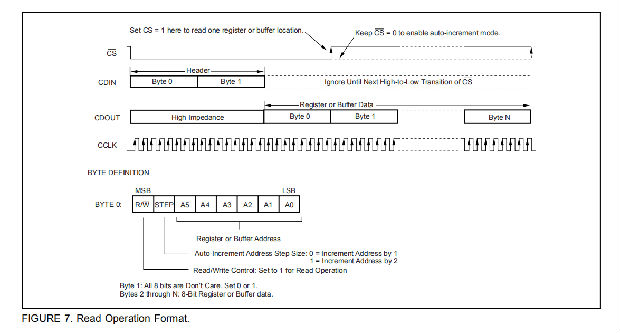

读取操作

图7显示了控制端口的读取操作。您可以一次读取一个寄存器或缓冲区地址,或者使用控制端口内置的自动增量功能执行块读取。首先将16位头写入端口,第一个字节用于配置控制端口操作和设置起始寄存器或缓冲区地址。报头的第二个字节由“不关心”位组成,可以设置为0或1,而不影响端口操作。

报头的第一个字节包含两个控制位,R/W和STEP,后跟一个6位地址。对于读取操作,R/W=1。步进位决定自动递增操作的地址步进大小。当STEP=0时,地址递增1。当STEP=1时,地址递增2。按顺序读取多个控制寄存器时,或按顺序读取左右通道状态数据时,递增1非常有用。递增2对于按顺序读取一个通道的状态数据非常有用。

第一个输出数据字节在写入16位报头后立即出现。此字节包含报头第一个字节指向的寄存器或缓冲区地址的8位数据。要读取单个地址位置,在第一个数据字节的最低有效位从端口打卡后,CS将变高。对于自动递增模式,CS保持在低位以读取连续寄存器或缓冲区地址。

通道状态数据缓冲操作(仅限软件模式)

DIT4192包含两个通道状态数据缓冲区。这些被称为发射机接入(TA)缓冲器和用户接入(UA)缓冲器。每个缓冲区的长度为48字节,每个缓冲区包含通道A和B的24字节。每个通道的24字节对应于AES-3和IEC-60958规范中定义的通道状态块。通道A和B数据在缓冲器内交错,见表VII和VIII。

AES-3编码器内部访问TA缓冲器以获得多路复用到AES-3数据流中的信道状态数据。用户通过控制端口访问UA缓冲区,以便在需要时更新信道状态数据。从UA缓冲区到TA缓冲区的数据传输由DIT4192在内部管理,但是用户可以通过控制寄存器来启用或禁用它。

主时钟输入(MCLK)和帧同步时钟输入(SYNC)必须处于活动状态,以便在软件模式下更新信道状态缓冲区。当DIT4192最初通电时,设备默认为断电模式。当寄存器2中的PDN位设置为0以使设备通电时,PDN设置为0的时间与第一次访问信道状态缓冲区之间必须存在延迟。此延迟允许同步时钟将AES3编码器块与音频串行端口同步。建议寄存器2是在初始化序列中写入的最后一个控制寄存器,在尝试访问通道状态缓冲区之前,后面跟着一个延迟(10毫秒或更长)。

更新通道数据状态缓冲区

更新信道状态数据缓冲区涉及使用控制寄存器07H中的BTD位禁用和启用UA到TA缓冲区传输。图9显示了更新缓冲区的正确流程。

BTD位通常设置为0,这将启用UA到TA的缓冲区传输。为了更新信道状态数据,用户必须写入UA缓冲区。为了在更新UA缓冲区时避免UA到TA的数据传输,BTD位设置为1,这将禁用UA到TA的缓冲区传输。当BTD=1时,用户通过控制端口将新的信道状态数据写入UA缓冲区。一旦UA缓冲区更新完成,BTD位重置为0。在第184帧到第191帧中的一帧期间,将发生新的UA到TA缓冲器传输,以BTD位重置为0后发生的第一帧为准。一旦UA-to-TA缓冲区传输完成,只要未屏蔽,缓冲区传输中断(BTI)就会发生。

发射器将忽略任何访问UA的尝试

在UA到TA缓冲区传输期间缓冲。此外,BTD比特可以设置为1以停止UA到TA缓冲区的传输,如果需要的话,该传输可能正在进行中。

通道状态缓冲区映射

信道状态缓冲器按照AES-3和IEC-60958标准组织。专业模式下UA通道状态数据缓冲区内存映射见表七。表VIII显示了用户模式的UA信道状态数据缓冲器的存储器映射。

中断源(仅限软件模式)

DIT4192可以编程为最多生成三个预定义条件的中断。当发生有效中断时,中断输出INT(引脚22)被设置为低。然后读取中断状态寄存器04H,以确定中断源。状态寄存器位和INT输出引脚保持激活状态,直到状态寄存器被读取。一旦读取,状态位被清除,INT引脚被外部上拉电阻器拉高到VIO。

中断可以使用控制寄存器05H屏蔽。屏蔽时,与特定状态位相关联的中断机制被禁用。

通道状态缓冲传输中断

此中断发生在通道状态缓冲区传输完成时。缓冲区传输过程在本数据表的前一节中有详细说明。主机可使用此中断触发通道状态缓冲区更新后发生的事件。状态寄存器04H中的BTI位用于指示缓冲区传输的发生。与所有其他状态位一样,BTI位处于高激活状态,并在读取状态寄存器之前保持设置。

数据滑动和块启动中断

与只有一个功能的BTI中断不同,TSLIP中断可以设置为两种模式之一。这是使用控制寄存器05H中的BSSL位实现的。当BSSL=0时,TSLIP中断被设置为指示数据滑动条件。当BSSL=1时,TSLIP中断被设置为指示块启动条件。TSLIP位与所有其他状态位一样,处于高激活状态,并且在读取状态寄存器之前保持设置。

在主时钟MCLK(pin 6)与音频数据源不同步的情况下,可能会出现数据滑动情况。当BSSL=0时,每次丢弃或重复数据样本时,TSLIP位将设置为1。

当由DIT4192在内部生成块启动信号时,或者当在BLS输入端接收到外部块启动时(引脚25),发生块启动条件。

应用程序信息

本节提供与将DIT4192设计为目标应用程序相关的实用信息。根据需要提供电路原理图。

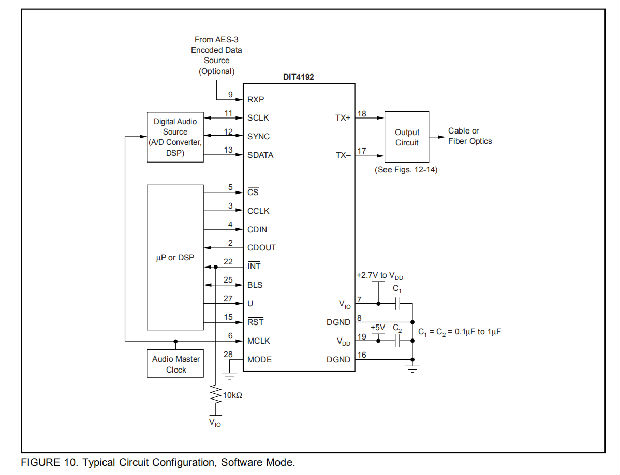

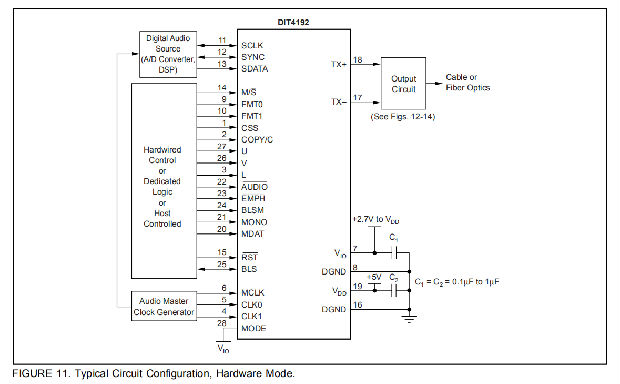

典型应用图

图10和11说明了在软件和硬件模式下使用DIT4192时的典型应用示意图。图10显示了一个典型的软件模式应用程序,其中微处理器或DSP接口用于通过串行控制端口与DIT4192通信。关于典型的硬件模式配置,请参见图11,其中控制管脚是硬接线的,或者由独立应用程序中的数字逻辑驱动。

电源旁路电容器的推荐部件值如图10和11所示。这些电容器应尽可能靠近DIT4192电源管脚。

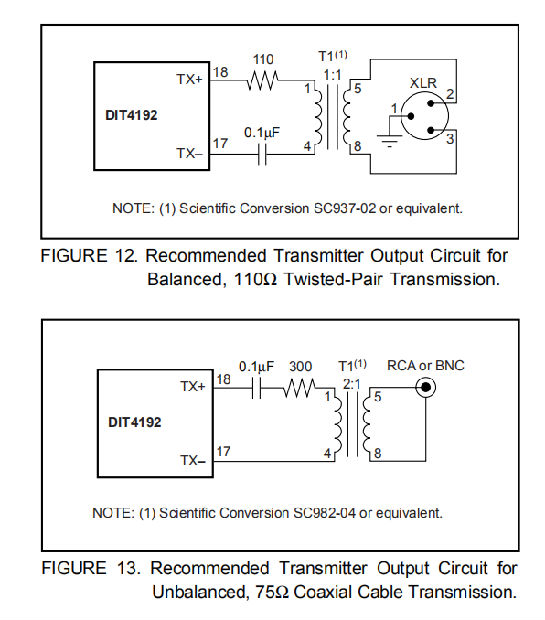

线路驱动器输出可以连接到目标应用中的电缆或光纤传输介质。图12和13显示了驱动平衡双绞线或非平衡同轴电缆的典型连接。这些连接中的任何一个将支持高达192kHz的速率。

图14说明了与光发送器模块的连接,该模块主要用于CD或DVD播放机等消费类应用。光发射机的数据速率限制在6Mb/s,因此它不支持192kHz的数据速率。光接口通常被保留用于低速率传输,例如44.1kHz或48kHz。

使用单声道模式的双线操作

为了支持传统系统的立体声192kHz传输,这些系统使用的AES-3接收机的最大工作频率为96kHz,有必要在所谓的双线配置中使用两个DIT4192发射机。在这种配置中,每个发射机只携带一个信道的数据。

双线操作要求每个DIT4192以单声道模式运行,这在软件和硬件控制模式中都受支持。在单声道模式下,DIT4192为信道a和信道B子帧发送单个信道的两个连续采样,有效地将采样率加倍。用于采样音频和通道状态数据的音频串行端口通道可在软件和硬件控制模式下选择。

在软件模式下,控制寄存器01H中的MONO、MDAT和MCSD位用于选择MONO模式,以及音频和信道状态数据的源信道。有关这些位的设置的详细信息,请参阅寄存器定义。

在硬件模式下,MONO(引脚21)和MDAT(引脚20)输入用于启用MONO模式,以及为音频和信道状态数据选择源信道。表九显示了MONO和MDAT选择的可用选项。图15说明了使用两个DIT4192发射机实现双信道操作的简单硬件模式配置。

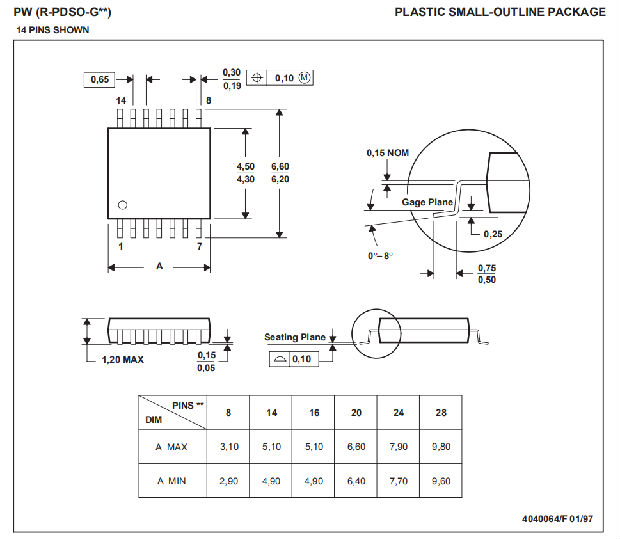

包装信息

注:

A、所有线性尺寸单位均为毫米。

B、 本图如有更改,恕不另行通知。

C、 阀体尺寸不包括不超过0.15的飞边或突出部分。

D、 属于JEDEC MO-153。