ADF7021点击型号即可查看芯片规格书

特征

低功耗窄带收发器;使用双VCO的频带;80兆赫至650兆赫;862兆赫至950兆赫;调制方案:2FSK、3FSK、4FSK、MSK;光谱整形;高斯和升余弦滤波;支持的数据速率;0.05 kbps至32.8 kbps;2.3 V至3.6 V电源;可编程输出功率:-16 dBm至+13 dBm,63步;自动PA坡道控制;接收机灵敏度;130 dBm,速度为100 bps,2FSK;122 dBm,1 kbps,2 fsk时;113 dBm,25 kbps,升余弦2FSK;正在申请专利,片上图像拒绝校准;片上VCO与分数N锁相环;片上、7位ADC和温度传感器;全自动频率控制回路(AFC);数字接收信号强度指示(RSSI);集成Tx/Rx开关;断电模式下0.1μA泄漏电流。

应用

低成本无线数据传输;远程控制/安全系统;无线测光;私人移动电台;无线医疗遥测服务(WMTS);无钥匙进入;家庭自动化;过程和建筑控制;传呼机。

一般说明

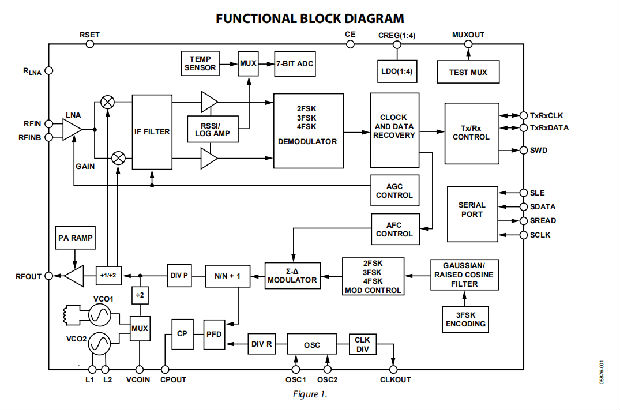

ADF7021是一款高性能、低功耗、高度集成的2FSK/3FSK/4FSK收发器。它设计用于在窄带、无许可证ISM波段和频率范围为80 MHz至650 MHz和862 MHz至950 MHz的许可波段中工作。该设备同时具有高斯和升余弦传输数据滤波选项,以提高窄带应用的频谱效率。它适用于针对欧洲ETSI EN 300 220、日本ARIB STD-T67、中国短程设备法规和北美FCC第15部分、第90部分和第95部分法规标准的电路应用。一个完整的收发器可以建立使用少量的外部离散组件,使ADF7021非常适合价格敏感和地区敏感的应用。

片上FSK调制和数据滤波选项的范围允许用户在选择调制方案时具有更大的灵活性,同时满足严格的频谱效率要求。ADF7021还支持在2FSK/3FSK/4FSK之间动态切换的协议,以最大化通信范围和数据吞吐量。

传输部分包含双压控振荡器(VCO)和输出分辨率小于1ppm的低噪声分数N锁相环。ADF7021有一个使用内部LC槽(431兆赫至475兆赫,862兆赫至950兆赫)的VCO和一个使用外部电感作为槽电路一部分(80兆赫至650兆赫)的VCO。双VCO设计允许双波段操作,用户可以在内部电感VCO支持的任何频率发射和/或接收,也可以在外部电感VCO支持的特定频带发射和/或接收。

频率捷变PLL允许ADF7021用于跳频扩频(FHSS)系统。两个VCO的工作频率都是基频的两倍,以减少杂散发射和频率牵引问题。

发射机输出功率可编程为63步,从-16 dBm到+13 dBm,并具有自动功率斜坡控制,以防止光谱飞溅并帮助满足监管标准。收发机射频频率和调制可使用简单的3线接口编程。该装置的工作电源范围为2.3伏至3.6伏,不使用时可断电。

接收机采用低中频结构(100khz),将功耗和外部组件降到最低计数,但避免了直流偏移和低频闪烁噪声。中频滤波器具有12.5 kHz、18.75 kHz和25 kHz的可编程带宽。ADF7021支持多种可编程特性,包括Rx线性度、灵敏度和中频带宽,允许用户根据应用情况权衡接收器灵敏度和选择性与电流消耗。

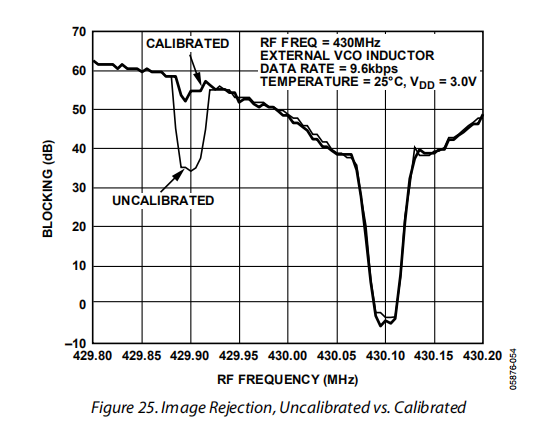

接收机还具有一个正在申请专利的自动频率控制(AFC)环路,该环路具有可编程的拉入范围,允许PLL跟踪输入信号中的频率误差。接收器使用不需要使用外部RF源的正在申请专利的IR校准方案实现56db的图像抑制性能。

片上ADC提供集成温度传感器、外部模拟输入、电池电压和RSSI信号的读回,这在某些应用中为ADC提供了节省。温度传感器在-40°C至+85°C的整个工作温度范围内精确到±10°C。可以通过在室温下执行1点校准并将结果存储在存储器中来提高此精度。

时序图

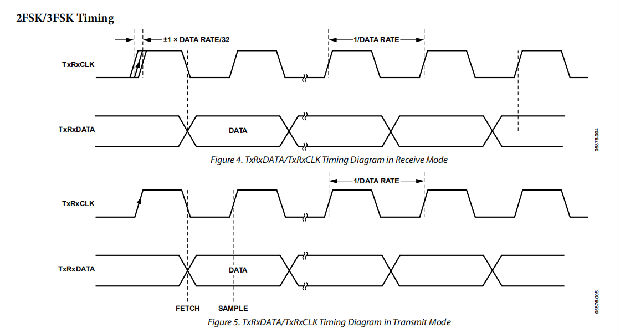

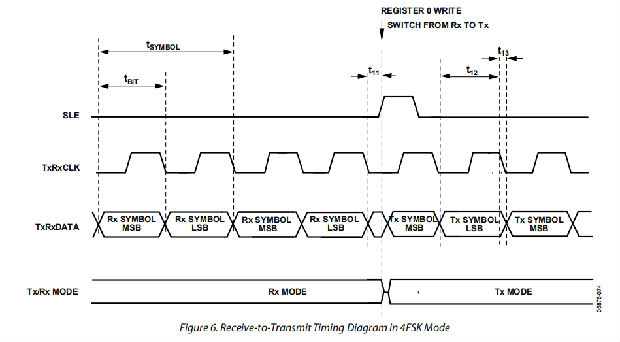

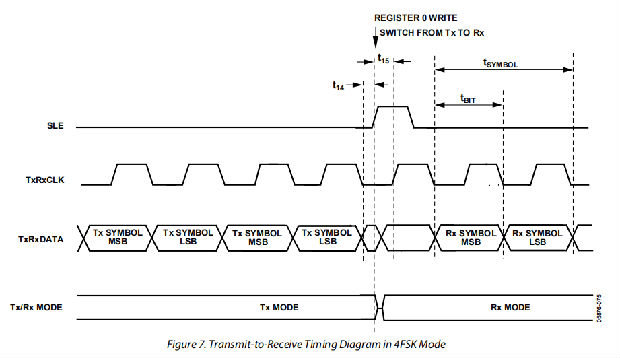

4FSK定时

在4FSK接收模式下,接收比特流中的SWD保证MSB/LSB同步。

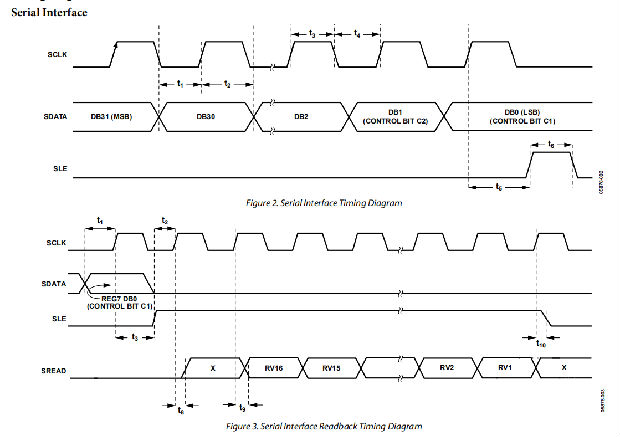

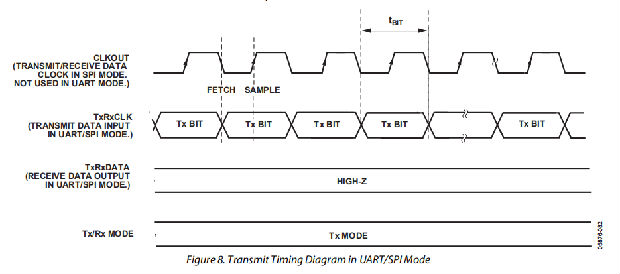

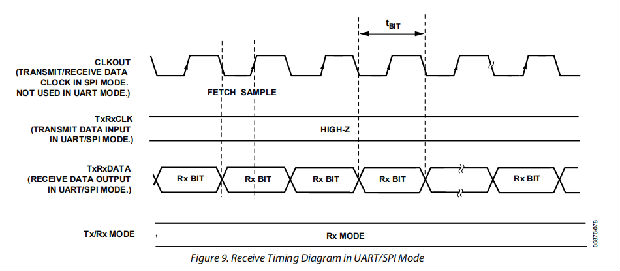

UART/SPI模式

通过将R0_DB28设置为1启用UART模式。通过将R0_DB28设置为1并将R15_DB[17:19]设置为0x7来启用SPI模式。传输/接收数据时钟在CLKOUT引脚上可用。

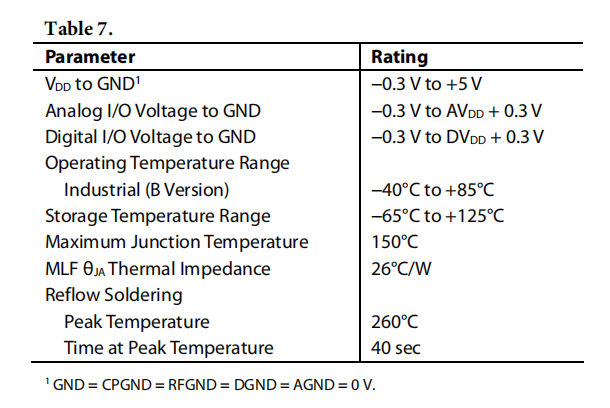

绝对最大额定值

T=25°C,除非另有说明。

大于或等于绝对最大额定值的应力可能会对产品造成永久性损坏。这仅是一个应力等级;不暗示产品在本规范操作部分所述条件或以上任何其他条件下的功能运行。超过最大运行条件的长时间运行可能会影响产品的可靠性。

该器件是一种高性能射频集成电路,ESD额定值<2kv,对ESD敏感。在搬运和装配时采取适当的预防措施。

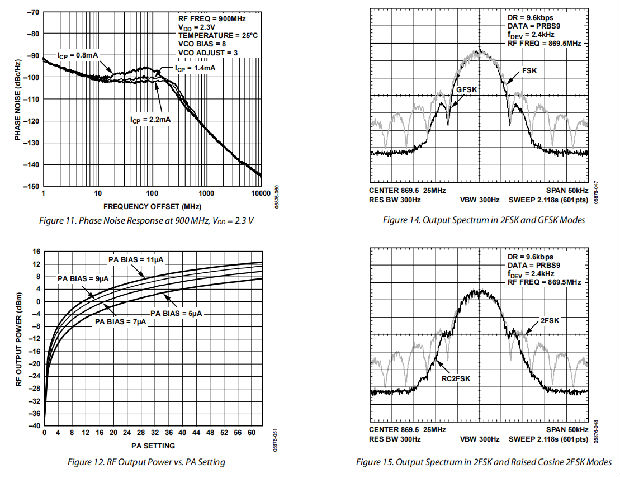

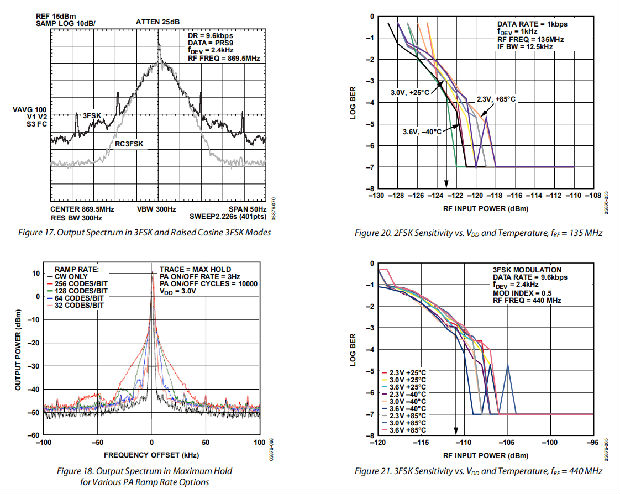

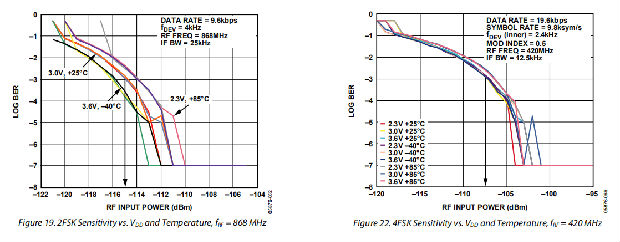

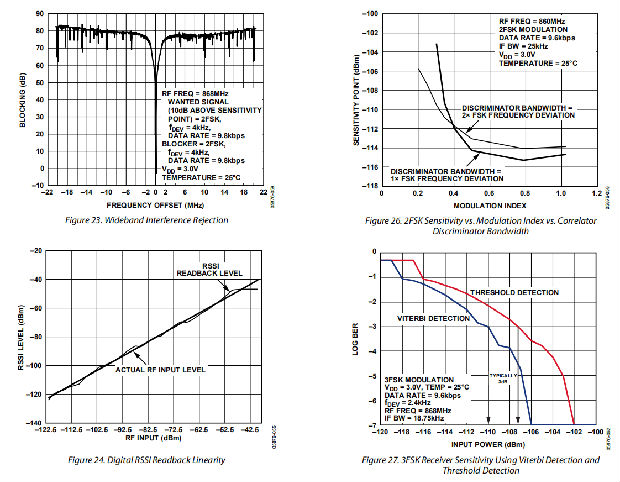

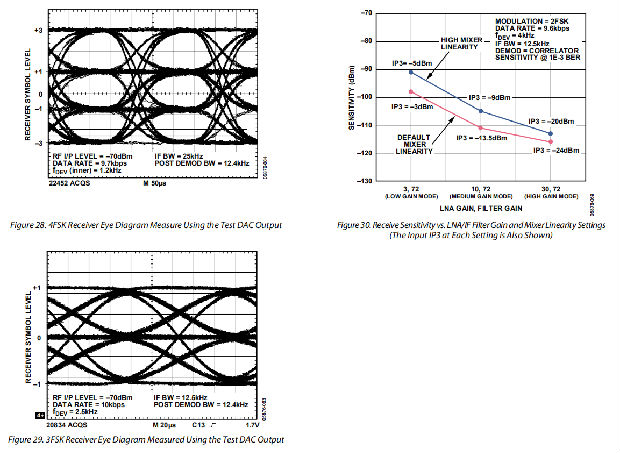

典型性能特征

频率合成器

参考输入

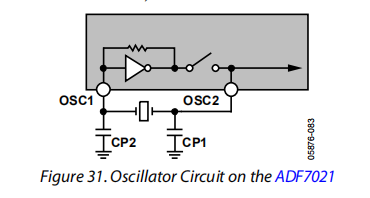

车载晶体振荡器电路(见图31)可以使用石英晶体作为PLL参考。建议在窄带应用中使用频率公差小于等于10ppm的石英晶体。可以使用公差大于10ppm的石英晶体,但为了符合窄带规定的绝对频率误差规范(例如,ARIB STD-T67和ETSI EN 300-220),必须对晶体的频率误差进行补偿。

振荡器电路通过设置R1-DB12高来启用。默认情况下,在通电时启用,并通过降低CE禁用。晶体中的误差可以通过使用自动频率控制功能或通过调整小数-N值来校正(参见N计数器部分)。

在正确的频率下振荡需要两个并联谐振电容器。它们的值取决于晶体的规格。在选择电容器的值时,请确保添加到PCB轨道电容的电容串联值等于晶体的指定负载电容,通常为12 pF到20 pF。轨道电容值从2 pF到5 pF不等,具体取决于电路板布局。如果可能,选择温度系数非常低的电容器,以确保在所有条件下稳定的频率运行。

使用TCXO引用

单端引用(TCXO、VCXO或OCXO)也可以与ADF7021一起使用。对于绝对频率精度要求小于10ppm的应用,如ARIB STD-T67或ETSI EN 300-220,建议采用该方法。ADF7021与外部参考振荡器的接口有两种选择。

•具有CMOS输出电平的振荡器可应用于OSC2。通过设置R1-DB12低,禁用内部振荡器电路。

•0.8 V p-p电平的振荡器可以通过22 pF电容器交流耦合到OSC1中。通过设置R1-DB12高来启用内部振荡器电路。

可编程晶体偏压电流

振荡器电路中的偏置电流可以通过写入XTAL_偏置位(r1u DB[13:14])在20μA和35μA之间配置。增大偏置电流可以使晶体振荡器更快地通电。

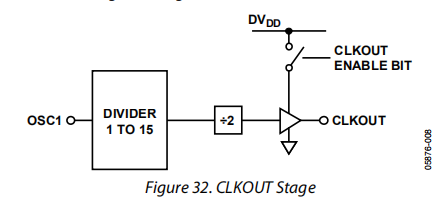

CLKOUT除法器和缓冲器

CLKOUT电路从振荡器部分获取参考时钟信号,如图32所示,并向CLKOUT管脚提供一个向下50:50的标记空间信号。CLKOUT信号相对于基准时钟是反向的。2到30之间的均分是可用的。这个除数是在R1_分贝[7:10]。通电时,CLKOUT默认为除以8。

要禁用CLKOUT,请将除数设置为0。输出缓冲区可以驱动高达20pf的负载,在4.8mhz下有10%的上升时间。更快的边缘可能会导致对输出的一些杂散馈通。一个串联电阻(1kΩ)可以用来减缓时钟边缘,以减少时钟频率的这些杂散。

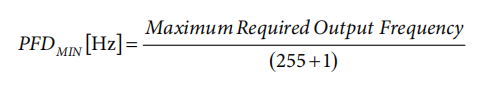

R计数器

3位R计数器将参考输入频率除以1到7的整数。分频信号被作为基准时钟提供给相位频率检测器(PFD)。分频比设置为R1_DB[4:6]。最大化PFD频率会降低N值。这将减少以20 log(N)的速率乘以输出的噪声,并减少杂散分量的出现。

寄存器1在通电时默认为R=1。

PFD[Hz] = XTAL/R

环路滤波器

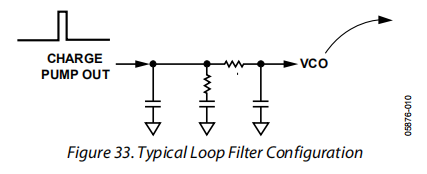

环路滤波器集成来自电荷泵的电流脉冲,形成一个电压,将VCO的输出调谐到所需频率。它还可以减弱PLL产生的杂散电平。典型的环路滤波器设计如图33所示。

设计环路,使环路带宽(LBW)约为100 kHz。这在带内相位噪声和带外杂散抑制之间提供了一个很好的折衷方案。增大LBW过多地减少了在频率之间跳跃的时间,但它可能导致不充分的杂散注意。窄的环路带宽会导致环路花费很长的时间来实现锁定,也会导致较高的功率落入相邻信道。在EVAL-ADF7021DB评估板上使用环路滤波器设计,以获得最佳性能。

自由设计工具adispll也可以用来为ADF7021设计环路滤波器。

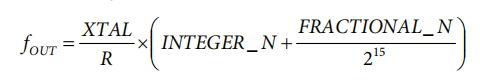

N计数器

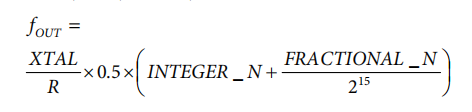

ADF7021锁相环中的反馈分频器由一个8位整数计数器(R0_DB[19:26])和一个15位∑-Δ分数分频器(R0_DB[4:18])组成。整数计数器是PLLs中常见的标准脉冲吞入类型。这将最小整除值设置为23。分数分频值在输出端提供非常精细的分辨率,其中PLL的输出频率计算为:

当选择RF_除以_2(参见压控振荡器(VCO)部分)时,此公式变为:

整数N(最大值=255)和小数N(最大值=32768/32768)的组合给出了255+1的最大N除法器。因此,最小可用PFD为:

例如,当在欧洲868mhz到870mhz波段工作时,PFDMIN等于3.4mhz。

电压调节器

ADF7021包含四个稳压器,为设备提供稳定的电压。额定调节器电压为2.3 V。调节器1需要在CREG1和GND之间串联一个3.9Ω电阻器和一个100 nF电容器,而其他调节器需要在CREGx和GND之间连接一个100 nF电容器。当CE高时,调节器和其他相关电路通电,总供电电流为2ma。将CE引脚调低将禁用调节器,将电源电流降低到小于1μA,并清除寄存器中保存的所有值。串行接口通过调节器电源工作。因此,要写入设备,用户必须具有CE高和稳压器电压必须稳定。调节器状态(CREG4)可以使用来自MUXOUT的调节器就绪信号进行监控。

MUXOUT

MUXOUT引脚允许访问ADF7021中的各种数字点。MUXOUT的状态由R0_DB[29:31]控制。

调节器准备就绪

REGULATOR_READY是收发器通电后MUXOUT的默认设置。调节器的通电时间通常为50μs。由于串行接口由调节器供电,因此调节器必须在其标称电压下才能对ADF7021进行编程。调节器的状态可以在MUXOUT进行监控。当MUXOUT上的调节器就绪信号高时,可以开始对ADF7021进行编程。

过滤完成

MUXOUT可以设置为FILTER_CAL_COMPLETE。在粗中频滤波器校准和精中频滤波器校准期间,此信号变低。它可以用作微控制器的中断,以发出中频滤波器校准结束的信号。

数字锁检测

数字锁定检测指示PLL何时锁定。

锁定检测电路位于PFD上。当五个连续周期的相位误差小于15ns时,锁定检测设置为高。锁定检测保持高电平,直到在PFD处检测到25 ns相位错误。

准备就绪

MUXOUT可以设置为RSSI_READY。这表明内部模拟RSSI已经稳定,并且可以执行数字RSSI回读。

发送/接收

Tx_Rx表示ADF7021处于发送模式还是接收模式。当处于传输模式时,此信号为低电平。当处于接收模式时,此信号为高。它可用于控制外部Tx/Rx开关。

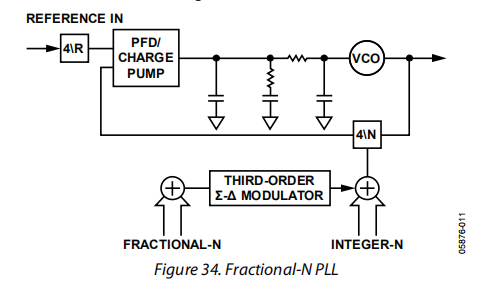

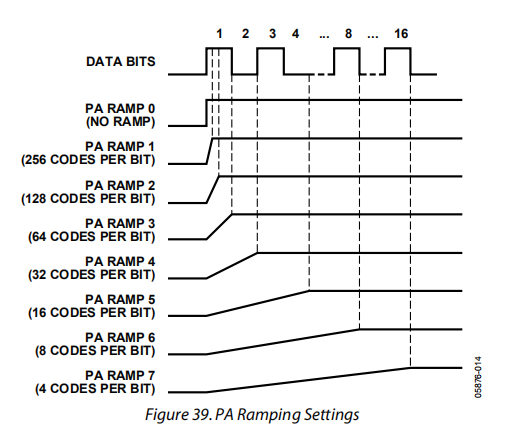

压控振荡器

ADF7021包含两个VCO核心。第一个VCO,内部电感VCO,使用内部LC槽,支持862兆赫至950兆赫和431兆赫至475兆赫的工作频带。第二个VCO,即外部电感VCO,使用外部电感作为其LC槽的一部分,并支持80 MHz到650 MHz的射频工作频带。

为了减少杂散发射,两个VCO的工作频率都是射频频率的两倍。VCO信号然后在合成器环路内除以2,给出发射机所需的频率和接收机所需的本地振荡器(LO)频率。在合成器环路之外执行进一步的除以2(RF除以2),以允许在431 MHz到475 MHz频带(内部电感VCO)和80 MHz到325 MHz频带(外部电感VCO)中操作。

VCO需要在CVCO引脚和调节器(CREG1)之间有一个外部22 nF电容器来降低内部噪声。

内电感VCO

要选择内部电感VCO,请将R1_DB25设置为逻辑0,这是默认设置。

VCO偏置电流可使用R1 DB[19:22]进行调整。为保证压控振荡器的振荡,使用内电感压控振荡器时,所有条件下的最小偏置电流设置为0x8。

根据所需的工作频率,通过编程VCO_调整位(R1_DB[23:24])重新输入VCO。详见表9。

外电感VCO

在使用外电感压控振荡器时,压控振荡器的中心频率由内部变容二极管电容和外部芯片电感、键合线和印刷电路板轨道的组合电感来设定。外部电感连接在L2和L1引脚之间。

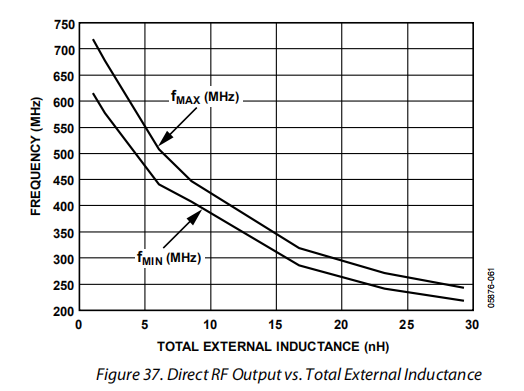

VCO工作频率与总外部电感(芯片电感+PCB轨迹)的关系图如图37所示。

使用FR4材料的PCB磁道电感约为0.57nh/mm。从总值中减去该值以确定正确的芯片电感值。

通常,特定的电感值允许ADF7021在RF工作频率的±6%范围内工作。当选择RF_除以_2位(R1_DB18)时,该范围变为±3%。例如,在400兆赫时,可以预期具有单个电感器(以400兆赫为中心的VCO范围)的工作范围为±24兆赫(即376兆赫至424兆赫)。

当设备在发射或接收模式下完全通电时,可以通过测量VCO in管脚上的电压来检查VCO调谐电压是否具有特定的RF输出频率。

VCO调谐范围为0.2 V至2 V。选择外部电感值以确保VCO工作时尽可能接近该调谐范围的中心。这对于射频频率<200mhz尤其重要,其中VCO增益降低并且存在<±6mhz的调谐范围。

VCO工作频率范围可以通过编程VCO_调整位(R1_DB[23:24])来调整。这通常允许VCO工作范围向上或向下移动最多1%的射频频率。

要选择外部电感VCO,请将R1_DB25设置为逻辑1。根据工作频率设置VCO_偏置电流(如表9所示)。

选择最佳系统性能的通道

射频压控振荡器频率和参考频率之间的相互作用可导致分数杂散的产生。当合成器处于分数模式(即,RF VCO和参考频率不是整数相关的)时,在对应于参考频率的整数倍和VCO频率之间的差频的偏移频率处,VCO输出频谱上可能出现杂散。

这些杂散被环路滤波器衰减。它们在接近参考的整数倍的信道上更明显,其中差频可能在环路带宽内;因此,名称整数边界杂散。这些杂散的发生是罕见的,因为整数频率大约是参考频率的倍数,通常大于10兆赫。为了避免分数寄存器中有非常小或非常大的值,请选择适当的参考频率。

发射机

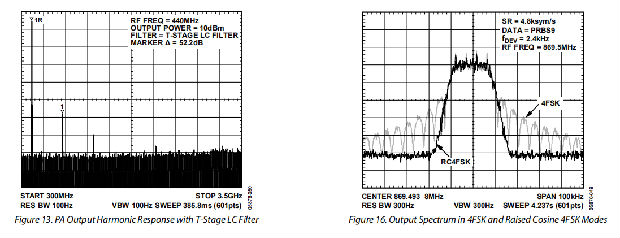

射频输出级

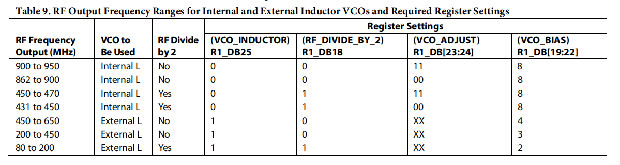

ADF7021的功率放大器(PA)基于一个单端、可控电流、开漏放大器,其设计可在950兆赫的最大频率下向50Ω负载提供高达13 dBm的电流。

功率放大器的输出电流和输出功率可以在很宽的范围内进行编程。PA配置如图38所示。使用R2_DB[13:18]设置输出功率。

功率放大器配有过电压保护,使其在严重失配条件下具有鲁棒性。根据应用,用户可以为PA设计一个匹配网络,以在诸如环形天线或单极天线等宽范围天线的期望辐射输出功率水平下显示最佳效率。有关详细信息,请参阅LNA/PA匹配部分。

PA斜坡

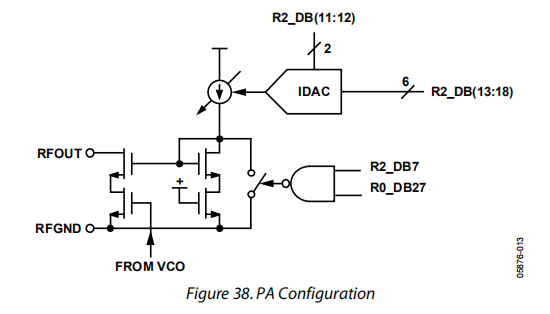

当PA快速打开或关闭时,其变化的输入阻抗会瞬间干扰VCO的输出频率。这个过程被称为VCO拉,它表现为输出频谱中围绕期望载波频率的光谱飞溅或杂散。一些无线电发射法规对这些PA瞬态诱发的杂散进行了限制(例如,ETSI EN 300 220)。通过逐渐增加功率放大器的开和关,功率放大器的瞬态脉冲被最小化。

ADF7021具有内置PA斜坡配置。如图39所示,有八个斜坡速率设置,定义为每一个数据位周期的特定数量的PA设置码。PA通过64个代码级别中的每一个,但每个设置的速度不同。通过配置R2_DB[8:10]来设置斜坡速率。

如果PA通过PA_ENABLE(R2_DB7)启用/禁用,则它以编程速率递增,但很难关闭。如果PA由Tx/Rx(R0_DB27)启用/禁用,则它以编程速率递增和递减。

PA偏置电流

如有必要,PA_偏置位(R2_DB[11:12])有助于调整PA偏置电流以进一步扩展输出功率控制范围。如果不需要此功能,建议使用默认值9μA。如果需要大于10 dBm的输出功率,建议将PA偏置设置为11μa。通过重置R2-DB7关闭输出级。

调制方案

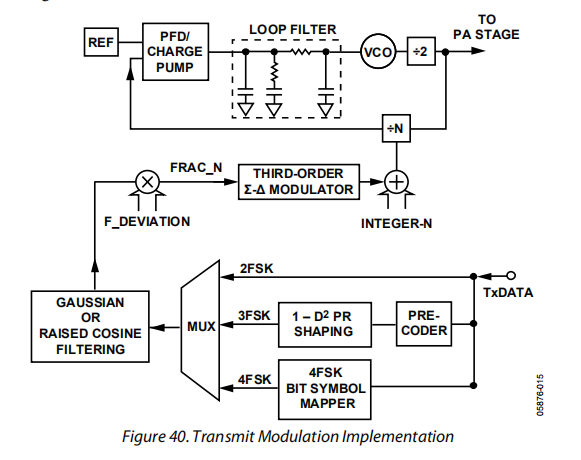

ADF7021支持2FSK、3FSK和4FSK调制。这些调制方案的实现如图40所示。

设置传输数据速率

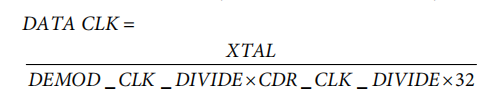

在除过采样2FSK模式以外的所有调制模式中,在TxRxCLK引脚上提供精确的时钟,以以所需的数据速率将微控制器的数据锁存到发送部分。这个时钟的确切频率由:

其中:XTAL是晶体或TCXO频率。

DEMOD_CLK_DIVIDE是设置解调器时钟速率(R3_DB[6:9])的除法器。

CDR_CLK_DIVIDE是设置CDR时钟速率(R3_DB[10:17])的除法器。

有关更多编程信息,请参阅寄存器3-发送/接收时钟寄存器部分。

设置FSK发送偏差频率

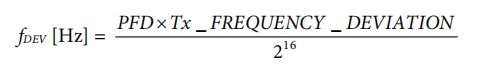

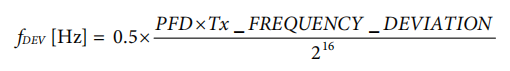

在所有调制模式中,使用Tx_frequency_deviation位(R2_DB[19:27])设置与中心频率的偏差。

与中心频率的偏差(单位:Hz)如下:

对于直接射频输出,

对于RF_除以_2启用,

其中:Tx_频率_偏差是1到511之间的数字(R2_DB[19:27])。

在4FSK调制中,4个符号(00,01、11,10)分别以±3×fDEV和±1×fDEV的形式发送。

二进制频移键控(2FSK)

通过设置中心频率的N值,然后将其与TxDATA线切换。使用Tx_frequency_deviation位R2_DB设置与中心频率的偏差[19:27]。

通过将调制方案位(r2u DB[4:6])设置为000来选择2FSK。

最小移位键控(MSK)或高斯最小移位键控(GMSK)通过选择2FSK调制并使用0.5的调制指数来支持。通过为频率配置R2_DB[19:27]设置调制指数0.5=偏离0.25×传输数据速率。

三电平移频键控(3FSK)

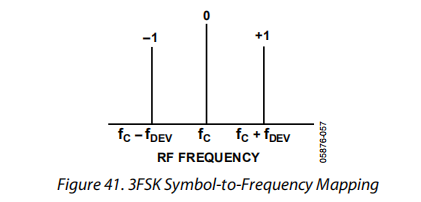

在三电平FSK调制(也称为修正双二进制FSK)中,二进制数据(逻辑0和逻辑1)映射到三个不同的频率上,即载波频率(fC)、载波频率减去偏差频率(fC-fDEV)和载波频率加上偏差频率(fC+fDEV)。

逻辑0映射到载波频率,而逻辑1映射到频率fC-fDEV或fC+fDEV。

与2FSK相比,这种比特-频率映射导致传输带宽的减少,因为一些能量从射频边带中移除并传输到载波频率。在低调制指数下,3FSK比2FSK提高了25%的发射频谱效率。

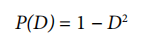

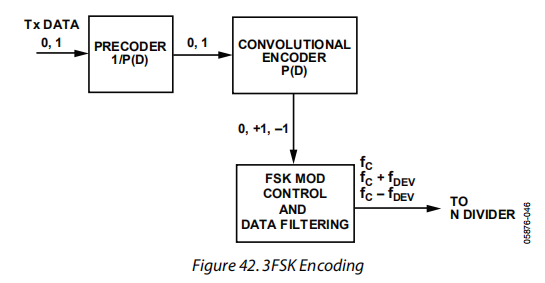

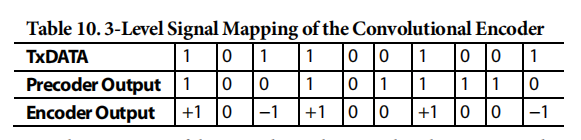

3FSK的位到符号映射使用线性卷积编码器来实现,该编码器还允许在接收机中使用Viterbi检测。用于实现该系统的发送硬件的框图如图42所示。用于实现发射光谱整形的卷积编码器多项式是:

其中:P是卷积编码器多项式;D是单位延迟运算符。

具有传递函数1/P(D)的数字预编码器实现发射机中1-D2成形滤波器的逆模2操作。

表10示出了输入二进制发送数据到3级卷积输出的信号映射。卷积编码器将最大序列+1s或-1s的数目限制为2,并将相同数目的+1s和-1s传送到FSK调制器,从而确保两个RF边带中的频谱能量相等。

该编码方案的另一个特点是发送的码元序列是无直流的,这有利于在接收机中进行码元检测和频率测量。此外,不存在与该3级卷积编码器相关联的码速率损失;即,发送符号速率等于在发送数据输入处呈现的数据速率。

通过将调制方案比特(R2 DB[4:6])设置为010来选择3FSK。它还可以与升余弦滤波一起使用,以进一步提高发射信号的频谱效率。

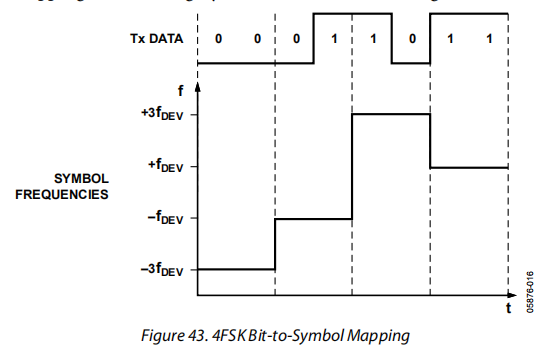

四电平移频键控(4FSK)

在4FSK调制中,通过将Tx数据比特流中的连续输入比特对映射到四个可能的符号中的一个来实现每符号两位的频谱效率(-3、-1、+1、+3)。因此,发送的符号速率是输入比特速率的一半。

通过最小化符号频率之间的间隔,4FSK可以具有较高的频谱效率。4FSK的位到符号映射是灰色编码的,如图43所示。

内部偏差频率(+fDEV和-fDEV)使用Tx_FREQUENCY_偏差位R2_DB设置[19:27]。外部偏差频率自动设置为内部偏差频率的三倍。

从Pin TxRxCLK发送时钟在写入接收模式的通电序列中的寄存器3后可用。将第一个符号的MSB写入到寄存器3后,在从ADF7021发送的第一个时钟脉冲上对ADF7021进行时钟。有关更多计时信息,请参阅图6。

过采样2FSK

在过采样2FSK中,没有来自TxRxCLK引脚的数据时钟。相反,TxRxDATA引脚处的传输数据以32倍编程速率采样。

这是唯一可与UART模式接口一起用于数据传输的调制模式(有关更多信息,请参阅与微控制器/DSP的接口部分)。

光谱整形

高斯或升余弦滤波可用于提高发射光谱效率。ADF7021在2FSK调制上支持高斯滤波(带宽时间[BT]=0.5)。升余弦滤波可用于2FSK、3FSK或4FSK调制。升余弦滤波器的滚降系数(α)具有0.5和0.7的可编程选项。高斯和升余弦滤波器均采用线性相位数字滤波器结构实现,对BT和alpha滤波器参数进行精确控制,并保证发射光谱在温度和电源变化下非常稳定。

高斯频移键控(GFSK)

高斯频移键控通过对发射数据进行数字预滤波来减少发射频谱占用的带宽。高斯滤波器的BT积为0.5。

高斯滤波只能用于2FSK调制。这是通过将R2_DB[4:6]设置为001来选择的。

升余弦滤波

升余弦滤波通过使用滚降系数(α)为0.5或0.7的升余弦滤波器来提供发送数据的数字预滤波。默认情况下,alpha设置为0.5,但是可以通过使用alpha 0.7(将R2-DB30设置为逻辑1)来增加提升的余弦滤波器带宽,以提供不太积极的数据过滤。升余弦滤波可用于2FSK、3FSK和4FSK。

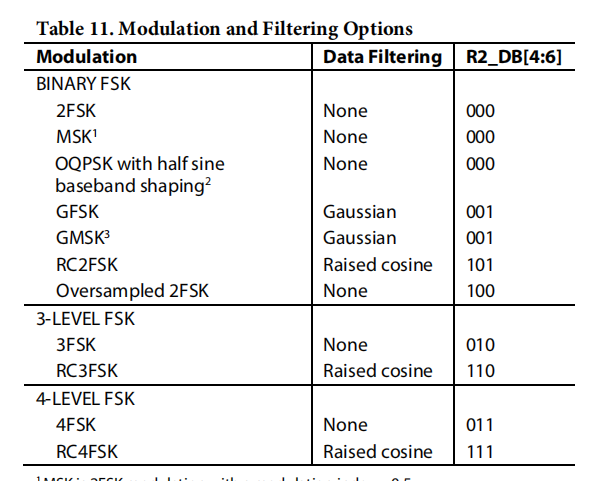

如表11所示,通过设置R2 DB[4:6]启用升余弦滤波。

调制和滤波选项

表11描述了各种调制和数据滤波选项。

1、MSK是2FSK调制,调制指数为0.5。

2、半正弦基带成形的偏移正交相移键控(OQPSK)在频谱上等价于MSK。

3、GMSK是调制指数为0.5的GFSK。

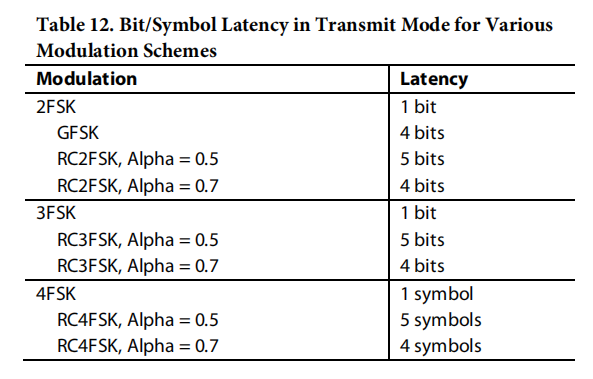

传输延迟

传输延迟是从TxRxCLK信号对位/符号进行采样到该位/符号出现在RF输出时的延迟时间。没有任何数据过滤的延迟是1位。如表12所示,数据过滤的添加增加了进一步的延迟。

重要的是,在数据时钟对最后一个数据位进行采样后,ADF7021保持在传输模式,以解释此延迟。将ADF7021保持在发送模式中的时间等于所应用调制方案的延迟比特周期数。这确保了由TxRxCLK信号采样的所有数据出现在RF处。

表12中的延迟数字假定正的TxRxCLK边缘用于采样数据(默认)。如果通过设置R2 DB[28:29]来反转TxRxCLK,则可以向表12中的所有值添加额外的0.5位延迟。

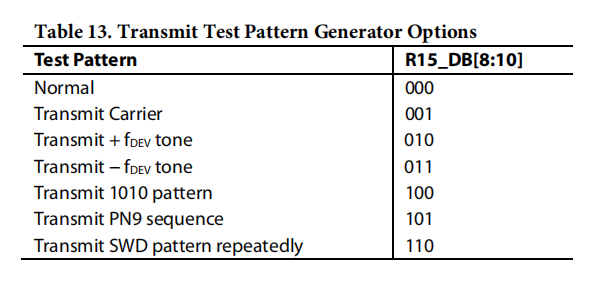

测试模式生成器

ADF7021有许多内置的测试模式发生器,可用于促进无线链路设置或射频测量。支持的模式的完整列表如表13所示。这些测试模式的数据速率是在寄存器3中设置的编程数据速率。

PN9序列适合在执行相邻信道功率(ACP)或占用带宽测量时进行测试调制。

接收器部分

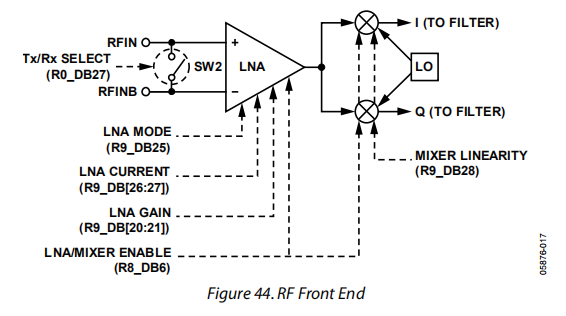

射频前端

ADF7021基于完全集成的低中频接收机架构。低中频架构有助于非常低的外部组件计数,并且不受电力线引起的干扰问题的影响。

图44显示了接收器前端的结构。许多编程选项允许用户权衡灵敏度、线性度和电流消耗,以最适合其应用。为了获得高水平的抗杂散接收能力,低噪声放大器(LNA)采用差分输入。选择传输模式时,开关SW2使LNA输入短路(R0_DB27=0)。此功能有助于设计组合的LNA/PA匹配网络,避免需要外部Rx/Tx交换机。有关匹配网络设计的详细信息,请参阅LNA/PA匹配部分。

LNA之后是正交下变频混频器,它将RF信号转换为100khz的IF频率。一个重要的考虑是,合成器的输出频率必须编程为低于接收信道中心频率100 kHz的值。低噪声放大器有两种基本工作模式:高增益/低噪声模式和低增益/低功率模式。要在这两种模式之间切换,请使用LNA_MODE位(R9_DB25)。混频器还可使用混频器线性位(R9_DB28)在低电流和增强线性模式之间配置。

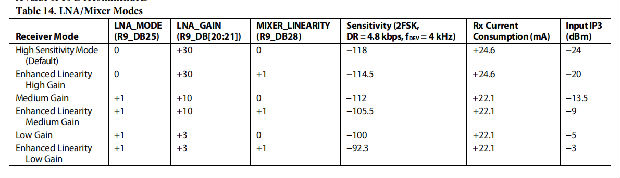

根据应用的特定灵敏度和线性要求,建议如表14所示调整LNA_模式位和混频器_线性位。

LNA的增益由LNA增益位(R9_DB[20:21])配置,并且可以由用户或自动增益控制(AGC)逻辑设置。

中频滤波器

如果筛选器设置

通过以100khz频率为中心的五阶巴特沃斯多相中频滤波器来抑制带外干扰。中频滤波器的带宽可编程为12.5 kHz、18.75 kHz或25 kHz×R4_DB[30:31];选择滤波器值作为所需信号的干扰抑制和衰减之间的折衷。

如果AGC环路被禁用,则可以使用滤波器增益位(R9_DB[22:23])将If滤波器的增益设置为三个电平之一。如果启用AGC回路,滤波器增益将自动调整。

中频滤波器带宽与中心频率校准

为了补偿制造公差,在通电后校准中频滤波器,以确保带宽和中心频率正确。提供粗校准和精校准方案,以便在快速校准(粗校准)和高过滤器定心精度(精校准)之间进行选择。通过将R5_DB4设置为高,可启用粗校准。通过设置R6_DB4高,可以进行精细校准。

有关何时需要执行滤波器校准以及在哪些应用程序中使用粗略校准或精细校准的详细信息,请参阅IF filter Bandwidth calibration部分。

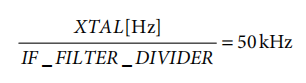

在进行精细校准之前,必须进行粗略校准。如果If_FINE_CAL位(R6_DB4)已配置为高,则可以通过仅写入寄存器5来进行精细校准。一旦通过写入设备启动,校准将自动执行,无需任何用户干预。粗略校准的校准时间为200μs,精细校准的校准时间为几毫秒,在此期间不得访问ADF7021。IF filter校准逻辑要求将IF_filter_除法器位(R5_DB[5:13])设置为:

中频滤波器精细校准概述

精细校准使用两个内部生成的音调在中频滤波器周围的特定偏移处。LNA暂时与接收器链分离,以确保外部信号不会影响校准。这两个音调被IF滤波器衰减,并且使用RSSI测量这种衰减的水平。调整滤波器中心频率,使两个音调的衰减相等。然后重新测量两个测试音调的衰减。这将继续进行最多10个RSSI测量,在此阶段,校准算法将IF滤波器中心频率设置为100 kHz的0.5 kHz以内。

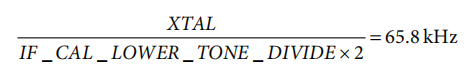

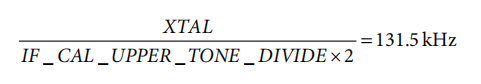

这些音调的频率由以下位设置:

•IF_CAL_LOWER_TONE_DIVIDER(R6_DB[5:12])

•IF_CAL_UPPER_TONE_DIVIDER(R6_DB[13:20])

建议将低音和高音分别放置在尽可能接近65.8 kHz和131.5 kHz的位置,如下式所示:

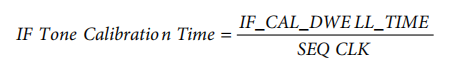

校准算法调整滤波器中心频率,并在校准过程中测量10次RSSI。调整加RSSI测量的时间由下式给出:

建议IF-tone校准时间至少为500μs。IF-filter精细校准的总时间如下:

中频滤波器精校准时间=中频音校准时间×10

RSSI/AGC系统

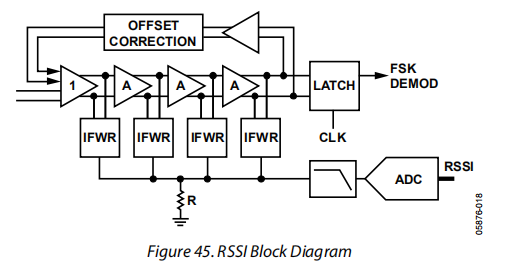

RSSI被实现为继基带(BB)信道滤波之后的连续压缩对数放大器。对数放大器的对数线性度达到±3db。它还兼作限制器,将信号转换为FSK解调器的数字电平。偏移校正电路使用BBOS-CLK-u除法位(R3-DB[4:5]),该除法位必须设置在1 MHz和2 MHz之间。RSSI电平通过80电平(7位)flash ADC转换为用户回读和数字控制AGC。该电平可转换为输入功率,单位为dBm。默认情况下,AGC在接收模式下通电时打开。

RSSI阈值

当RSSI高于AGC_HIGH_阈值(R9_DB[11:17])时,增益降低。当RSSI低于AGC_LOW_阈值(R9_DB[4:10])时,增益增加。在接收模式下通电时,阈值默认为30和70。延迟(由AGC时钟除法设置,R3_DB[26:31])已编程以允许环路的设置。建议值为10。

用户可以选择从默认值30和70(寄存器9)更改这两个阈值。确保默认AGC设置值适合大多数应用程序。必须选择相隔30多个阈值,AGC才能正常工作。

偏移校正时钟

在寄存器3中,设置BBOS-CLK-u除法位(R3-DB[4:5])以给出1 MHz到2 MHz之间的基带偏移时钟(BBOS-CLK)频率。

BBOS CLK餐厅[Hz]=XTAL/(BBOS_CLK_除法)

其中BBOS_CLK_DIVIDE可以设置为4、8、16或32。

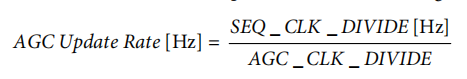

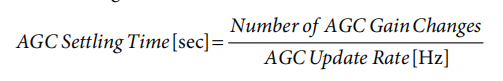

AGC信息和定时

自动增益控制(AGC)是默认选择,通过为测量的RSSI电平设置适当的LNA和滤波器增益设置来操作。如果用户想输入表14中列出的模式之一,可以通过写入寄存器9来禁用AGC。AGC电路的稳定时间,因此,精确测量RSSI所需的时间,通常为300μs。然而,这取决于AGC电路必须循环多少个增益设置。每次增益变化后,AGC回路等待编程时间,以允许瞬态稳定。此AGC更新率根据:

其中:AGC_CLK_DIVIDE由R3_DB设置[26:31]。建议值为10。

SEQ_CLK_DIVIDE=100千赫(R3_分贝[18:25])。

通过使用AGC_CLK_DIVIDE的建议设置,AGC的总设置时间为:

AGC调节的最坏情况是AGC控制回路必须循环通过所有五个增益设置,这使得AGC调节的最大时间为500μs。

RSSI公式(转换为dBm)

RSSI公式是:

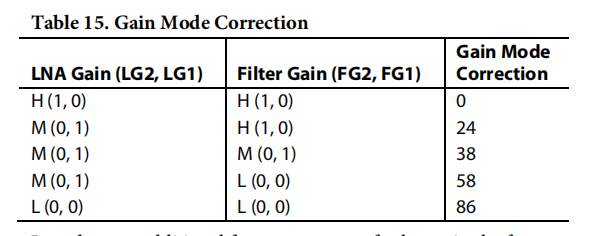

输入功率[dBm]=–130 dBm+(回读码+增益模式校正)×0.5

其中:回读代码由回读寄存器中的位RV7到位RV1给出(见回读格式部分)。

增益模式校正由表15中的值给出。

LNA增益(LG2,LG1)和滤波器增益(FG2,FG1)值也作为RSSI回读的一部分从回读寄存器获得。

引入一个附加因素来说明前端匹配网络/天线中的损耗。

解调、检测和CDR

系统概述

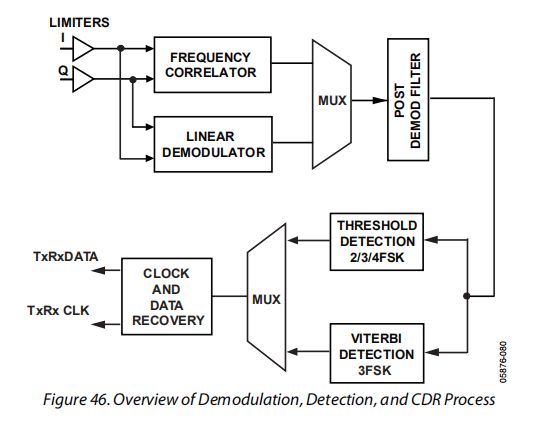

图46显示了ADF7021上接收信号的解调、检测、时钟和数据恢复(CDR)的概述。

IF滤波器的正交输出首先被限制,然后馈送到相关器FSK解调器或线性FSK解调器。相关解调器用于解调2FSK、3FSK和4FSK。线性解调器用于频率测量,并在AFC环路激活时启用。线性解调器也可用于解调2FSK。

在解调器之后,数字后解调滤波器从解调器信号输出中去除多余的噪声。阈值/切片器检测用于2FSK和4FSK的数据恢复。3FSK的数据恢复可以使用阈值检测或Viterbi检测来实现。

片上CDR-PLL用于将接收到的比特流重新同步到本地时钟。它分别在TxRxDATA和TxRxCLK管脚上输出重定时数据和时钟。

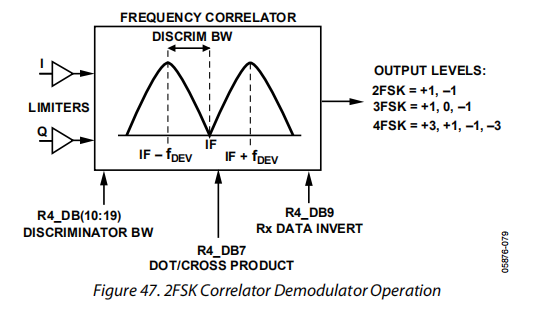

相关解调器

相关解调器可用于2FSK、3FSK和4FSK解调。图47显示了2FSK的相关解调器的操作。

IF滤波器的正交输出首先被限制,然后被馈送到数字频率相关器,该数字频率相关器执行2FSK/3FSK/4FSK频谱的滤波和频率辨别。

对于2FSK调制,通过比较两个相关器的输出电平来恢复数据。该鉴频器的性能接近匹配滤波器检测器的性能,在加性高斯白噪声(AWGN)的情况下,匹配滤波器检测器具有最佳的检测性能。这种FSK解调方法比线性解调器提供了大约3db到4db更好的灵敏度。

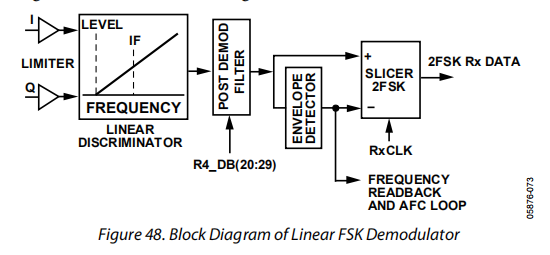

线性解调器

图48示出了线性解调器的框图。

数字鉴频器提供与限制器输出频率成线性比例的输出信号。鉴别器的输出通过一个组合的平均滤波器和包络检测器进行滤波和平均。从后解调滤波器解调的2FSK数据通过检测包络检测器输出的阈值来恢复,如图48所示。当接收到的频谱接近或在中频带宽内时,这种解调方法校正发射机和接收机之间的频率误差。此包络检测器输出也用于AFC回读,并为AFC控制回路提供频率估计。

后解调滤波器

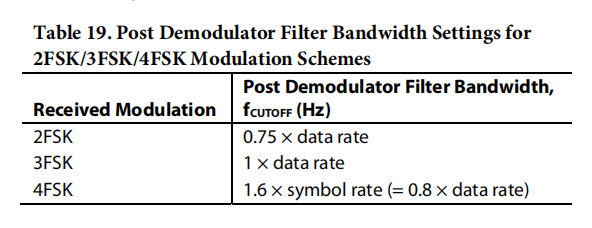

二阶数字低通滤波器去除鉴别器输出端解调比特流中的多余噪声。此后解调滤波器的带宽是可编程的,必须针对用户的数据速率和接收调制类型进行优化。如果带宽设置得太窄,性能会因码间干扰(ISI)而降低。如果带宽设置得太宽,过大的噪声会降低接收器的性能。后置解调器(R4_DB[20:29])设置此滤波器的带宽。

2FSK位切片器/阈值检测

2FSK解调可以使用相关FSK解调器或线性FSK解调器来实现。在这两种情况下,阈值检测用于解调后滤波器输出处的数据恢复。

相关解调器的输出信号电平总是以零为中心。因此,切片器的阈值电平可以固定在零,解调器的性能与传输数据比特流的游程限制无关。这导致了稳健的数据恢复,而不受传统FSK解调器中存在的经典基线漂移问题的影响。

当线性解调器用于2FSK解调时,包络检测器的输出被用作切片器阈值,该输出跟踪中频滤波器带宽内的频率误差。

3FSK和4FSK阈值检测

4FSK解调采用相关解调器、后解调滤波器和阈值检测实现。解调后滤波器的输出是表示发送符号(-3、-1、+1、+3)的4电平信号。4FSK的阈值检测需要三个阈值设置,一个总是固定在0,两个是可编程的,并且使用3FSK/4FSK_切片器阈值位(R13_DB[4:10])对称地置于0之上和之下。

3FSK解调是使用相关解调器实现的,接着是解调后滤波器。后解调滤波器的输出是表示发送符号的3电平信号(-1、0、+1)。3FSK的数据恢复可以通过阈值检测或Viterbi检测来实现。使用可编程的两个阈值来实现阈值检测,并使用3FSK/4FSK_切片器阈值位(R13_DB[4:10])对称地置于零上下。

3FSK维特比检测

3FSK的Viterbi检测在四状态格架上操作,并且使用以一半符号速率操作的两个交织Viterbi检测器来实现。Viterbi检测器由R13_DB11启用。

为了便于在发送的比特流中实现不同的运行长度约束,通过设置VITERBI_路径存储位(R13_DB[13:14])。将其设置为等于或长于交织传输比特流中连续0s的最大数目。

当与Viterbi检测一起使用时,3FSK的接收机灵敏度通常比使用阈值检测获得的接收机灵敏度高+3db。然而,当Viterbi检测器被启用时,接收比特延迟增加了Viterbi路径存储器长度的两倍。

时钟恢复

过采样数字时钟和数据恢复(CDR)PLL用于在所有调制模式下将接收到的比特流重新同步到本地时钟。PLL(CDR CLK)的过采样时钟速率必须设置为符号速率的32倍(参见寄存器3-发送/接收时钟寄存器部分)。CDR-PLL的最大数据/符号速率容限由发送分组中的过零符号转换的数目来确定。例如,如果使用具有101010前导码的2FSK,则达到数据速率的±3.0%的最大公差。然而,在恢复包的其余部分时,该公差减小,其中符号转换不能保证以固定间隔发生。为了最大限度地提高CDR的数据速率容限,建议采用某种形式的编码和/或数据置乱,以保证以固定间隔进行多次转换。例如,将2FSK与Manchesterencoded数据一起使用,可获得±2.0%的数据速率公差。

CDR-PLL设计用于在前导码期间快速捕获恢复的符号,并且通常在前导码的5个符号转换内实现位同步。

在4FSK调制中,使用+3、-3、+3、-3前导码的公差为符号速率的±3%(或数据速率的±1.5%)。然而,在恢复包的其余部分时,该公差减小,其中符号转换不能保证以固定间隔发生。为了使符号/数据速率容限最大化,构造4FSK分组的剩余部分,以便通过使用数据置乱和/或通过插入特定的dc平衡符号(以固定间隔插入发送比特流中,例如每8或16个符号之后),发送的符号保持接近无dc特性。

在3FSK调制中,线性卷积编码器方案保证了发送的码元序列是无直流的,便于码元检测。然而,建议Tx数据加扰以限制发送比特流中零符号的运行长度。使用3FSK,CDR数据速率公差通常为±0.5%。

接收器设置

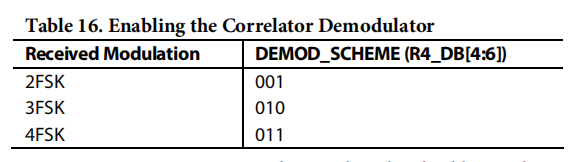

相关解调器设置

要启用各种调制模式的相关器,请参阅表16。

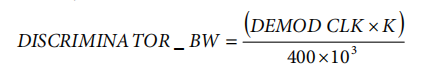

为了优化接收机灵敏度,相关器带宽必须针对发射机使用的特定偏差频率和调制进行优化。鉴别器带宽由R4 DB[10:19]控制,定义为:

其中:DEMOD CLK是在寄存器3-发送/接收时钟寄存器部分中定义的。

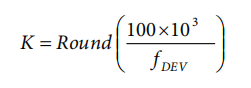

根据以下内容为每个调制模式设置K:

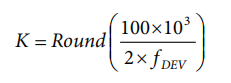

对于2FSK,

对于3FSK,

对于4FSK,

其中:舍入到最接近的整数。

Round4FSK四舍五入到下列整数中最接近的一个:32、31、28、27、24、23、20、19、16、15、12、11、8、7、4、3。

fDEV是发射频率偏差,单位为赫兹。对于4FSK,fDEV是用于±1符号的频率偏差(即内部频率偏差)。

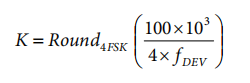

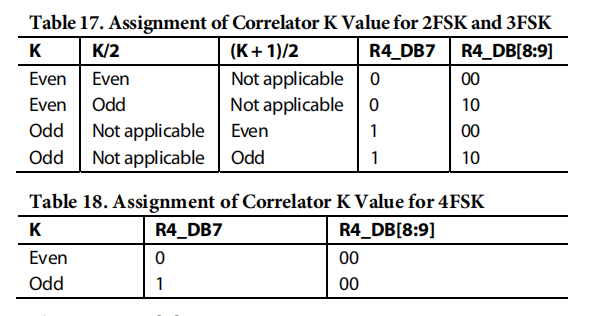

为了优化相关器的系数,还必须分配R4_DB7和R4_DB[8:9]。这些位的值取决于K是奇数还是偶数。这些位是根据表17和表18分配的。

线性解调器设置

线性解调器可用于2FSK解调。要启用线性解调器,请将解调方案位(R4_DB[4:6])设置为000。

后解调滤波器设置

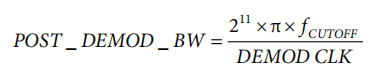

根据接收的调制类型和数据速率设置后解调滤波器的3db带宽。带宽由R4 DB[20:29]控制,由:

其中,fCUTOFF是后解调滤波器的目标3db带宽(单位:Hz)。将POST_DEMOD_BW舍入到最接近的整数值。

3FSK维特比探测器设置

Viterbi检测器可用于3FSK数据检测。这是通过将R13_DB11设置为逻辑1来激活的。

Viterbi路径存储器的长度可编程为4、6、8或32位(Viterbi路径存储器,R13-DB[13:14])。

将路径存储器长度设置为等于或大于交织传输比特流中最大连续0s数。

Viterbi检测器还使用阈值来实现最大似然检测算法。这些阈值可通过3FSK/4FSK_切片器阈值位(R13_DB[4:10])进行编程。

这些位分配如下:

其中K是为相关器鉴别器带宽计算的值。

3FSK阈值检测器设置

要激活3FSK的阈值检测,请将R13_DB11设置为逻辑0。设置3FSK/4FSK_切片器阈值位(R13_DB[4:10]),如3FSK Viterbi Detector Setupsection所述。

3FSK CDR设置

在3FSK中,建议至少40位连续1s的发送前导码,以确保CDR获得锁的最大符号转换次数。

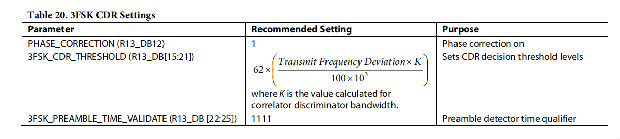

3FSK的时钟和数据恢复需要在寄存器13中设置一些参数(见表20)。

4FSK阈值检测器设置

4FSK检测器的阈值使用3FSK/4FSK_切片器阈值位(R13_DB[4:10])设置。

根据设置阈值:

其中K是为相关器鉴别器带宽计算的值。