2996点击型号即可查看芯片规格书

125点击型号即可查看芯片规格书

概要

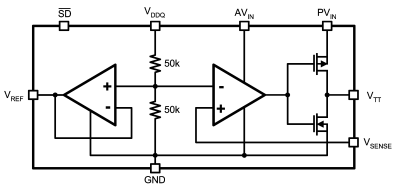

LP 2996是符合JEDEC标准的SSSTL-2规格的DDR→→→SDRAM进阶线性调整器。LP 2996是内置高速运算放大器,可以对负荷变动做出优异的响应正在做。输出级可以供给1.5A的连续电流,并且可以达到DDR调整;SDRAM调整所求的最大3A的变动峰值虽然对应,但是不会产生贯穿电流。将VSNSE端子通过监测介电电压,实现优异的输出负荷调节同时,芯片组和DDR DIMM所需的VREF电压也会产生成输出。此外,LP 2996支持Suspend-to-RAM(STR)功能的活动LOW的关机(SD)端子。SD为LOW,VTT输出为TRI-STATE的高阻抗但VREF保持活动。在本模式中待机因为时耗电流变小,所以可以节约电力。

特长

电流源及电流宿

低输出电压偏移

无需外置电阻

线性拓扑

Suspend-to-RAM(STR)功能

少量外置部件

热敏关机

SO-8、PSOP-8、LLP-16包装供应

应用程序

DDR-I和DDR-II支持断面电压

SSSTL-2和SSSTL-3层压

HSTL层压

绝对最大额定(Note 1)

动作额定

电气特性。

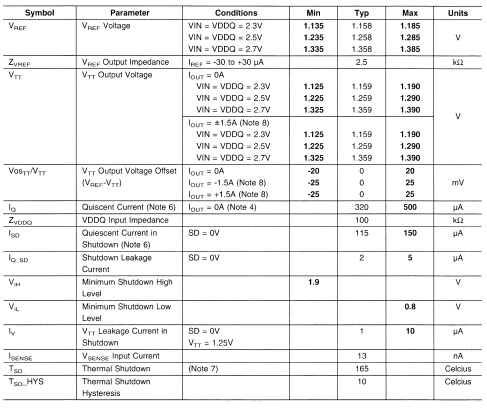

标准字体中记载的规格为TJ=25℃的情况,用粗体记载的限制值适合于“动作温度范围”(TJ=0°C~+125°C)

被使用(Note 4)。只要没有特别记载,AVIN=PVIN=2.5V,VDDQ=2.5V(Note 5)。

GND基准的PVIN、AVIN、VDD各电压-0.3 V~+6V

保存温度范围-65℃~+150℃

接合部温度150℃

SO-8热阻(θJA)151℃/W

PSOP-8热阻(θJA)43℃/W

LLP-16热阻(θJA)51℃/W

导程温度(焊接10秒)260℃

ESD耐压(Note 2)1kV

接合部位温度范围(Note 3)0℃~+125℃

GND基准的AVIN电压2.2V~5.5V

PVIN电源电压0~AVIN

SD输入电压0~AVIN

电气特性。

标准字体中记载的规格为TJ=25℃的情况,用粗体记载的限制值适合于“动作温度范围”(TJ=0°C~+125°C)

被使用(Note 4)。只要没有特别记载,AVIN=PVIN=2.5V,VDDQ=2.5V(Note 5)。

电气特性(续)

标准字体中记载的规格为TJ=25℃的情况,用粗体记载的限制值适合于“动作温度范围”(TJ=0°C~+125°C)被使用(Note 4)。只要没有特别记载,AVIN=PVIN=2.5V,VDDQ=2.5V(Note 5)。

Note 1:“绝对最大额定值”是指设备有可能破坏的极限值。“动作额定”是表示设备正确运转的条件,但在特定的不能保证性能界限。关于保证的规格及其测试条件,请参阅“电气特性”。规格的保证是表记的的测试条件。在记载的测试条件以外使设备动作的话,性能特性可能会下降。

Note 2:使用的测试电路根据人体模型,从100pF的电容器通过串联电阻1.5kΩ向各端子放电。

Note 3:在高温下,设备必须根据热阻进行延迟。SO-8包装中,没有散热片,从接合部到周围的热电阻θJA请在=151.2℃/W进行延迟。

Note 4:25℃时的极限值100%测试。所有动作温度范围内的限制值加上由统计品质管理(SQC)方式决定的修正数据,的保证。这些限制值用于计算国家半导体公司的平均出厂质量水平(AOQL)。

Note 5:VIN被定义为VIN=AVIN=PVIN。

Note 6:非动作时电流被定义为流入AVIN的电流。

Note 7:最大容许消耗功率是最大接合部温度TJ(MAX)、接合部・周围间热阻θJA、周围温度TA的函数。超过最大容许消耗功率时,凹模温度度极端上升,调节器进入热闭状态。

Note 8:VTT负荷设定使用10ms的电流脉冲测量VTT进行测试

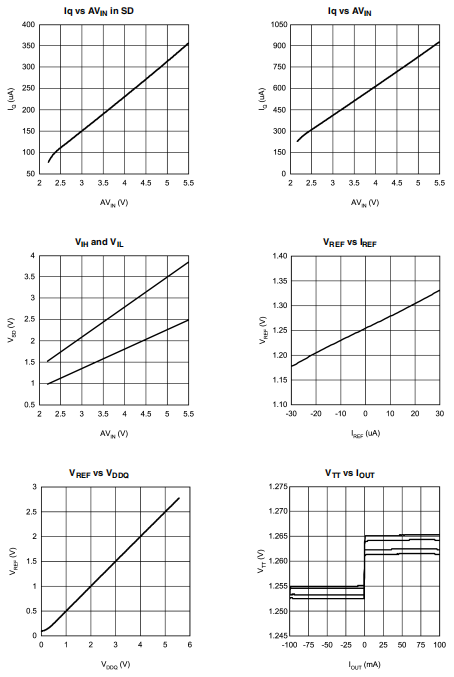

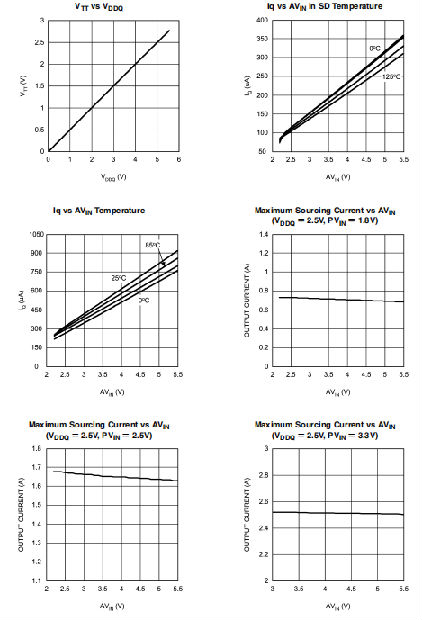

代表性的性能特性

说明

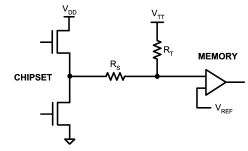

LP 2996是符合JEDEC标准的SSSTL-2规格的DDR、以及SDRAM总线、终结者的线性调整器。VTT输出得到与VDDQ/2相等的调节率电压,电流为可以选择辣酱油和辣酱油。输出级为优秀负荷设计成维持配置,产生贯穿电流被防止。另外,LP 2996是两种不同的电源线支持ru(电压)下的动作,功率输出级和模拟回可以分开路。分割电源的话,可以减少内部耗电画出来。LP 2996是下一代的DDR-SDCRAM存储器(DDR)。II)对应的终端解决方案。开小差和HSTL等不同逻辑I/F的输入发生器也可以生成电压。系列启动/终端逻辑(SSSTL)是记事本反向的为了改善传送数据时的信号质量而开发的。这个输入方式是以高频率的DDR-SDIRAM的数据在传送数据时,为了防止信号反射引起的数据错误,可以说是不可缺少的。最常见的层压电路形式是:芯片组和存储器之间设置一个串联电阻RS,并在使用一个断点电阻RT的Class II信号并行是彩灯。电路示例如Figure 1所示。

端子说明

AVIN及PVINAVIN和PVIN是LP 2996的电源端子。AVIN是全内作为部电路的电源被使用。PVIN是用于生成VTT的输出段专用电源。根据应用程序的不同,两个电源端子不同的电源使之动作也可能。接近VTT的电压场根据合RSDON的不同,输出会受到限制,但会给PVIN施加高电压。可以增加最大连续输出电流。但是,给PVIN高电压会增加内部功率损失,设计较热产生受制约的问题点。在SSSTL-2应用程序中,将AVIN和PVIN一起连接到2.5V轨道是最妥当的。无需通过短路分别绕过两个端子。作为对输入电压选择的唯一限制,PVIN在AVIN以下必须。过度的内部电力消耗导致的热限制为了防止到达,PVIN必须连接在3.3V以下的电压轨道上推荐。接合部位温度超过热阻温度。和设备在手动关机时进入相同状态,VREF保持原样,VTT为TRI-STATE。

VDDQ

VDDQ是输入,VTT的调整率所需的内部参考电用于生成压力。参考电压为2个50kΩ内置电阻抗压分压生成。由此,VTT的VDDQ/2的正确追随。请在VDD端子上接线,以实现远程感觉。代替AVIN或PVIN,将DIMM点的2.5V直接连接到VDDQ即可。这样于是,内部参照电压会影响电源布线的电压下降。不接,正确跟随DDR存储器部的电源电压。SSTL-2因为应用程序中VDDQ是2.5V,所以输入电压生成1.25V作为VTT。(VTT相对于温度的变化范围的正确值请参照“电气特性”表。VSENSE本感测端子的目的是改善远端的负荷调整。开始。在很多主板上,VTT是通过长线的连接到连字符电阻。此时,按LP 2996的输出点供电进行压感的话,由于长的线路发生的大的电压下降总线端的叠层电压比总线的其他点低。的问题。在那里把巴士中点附近的电压,改善在总线远端电压下降的问题。通过这个方法可以保持总线整体的电压良好。如果不进行远端的负荷调整,则VSNSE端子必须给予VTT。注意VSNSE信号的配线靠近ri安装时需要注意。VSNSE配线重复操作会影响VTT的正确规则的场合有合。在VSENSE端子附近的0.1μF陶瓷电容器设置SA时,会对高频信号进行滤波,因此防止误动作开始。

关闭LP 2996是将VTT输出设为TRI-STATE的有源LOW的具备关机端子。关机中VTT为AVIN的电压。将关机端子设为LOW的情况下,LP 2996待机时消耗电流会下降,而VDDQ的阻抗为为了生成内部参考电压而在100kΩ定。因此,在关机时总功率损失的计算中,考虑双方的电流(待机时消耗电流和流过VDDQ的电流)有必要。详情请参照“散热”项。由于关机端子在内部被拉上,导通时,将关机端子连接到AVIN或打开放了。

VREF

VREF是内部参照电压VDD/2的缓冲输出。正式出版力是针对北桥芯片组和存储器的参考电作为压力使用。通常那些输入的阻抗很高然后,VREF端子的电流很少。作为噪音对策如果在子附近设置旁路电容器,则可实现调节性能得到改善。推荐产品为0.1μF至0.01μF的陶瓷电容器,VREF输出支持Suspend-to-RAM功能因此,在关机和热敏关机时也激活维持状态。

VTT

VTT输出给总线的压印电阻的调节率电压力量。高精度跟随VDD/2电压,并配上电流源和电流宿的能力。LP 2996通过高速响应最大±3A的峰值电流变动有。最大连续电流是VIN的函数,是“代表性的性能特性”中记载。超过最大连续电流额定值的变动长时间如果输出电容器容量足够大因此,请防止电压过度下降。LP 2996输出虽然设计成可以承受电流的大变动,但所有的电流都可以承受。在上述条件下,很难长时间应对这种情况。理由是因为采用了小型标准包装,因为不能让由于大的内部电力损失产生的热逃跑。长度在时间上需要大电流的情况下,超过最大接合部温度需要注意不要忘记。根据热量,适当地使用额定值请降低(参阅“散热”)。接合部位温度为超过关机点后,会有褶皱VTT为TRI-STATE,直至低于点位温度。

零件的选择

输入电容器

LP 2996不需要以输入稳定为目的的输入电容器。但是在大负荷变动时防止了输入电压的降低推荐使用输入电容器。输入电容器尽量配置在PVIN附近。应用程序要求因此推荐条件不同。使用铝电解电容器的场合合,推荐容量为50μF。使用陶瓷电容器时电容在10μF左右,介质的温度特性在X 5 R以上。可以说电容器是理想的。另外,LP 2996为2.5V DC-DC如果设置在转换器的输出电容器附近,也可以省略输入电容器。两条电源线使用(AVIN和PVIN)时,请尽量靠近PVIN端子请配置47μF电容器。另外,设备上的过敏症为了防止串口,在AVIN端子处采用0.1μF陶瓷・电容器可以追加nsa。

零件的选择(继续)

输出电容器

LP 2996包括输出电容器的容量和ESR(等效串联电阻)。设计成不依赖。因此要灵活地打开电容器可以选择。输出电容器与应用程序的负荷变动请根据对VTT的响应要求来决定。DDR-SDRAM的SSL应用程序具有100μF或更高的低ESR索引。一般推荐nsa。其中ESR是预计最大功率请根据流动扣球和容许的输出电压降低来决定。输入下面对可用电容器中具有代表性的品种进行说明。开始。AL-铝电解电容器只有120Hz的阻抗需要注意的是,在高频区域中,表示特性差。LP 2996回路铝电解电容器能够适用nsa的条件是20kHz~100kHz的高频率区域但是,仅限于定义阻抗的情况。铝电。并列连接多个解电容器的话总ESR会下降。但是问题点是ESR根据温度而变化,到了低温时ESR急剧增大。

陶瓷电容器一般容量为10μF~100μF不大,ESR非常小(通常10mΩ以下)因此具有优异的噪声、旁路特性。根据使用的介电体的种类,对于电压和温度充分也有不具备上述特性的。一般来说容量小基于以上理由,陶瓷电容器采用铝电解电容器等并列连接使用。所有要使用的陶瓷电容器的介电体温度特性在X 5 R以上推荐种子。几家公司发布了采用化合物-OS-CAN(有机半导体)和SP(功能性高分子)等化合物的电容器。这些电容器在保持低ESR的同时实现了大容量现出。与其他电容器相比,虽然成本较高,可以说是在安装尺寸和性能重要的情况下最适合的解决方案。

散热

LP 2996是线性调节器,导致热的内部损失是由VTT电流产生的。最重要的是保护设备免受损坏因为不能超过大容许接合部温度,所以预计最大周根据环境温度和耗电,使设备在额定以下运转需要注意。最大容许内部温度上升(TRmax)是应用程序给出的最大环境温度(TAmax)和最根据大容许接合部温度(TJmax)计算。

根据此方程式,装置的最大功耗(PDmax)由以下方程式表示:

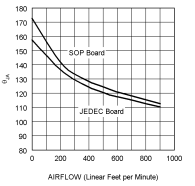

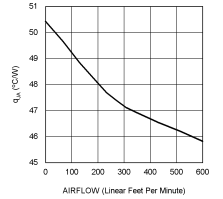

LP 2996θJA是所使用的封装、印刷基板的铜箔厚度,啤酒数量,空气流量决定。比如SO-8冰球在标准的203×102m m、铜箔厚度为35μm的基板上安装在没有空气流通的室温下消耗0.5W时的θJA,163℃/W。另外JEDEC标准的76×102m m、70μm使用厚铜箔的基板的话,θJA降低到1515.2℃/W。在Figure 2中,上述两个基板中的、相对于空气流的θJA的表示变化。

装置的安装和为了向运动场内层释放热量使用后,可以进一步改善。基板表面层即使使用厚铜箔的配线也能得到同样的效果。基板的布局设计,则Figure 2所示的标称值利率也低θJA。

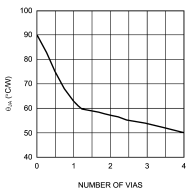

为了最大限度地引出LLP包装的输出电流,基板延迟也是非常重要的。仅仅是单纯地在DAP正下方打啤酒,可以大幅降低θJA。Figure 3为18μm/35μm/35μm/35μm/3安装在由18μm的铜箔构成的4层JEDEC基板上时是LLP包装的热特性。间距1.27mm,最大4增加到5个的时候,可以得到50.41℃/W的θJA。这个螺丝拉夫的啤酒镀金厚度为36μm。

即使给包装提供稳定的空气流量,θJA也会下降。上面在上述条件下使用2×2的通道排列时,通过气流θJA的降低如Figure 4所示。

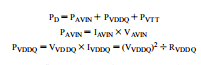

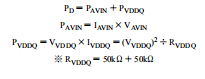

θJA进行优化,使周围温度低的基板区域如果配置LP 2996,则可以以更大的功耗使用设备。变成能。内部耗电主要不取决于信宿或信源VTT的输出电流、AVIN待机时消耗电流、VDDQ待机时消耗作为费电流等3种损失的合计被要求。在关机不是LOW的活跃状态下,内部耗电量为按以下公式计算。

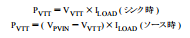

求VTT的最大功率时,电流为漏时和源时的两种状态下需要讨论VTT。但是VTT是真的因为不能同时获取克和酱两种状态,所以合计是多少仅计算一个值。

也可以计算处于关机状态的LP 2996的消耗功率。VTT输出成为TRI-STATE,漏电流和源电流都流动因此,在电力计算中去掉该项进行考虑(漏掉可以忽略电流)。关机期间,减少了的AVIN待机时消耗电流和VDDQ端子上出现的一定的IN由于会产生一些损失。

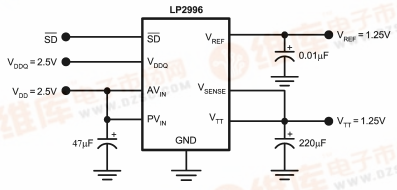

代表性的应用程序电路

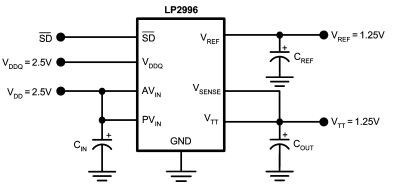

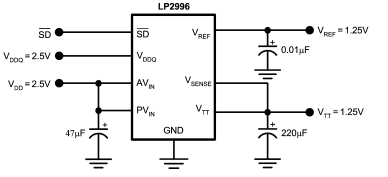

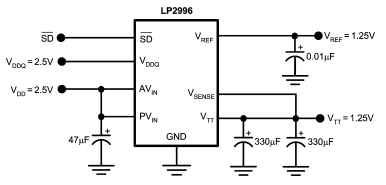

为了指示LP 2996在配置上可采取的选项,各种类型的应用驱动电路如Figure 5~14所示。各个电路的特性能是该数据表前半部分“代表性性能特性”的在图表中,根据AVIN和PVIN的电压最大输出电流如何表示是否受到影响。SSSTL-2应用程序在实现SSSTL-2填充方式的应用中,建议将所有输入轨道连接在2.5V轨道上。电力消耗、零件数量、零件选择的权衡是最合适的是的。电路示例如Figure 5所示。

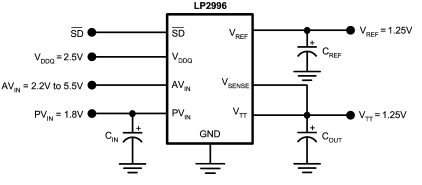

当耗电或效率成为设计上的重大课题时,通过分割电源使LP 2996动作。输出级(PVIN)为1.8V左右以2度的低电压动作,模拟电路(AVIN)为2.5V、3.3V、或给予5V等高电压。这样的话,VTT等电流供给时,也可以降低内部耗电量。这个电路的问题点是由于低电压动作,最大连续电流变小。但是,SSSTL-2应用程序的所有主板上都满了分钟。如果输出电容器变大,则会发生大的负荷电流转换可以延长对应的时间。

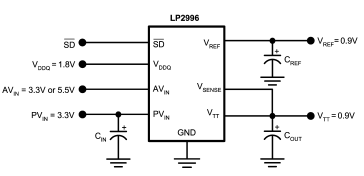

SSSTL-2应用程序的第三选项是1.8V电源轨道在不期望且使用2.5V的状态下,LP 2996的PVIN连接到3.3V轨道时。AVIN来自PVIN由于不能降低,此时AVIN为3.3V或5V轨道限制。在这个配置中,散热变大,另一方面,最大连续输出可以得到力电流。LP 2996将接合部温度超过最大额定值要注意不要变成大电流的状况。因为有这样的风险,所以在输出级上比标称3.3V高的电压不推荐。

代表性应用程序电路(续)

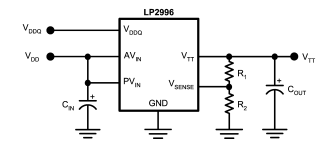

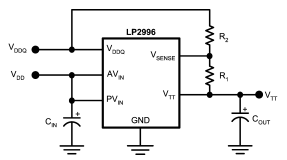

水平偏移。为了适用于SSSTL-3等SSSTL-2以外的标准,输出电压的调节与VDD的0.5倍以外的系数的情况。为了改变系数得到任意电压有几种方法。其中之一是从VTT到VSENSE端子追加反馈电阻,进行输出的水平・偏移的方法。使用该方法的电路如Figure 10、11所示。Figure 10使用2个附加电阻,从内部参照电压VDD/2也是向高电压转换的电路。VTT的正确电压是从以下公式中计算。

VTT = VDDQ/2 ( 1 + R1/R2)

相反,如果将电阻R 2置于VSENSE和VDD之间,则将VTT输出设为可以比内部参照电压VDD/2低。VTT与电阻之关工作人员用以下公式表示。VTT = VDDQ/2 (1 - R1/R2)

代表性应用程序电路(续)

HSTL应用程序

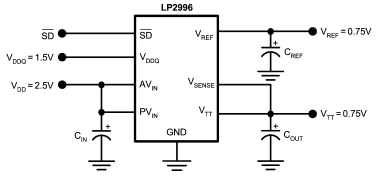

LP 2996只需在VDDDQ上连接1.5V轨道即可简单地适用于HSTL应用程序。与连字符电阻可以得到的VTT和VREF电压约为0.75V。最佳性为了获得功能,请将AVIN和PVIN连接在2.5V轨道上。

QDR应用程序的数据速率(QDR)应用程序具有较高的存储性能使用多个通道获得。因此,总线信号线数量增加,层压所需的电流电平也变大。因此,在终端中,对于多个信道的每个信道单独地的LP 2996。简化基板布局可以控制各个调节器的内部耗电量。各规则向各DIMM银行提供从比较器输出的各个VREF信号开始。芯片组用的参照电压,局部性地进行电阻分压从LP 2996中的一个开始提供。VREF追加到VTT由于设备之间的偏差较小,各LP 2996的基准电压差很少。输出电容器的选择将LP 2996用于SSSTL-2I/O信号的输入的应用在外壳中,将Figure 13所示的代表性应用电路适用。

该电路以最小的基板面积和最小的部件数量进行终结者。实现了电路。应选择电容器的容量为根据断字信号线的数量和最大负载电流而不同但是,VTT用长线分配的主板和应用软件在电路中,使用多个体电容器并且进一步进行高频解希望追加耦合电容器。下一个Figure在14中,将两个体输出电容器作为最佳位置的VTT显示层两端配置的电路示例。ESR小且成本低使用低容量铝电解电容器。

在一般的PC应用程序中,模块中实现的DDR恢复;由于SDRAM DIMM产生长的互连,所以多个的颓废。因此,通常1000μF的容量范围使用周围的铝电解电容器作为散装电容器。

PCB设计的考虑

1.电源轨的输入电容器尽可能将PVIN端子的请放在附近。

2.VSENSE端子上的VTT层压总线的调压请连接到需要启动的点。主板应用程序在的话,最理想的是终点站巴士的中点。

3.VDDQ输入针对DIMM或芯片组的VDDQ电源以实现远程感觉的方式连接。内部参考电可以最高精度地生成压力。

4.为了改善热特性,为了增加封装的散热量请把表层的铜箔放大。地线和内部格连接圆形平面的多个通道也有助于散热。宽度等,如果作为制造基准被容许的话,请放在底部。

5.在VSENSE信号的配线设计中,根据切换的I/O信号需要注意不要捡到噪音。VSNSE端子附近如果在0.1μF设置陶瓷电容器,则不理想的高频信号选项卡。VSNSE配线较长时,特别是需要研究。

6.VREF为了改善常规性能,0.1μF~0.01μF的陶瓷电容器,请绕过噪声。好的。电容器尽可能靠近VREF端子。