bq2022A点击型号即可查看芯片规格书

特点

•1024位一次性可编程(OTP)EPROM,用于存储用户可编程配置数据

•工厂编程的唯一64位识别号

•减少电路板布线的单线接口

•同步通信减少主机中断开销

•15KV IEC 61000-4-2数据引脚的ESD合规性

•无需备用电源

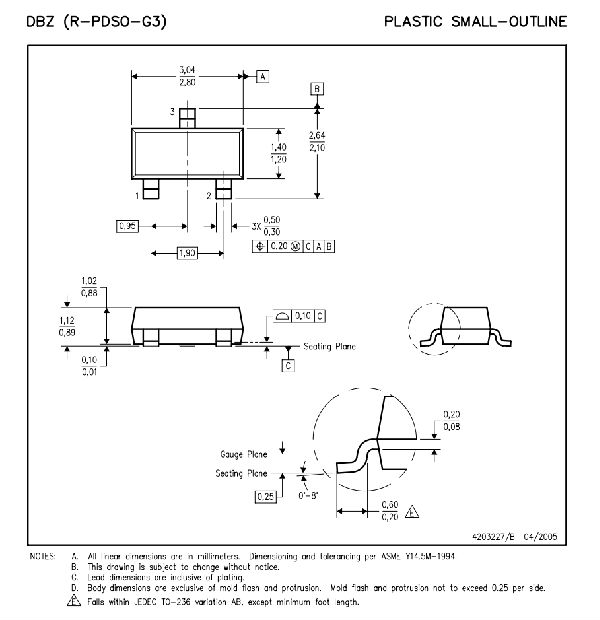

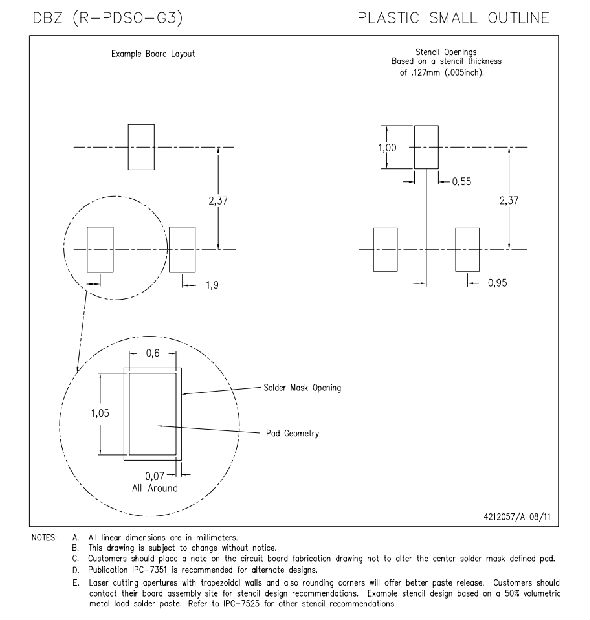

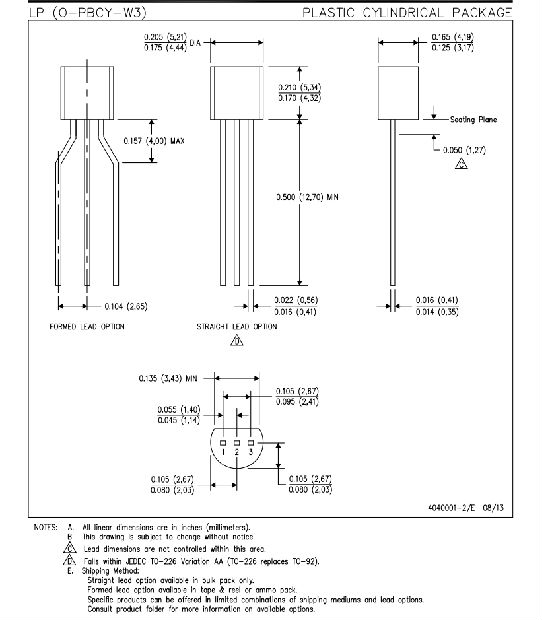

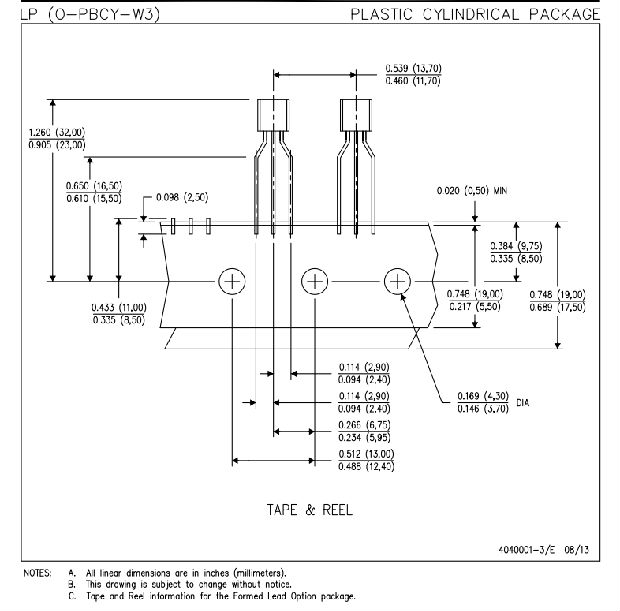

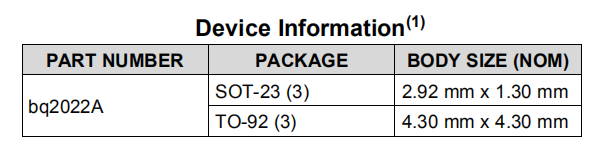

•提供3针SOT-23和TO-92封装

应用

•安全编码

•库存跟踪

•产品修订维护

•电池组标识

说明

bq2022A是1K位串行EPROM,包含工厂编程的唯一48位标识号、8位CRC生成和8位系列代码(09h)。64位状态寄存器控制写保护和页面重定向。

bq2022A SDQ™ 接口只需要一个连接和一个接地回路。数据管脚也是bq2022A的唯一电源。

小型表面贴装封装方案节省了印刷电路板空间,而低成本使其成为电池组等应用的理想选择配置参数、记录维护、资产跟踪、产品修订状态和访问代码安全性。

(1)、有关所有可用的软件包,请参阅数据表末尾的可订购附录。

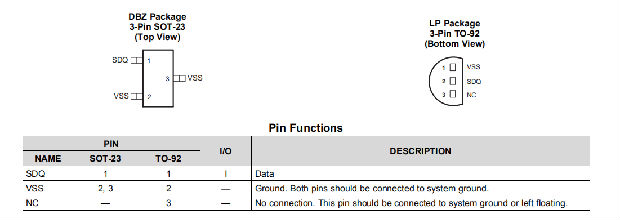

针配置和功能

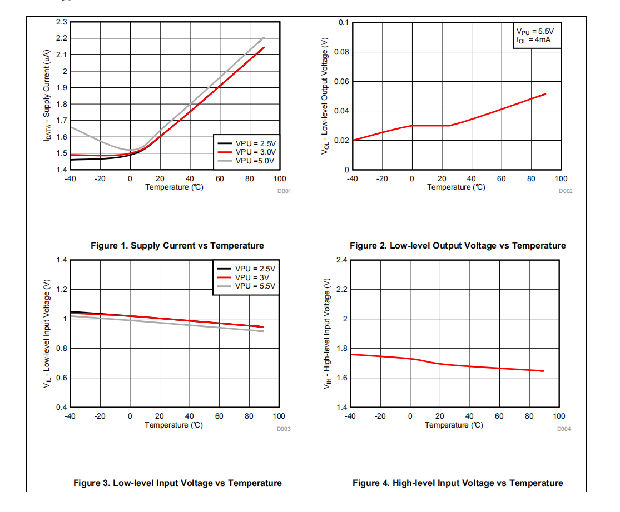

典型特征

详细说明

概述

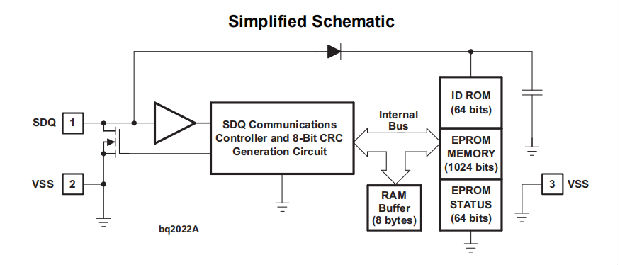

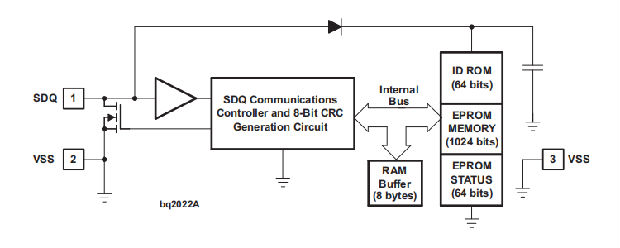

功能框图显示了bq2022A的主要控制和存储器部分之间的关系。bq2022A有三个主要数据组件:64位工厂编程ROM,包括8位系列代码、48位标识号和8位CRC值、1024位EPROM和EPROM状态字节。读写操作的电源来自数据管脚。内部电容器在信号线处于高位时存储能量,并在数据管脚处于低位时释放能量,直到管脚返回高位以补充电容器上的电荷。可以读取特殊制造商的程序配置文件字节,以确定编程部件所需的编程配置文件。

功能框图

特征描述

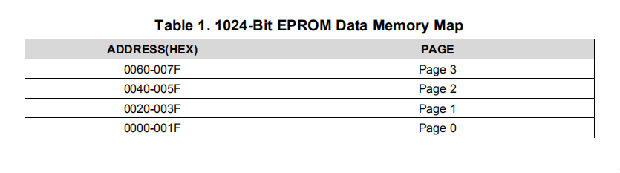

1024位EPROM

表1是bq2022A的1024位EPROM部分的内存映射,配置为4页,每页32字节。8字节RAM缓冲区是在对存储器编程时使用的附加寄存器。数据首先被写入RAM缓冲区,然后通过从bq2022A读取8位CRC来验证,该CRC确认数据的正确接收。如果缓冲区内容正确,则发出编程命令,并将8字节的数据段写入存储器中选定的地址。这个过程确保了存储器编程时的数据完整性。读取和编程bq2022A的1024位EPROM部分的详细信息见本数据表的存储器/状态功能命令部分。

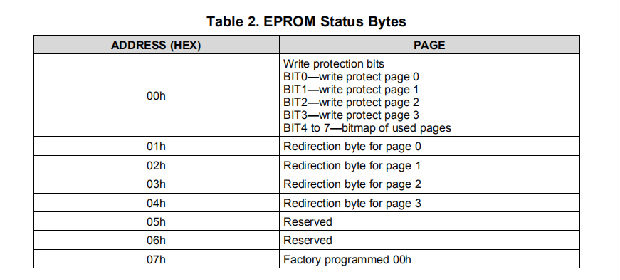

EPROM状态存储器

除了可编程的1024位存储器外,还有包含在EPROM状态存储器中的64位状态信息。状态存储器可通过单独的命令访问。状态位是EPROM,被读取或编程以指示询问bq2022A的软件的各种条件。状态存储器的第一个字节包含写保护页位,如果对适当的写保护位进行编程,则在1024位主存储器区域中禁止对相应页进行编程。一旦在写保护页字节中编程了一个位,与该位对应的整个32字节页就不能再被更改,但仍可以被读取。可以使用write STATUS命令清除写保护位。

EPROM状态存储器的下四个字节包含页地址重定向字节。EPROM状态字节中的位可以向主机指示用适当的重定向字节替换页面的页面。bq2022A的硬件不根据页面地址重定向字节的内容做出决定。此功能允许用户的软件通过指示一个或多个特定页面应替换为页面地址重定向字节中指示的页面,对EPROM进行数据修补。新页地址的一个补码写入对应于原始(替换)页的页地址重定向字节。如果页地址重定向字节具有FFh值,则主内存中与该页对应的数据有效。如果页地址重定向字节有其他十六进制值,则与该重定向字节对应的页中的数据无效,现在可以在存储在关联页地址重定向字节中的十六进制值所指示的页地址的补码处找到有效数据。例如,重定向字节中的FDh值表示更新的数据现在位于第2页。读取和编程bq2022A的EPROM状态存储器部分的细节在存储器/状态功能命令部分给出。

错误检查

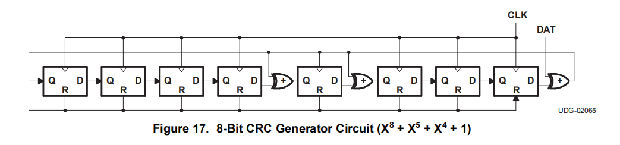

为了验证从bq2022A发送的数据,主机在接收数据时从数据中生成CRC值。将生成的值与bq2022A发送的CRC值进行比较。如果两个CRC值匹配,则传输无错误。这个CRC的等价多项式函数是X8+X5+X4+1。详细信息见本数据表的CRC生成部分。

定制bq2022A

64位ID标识每个bq2022A。48位序列号是唯一的,由德州仪器编程。默认的8位系列代码是09h;但是,可以根据单个客户保留不同的值。有关更多信息,请联系您的德州仪器销售代表。

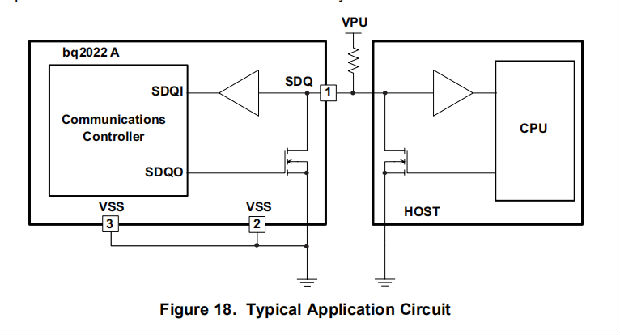

总线终端

由于bq2022A的驱动输出是一个开漏N沟道MOSFET,因此主机必须提供源电流或5-kΩ外部上拉,如图18中的典型应用电路所示。

设备功能模式

在SDQ通信期间或SDQ保持在有效VPU电压时,设备处于激活模式。

编程

串行通信

主机通过SDQ接口的命令结构读取、编程或检查bq2022A的状态。

初始化

初始化由两个脉冲组成,复位脉冲和存在脉冲。主机产生复位脉冲,而bq2022A用存在脉冲响应。主机通过将数据总线低驱动至少480μs来重置bq2022A。有关更多详细信息,请参阅重置和状态脉冲部分。

ROM命令

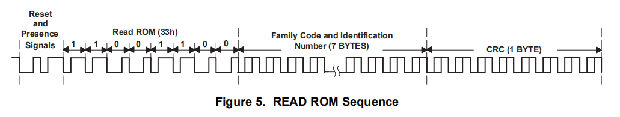

读取ROM命令

读取ROM命令序列是允许主机读取8位系列代码和48位标识号的最快序列。读取ROM序列从主机产生至少480μs的复位脉冲开始。bq2022A以存在脉冲响应。接下来,主机继续发出读取ROM命令33h,然后在数据帧期间使用读取信令(参见读取和写入信号部分)读取ROM和CRC字节。

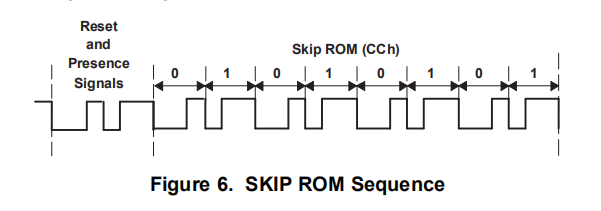

跳过ROM命令

这个SKIP ROM命令CCh允许主机访问内存/状态功能。SKIP ROM命令后面是memory/status functions命令。

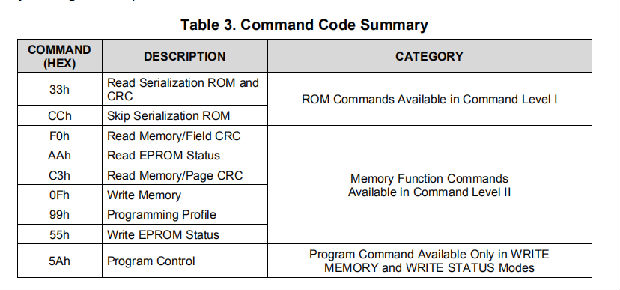

存储器/状态功能命令

六个存储器/状态功能命令允许读取和修改1024位EPROM数据存储器或64位EPROM状态存储器。有两种类型的读存储器命令,加上写存储器、读状态和写状态命令。此外,该部件响应程序配置文件字节命令。bq2022A仅在部件发出跳过ROM命令后才响应存储器/状态功能命令。

读取存储器命令

bq2022A上有两个读取内存命令。两个命令都用于从1024位EPROM数据字段读取数据。它们是读存储器/页CRC和读存储器/字段CRC命令。读存储器/页CRC在任何32字节页边界的末端生成CRC,而读存储器/字段CRC在到达1024位数据存储器的末端时生成CRC。

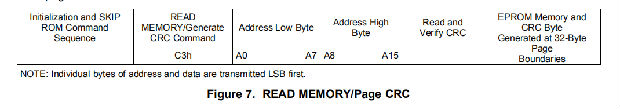

读存储器/页CRC

为了在bq2022A的32字节页边界处读取存储器并生成CRC,SKIP ROM命令后跟读取存储器/生成CRC命令C3h,接着是地址低字节,然后是地址高字节。

bq2022A计算命令字节和地址字节的8位CRC,并由主机读回,以确认接收到正确的命令字和起始地址。如果主机读取的CRC不正确,则必须发出重置脉冲,并且必须重复整个序列。如果主机接收到的CRC是正确的,则主机发出读取时隙,并从bq2022A接收数据,从初始地址开始,一直持续到32字节的页面结束。此时,主机发送8个额外的读取时隙,并接收8位CRC,这是将所有数据字节从当前页的初始起始字节移到最后一个字节的CRC生成器的结果。一旦接收到8位CRC,从下一页开始再次从1024位EPROM数据字段读取数据。这个序列一直持续到主机读取最后一页及其附带的CRC为止。因此,每一页数据可以被认为是33字节长,32字节用户编程的EPROM数据和8位CRC,在每一页结束时自动生成。

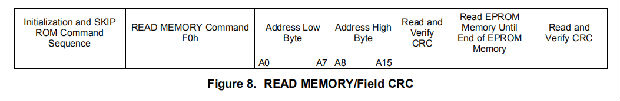

7.5.5.2读取存储器/现场CRC

为了在32字节的页面边界上读取没有CRC生成的内存,SKIP ROM命令后面跟着read memory命令F0h,后面跟着address low字节,然后是address high字节。

注意:如图8所示,地址和数据的单个字节首先被LSB发送。

bq2022A计算命令字节和地址字节的8位CRC,并由主机读回,以确认接收到正确的命令字和起始地址。如果主机读取的CRC不正确,则必须发出重置脉冲,并且必须重复整个序列。如果主机接收到的CRC是正确的,则主机发出读取时隙并从bq2022A接收数据,从初始地址开始并一直持续到到达1024位数据字段的末尾或直到发出复位脉冲。如果读取发生在存储器空间的末端,则主机可以发出八个额外的读取时隙,并且bq2022A用从存储器的初始起始字节到最后一个字节读取的所有数据字节的8位CRC来响应。在主机接收到CRC之后,在发出复位脉冲之前,任何随后的读取时隙都显示为逻辑1。在到达存储器末端之前由复位脉冲结束的任何读取都没有8位CRC可用。

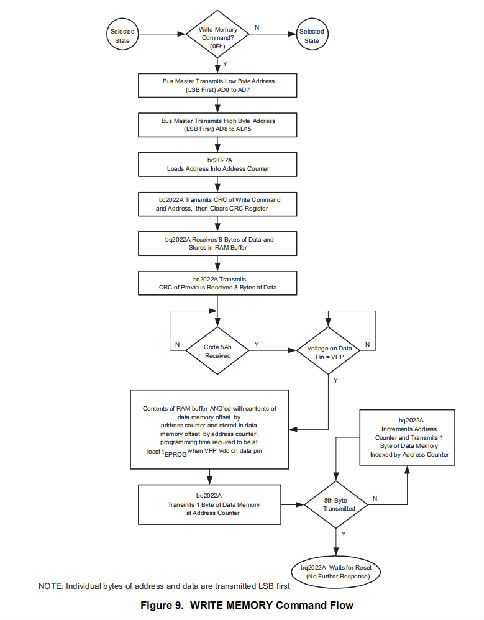

写入存储器命令

WRITE MEMORY命令用于对1024位EPROM内存字段进行编程。1024位内存字段以8字节段编程。数据首先一次写入一个8字节的RAM缓冲区。然后,当发出编程命令时,RAM缓冲区的内容与EPROM存储器字段的内容相加。

图9说明了为EPROM内存字段编程的事件序列。发出SKIP ROM命令后,主机发出写内存命令0Fh,后跟起始地址的低字节和高字节。bq2022A基于写入命令和地址计算并发送8位CRC。

如果在写入存储器过程中的任何时候,主机读取的CRC不正确,则必须发出复位脉冲,并且必须重复整个序列。

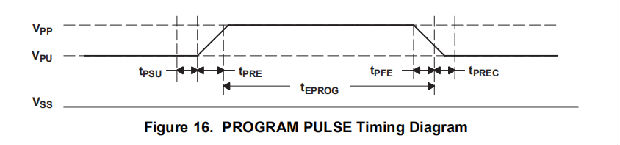

bq2022A发送CRC后,主机再向bq2022A发送8字节的数据,再根据8字节的数据计算并发送8位CRC。如果该CRC与主机计算的CRC一致,则主机发送程序命令5Ah,然后施加编程电压至少2500μs或tEPROG。然后,RAM缓冲区的内容与起始地址偏移的8字节EPROM的内容进行逻辑和运算。

起始地址可以是0000到007F(十六进制)之间的8的任意整数倍,例如0000、0008和0010(十六进制)。

写入数据存储器命令序列可以通过发出复位脉冲在任何点终止,除了在程序脉冲周期tPROG期间。

注意:bq2022A首先响应来自所选EPROM地址的最低有效位的数据。应检查此响应以验证编程字节。如果编程字节不正确,则主机必须重置部件并重新开始写入序列。

对于这两种情况,继续编程的决定完全由主机作出,因为bq2022A无法确定由主机计算的8位CRC是否与由bq2022A计算的8位CRC一致。

在编程之前,1024位EPROM数据字段中的位显示为逻辑1。

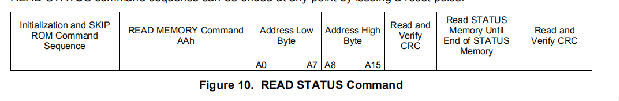

读取状态命令

READ STATUS命令用于从EPROM STATUS data字段读取数据。发出SKIP ROM命令后,主机发出READ STATUS命令AAh,然后是address low字节,然后是address high字节。

注意:bq2022A计算命令字节和地址字节的8位CRC,并由主机读回,以确认接收到正确的命令字和起始地址。

如果主机读取的CRC不正确,则必须发出重置脉冲,并且必须重复整个序列。如果主机接收到的CRC是正确的,则主机发出读取时隙并从bq2022A接收数据,从所提供的地址开始并一直持续到到达EPROM状态数据字段的末尾。此时,主机接收到8位CRC,这是将所有数据字节从初始起始字节移到包含00h值的最终工厂编程字节的CRC生成器的结果。

之所以提供此功能,是因为EPROM状态信息可能随着时间的推移而改变,使得不可能对数据编程一次,并且包括始终有效的伴随CRC。因此,READ status命令提供基于(并且始终与)存储在EPROM status data字段中的当前数据一致的8位CRC。

读取8位CRC后,主机从bq2022A接收逻辑1s,直到发出复位脉冲。读取状态命令序列可以通过发出复位脉冲在任何点结束。

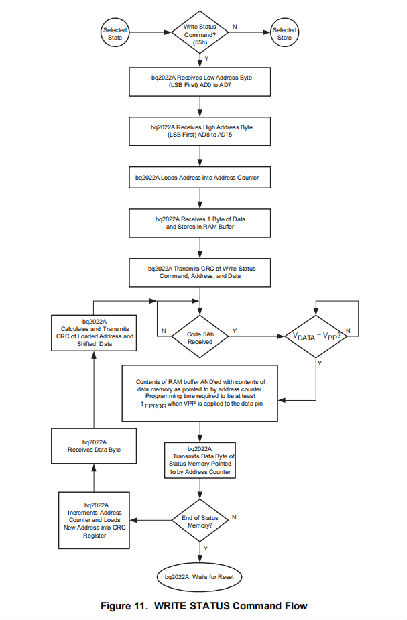

写入状态命令

写入状态命令用于在发出bq2022A跳过ROM命令后对EPROM状态数据字段进行编程。

图11中的流程图说明主机发出写状态命令55h,然后是地址低字节,然后是地址高字节,最后是要编程的数据字节。

注意:地址和数据的单个字节首先被LSB传输。命令字节、地址字节和数据字节的8位CRC由bq2022A计算并由主机读回,以确认接收到正确的命令字、起始地址和数据字节。

如果主机读取的CRC不正确,则必须发出重置脉冲,并且必须重复整个序列。如果主机接收到的CRC正确,则发出程序命令(5Ah)。在发出程序命令后,再向数据管脚施加程序电压VPP,用于周期tPROG。在编程之前,EPROM状态数据字段的前七个字节显示为逻辑1。对于主机提供的数据字节中设置为逻辑0的每一位,在字节位置应用编程脉冲后,EPROM状态数据字段所选字节中的相应位编程为逻辑0。EPROM状态字节数据字段的第八个字节在工厂编程为包含00h。

在应用编程脉冲并且数据线返回到VPU之后,主机发出八个读时隙来验证是否已对适当的位进行了编程。bq2022A首先用来自所选EPROM状态地址的数据发送最低有效位来响应。应检查此响应以验证编程字节。如果编程字节不正确,则主机必须重置设备并重新开始写入序列。如果bq2022A EPROM数据字节编程成功,bq2022A会自动递增其地址计数器,以在状态存储器数据字段中选择下一个字节。新的双字节地址的最低有效字节也作为起始值加载到8位CRC生成器中。主机使用八个写时隙发出下一个字节的数据。

当bq2022A将该字节的数据接收到RAM缓冲器中时,它还将数据转移到CRC生成器中,该CRC生成器已预先加载了当前地址的LSB,结果是新数据字节的8位CRC和新地址的LSB。在提供数据字节之后,主机从具有八个读取时隙的bq2022A读取这个8位CRC,以确认地址正确递增并且数据字节被正确接收。如果CRC不正确,则必须发出复位脉冲,并重新启动写入状态命令序列。如果CRC正确,则主机发出编程脉冲,并对存储器中选定的字节进行编程。

注意:写入状态命令的初始写入,生成一个8位CRC值,该值是将命令字节移位到CRC生成器中,然后是两个地址字节,最后是数据字节的结果。由于bq2022A自动递增其地址计数器,在该写入状态命令中的后续写入将生成8位CRC,这是将新(递增)地址的LSB加载(不移位)到CRC生成器中,然后再移位到新数据字节中的结果。

对于这两种情况,继续对EPROM状态寄存器进行编程的决定完全由主机做出,因为bq2022A无法确定主机计算的8位CRC是否与bq2022A计算的8位CRC一致。如果忽略错误的CRC并且主机应用程序脉冲,在bq2022A中可能会出现不正确的编程。还要注意,bq2022A总是在接收到用于确认所选EPROM字节编程的八个读取时隙后,递增其内部地址计数器。继续的决定再次完全由主机做出,因此,如果EPROM数据字节与提供的数据字节不匹配,但主机继续执行写状态命令,则可能在bq2022A内发生不正确的编程。可以通过发出复位脉冲在任何点结束写状态命令序列。

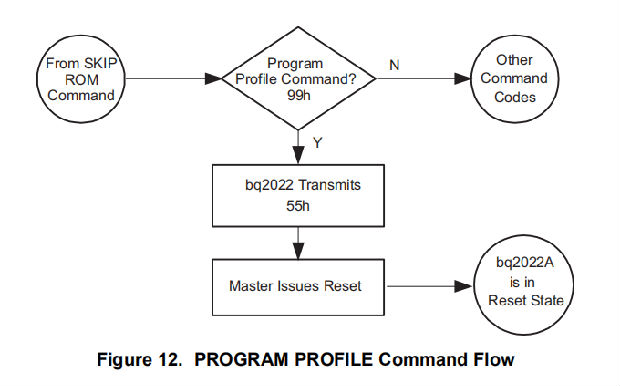

程序配置文件字节

读取程序配置文件字节,以确定特定制造商所需的写存储器编程序列。发出ROM命令后,主机发出PROGRAM PROFILE BYTE命令99h。图12显示bq2022A以55h响应。这将通知主机,写入内存编程序列是本数据表的写入内存命令部分中描述的序列。

SDQ信令

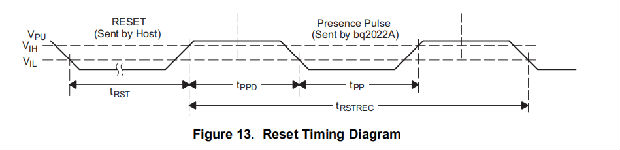

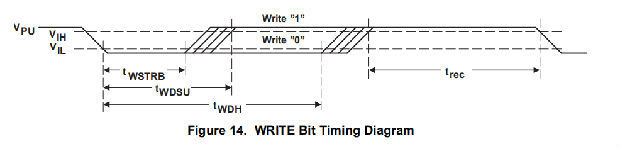

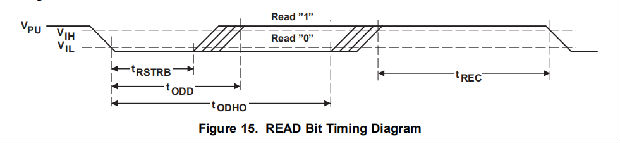

所有SDQ信令都从初始化设备开始,然后由主机驱动总线低位以写入1或0,或开始读取位的开始帧。图13显示了初始化计时,而图14和图15显示主机通过在启动周期tWSTRB/tRSTRB中驱动数据总线低位来启动每个位。该位启动后,主机在写入期间继续控制总线,或者bq2022A在读取期间响应。

复位和存在脉冲

如果数据总线被低驱动超过120μs,则bq2022A可以被重置。图13显示,如果数据总线被低驱动超过480μs,则bq2022A复位,并通过对存在脉冲的响应指示它准备就绪。

写入位

图14中的写入位时序图显示,主机通过发出位的tWSTRB部分,然后驱动数据总线低电平进行写入0,或释放数据总线进行写入1来启动传输。

读取位

图15中的读取位时序图显示主机通过发出位的tRSTRB部分来启动位的传输。然后,bq2022A通过驱动数据总线低以发送读取0或释放数据总线以发送读取1来响应。

程序脉冲

IDLE

如果总线处于高位,则总线处于空闲状态。总线事务可以通过让数据总线处于空闲状态而暂停。总线事务可以随时从空闲状态恢复。

CRC生成

bq2022A有一个8位CRC,存储在64位ROM的最高有效字节中。总线主控可以从64位ROM的前56位计算一个CRC值,并将其与bq2022A中存储的值进行比较,以确定总线主控是否已无错误地接收到ROM数据。该CRC的等价多项式函数为:X8+X5+X4+1。

在某些情况下,bq2022A还使用刚才显示的相同多项式函数生成一个8位CRC值,并将该值提供给总线主机,以验证从总线主机到bq2022A的命令、地址和数据字节的传输。bq2022A为写入存储器和写入状态命令,然后将该值输出到总线主控,以确认正确传输。类似地,bq2022A为从总线主机接收的用于读取存储器、读取状态和读取数据的命令和地址字节计算8位CRC/生成8位CRC命令以确认这些字节已被正确接收。在读取数据/生成8位CRC命令期间,来自1024位EPROM的每页数据被发送到总线主设备时,bq2022A上的CRC生成器还用于提供无错误数据传输的验证,以及用于状态存储器字段中的8字节信息的验证。

在使用CRC进行数据传输验证的每一种情况下,总线主节点必须使用先前给出的多项式函数计算CRC值,并将计算值与存储在bq2022A的64位ROM部分(用于ROM读取)中的8位CRC值或bq2022A内计算的8位CRC值进行比较CRC值和继续操作的决定完全由总线主机决定。如果存储在bq2022A中或由bq2022A计算的CRC与总线主节点生成的值不匹配,bq2022A上的任何电路都不会阻止命令序列继续进行。正确使用CRC可以产生具有高完整性的通信信道。

应用与实施

注意:以下应用程序部分中的信息不属于TI组件规范的一部分,TI不保证其准确性或完整性。TI的客户负责确定部件是否适合其用途。客户应验证和测试其设计实现,以确认系统功能。

申请信息

典型的应用包括被配置为SDQ通信主机设备的微控制器和作为SDQ从设备的bq2022A。主机和从机具有开漏功能,为此需要一个上拉电阻器(通常为10 kΩ)连接到2.65 V至5.5 V范围内的上拉电压。

典型应用

SDQ线路不需要额外电容,可能导致通信故障。

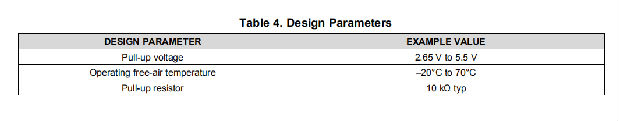

设计要求

详细设计程序

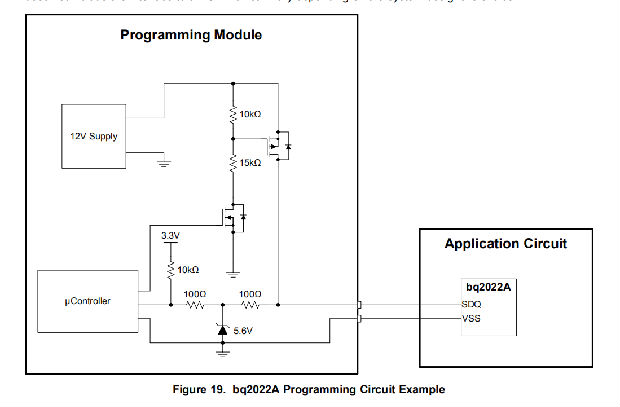

编程电路示例

bq2022A需要12伏最大脉冲信号来编程OTP存储器。有必要为生产设置编程测试。图19显示了这种设置的电路可能是什么的示例。编程模块包含作为SDQ主机的微控制器,并控制编程脉冲的时间和宽度。12伏电源是编程脉冲的电源。只有SDQ和VSS信号需要退出测试设置,因为包含被测bq2022A的应用电路仅连接用于编程和验证数据。

编程模块通常使用USB接口连接到PC。图19中的图表不包括与PC机的接口,该接口可以根据系统设计者的选择而变化。

SDQ主最佳实践

可能需要在主机系统上“bit bang”一个GPIO来充当SDQ主机。在这种情况下,应该在用于重置bq2022A的代码中内置一些额外的错误检查,以确保从机在总线上按预期运行。

每当主机发送复位时,bq2022A以存在脉冲响应。在出现脉冲之前,主机应确认总线已被释放并返回到高电平,这表示没有任何东西使总线处于意外的低电平。由于最小tppd为15微秒,在复位结束时释放总线后,让主机在总线上寻找10微秒高的逻辑足以确认总线被释放,以便bq2022A响应。

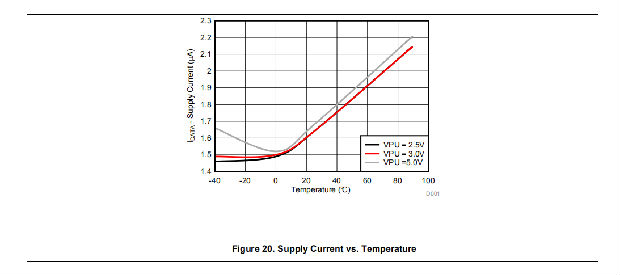

应用曲线

电源建议

bq2022A是一种低功耗设备,只需要在通信时打开。设备电源来自系统中用于数字I/O的电压源。不需要电源输入旁路电容器的设备中不存在专用VCC管脚。设备从SDQ通信输入获得功率,SDQ通信输入可在正常通信活动期间维持。

由于来自电源的电流限制,SDQ电压在最初通电时的斜坡时间可能很慢。斜坡时间大于200微秒可能会导致POR电路的意外反弹,并导致设备不产生存在脉冲。为了解释这种对设备的不希望的影响,通信主机的最佳实践是通过下拉SDQ线超过5 ms,然后在发出大约480μs长的复位脉冲之前释放SDQ总线,向设备发出“硬”复位。

图21说明了处理初始上电坡道的最佳实践,如图(1)所示,该坡道可能持续时间较长。主机应发出大于5 ms的“硬”复位(2),复位设备并产生存在延迟和存在脉冲(3)。之后,可应用约480微秒的“软”复位,(4),其还产生高存在延迟和低存在脉冲(5)。

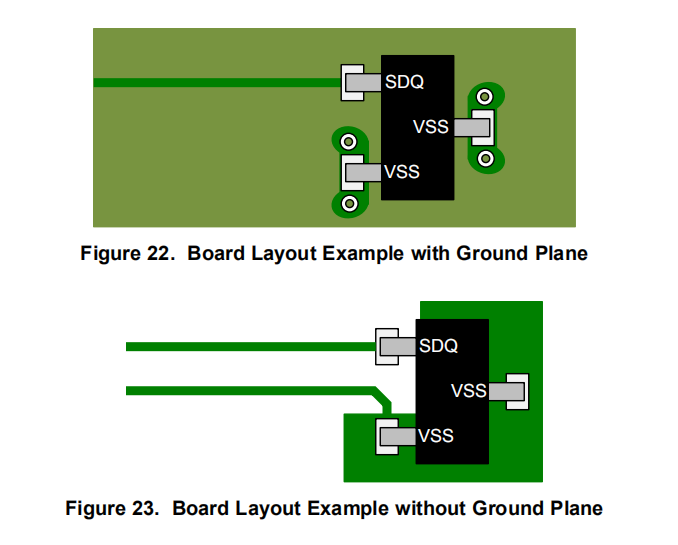

布局

布局指南

bq2022A只有一个信号(SDQ)。最佳实践是将信号跟踪直接从bq2022A的SDQ引脚路由到应用系统的外部连接器或主机SDQ主设备。信号轨迹应使用平行接地平面适当屏蔽。如果可能的话,使用每个VSS引脚的两个通孔到达接地层图22。如果一个完整的接地平面对bq2022A不可用,那么尝试将两个VSS引脚连接到一个围绕大部分设备的大轨迹上,并留下一个与SDQ引脚相邻的VSS引脚的轨迹,以便它沿着SDQ轨迹返回到SDQ主接口引脚图23。

布局示例

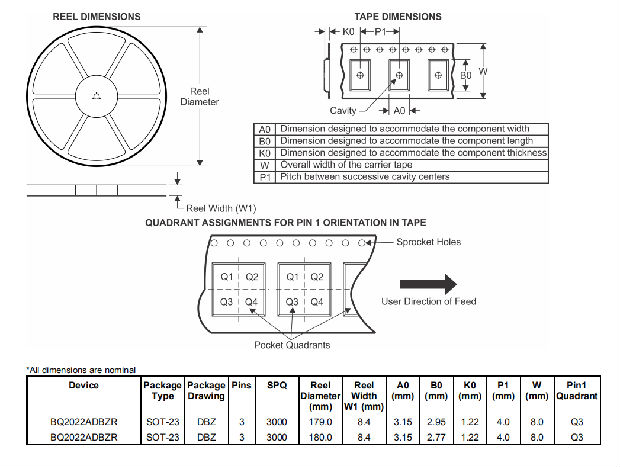

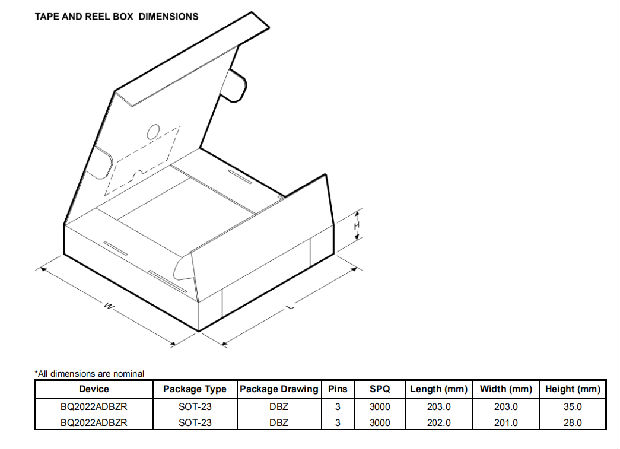

包装材料信息