AD7401A点击型号即可查看芯片规格书

AD7400A点击型号即可查看芯片规格书

特征

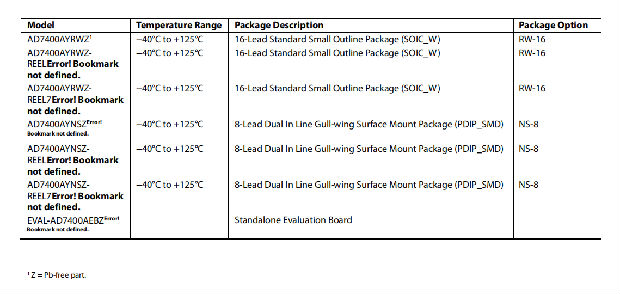

10兆赫时钟速率;二阶调制器;16位无漏码;16位时典型的±2 LSB输入;3.5微伏/摄氏度最大偏移漂移;车载数字隔离器;车载参考;低功率运行:5.25 V时最大18毫安;-40°C至+125°C工作范围;16铅SOIC,8铅鸥翼面贴装DIP封装;AD7401A,外部时钟版本安全和监管批准;UL认可;3750 V rms,每UL 1577 1分钟;CSA部件验收通知#5A;VDE合格证书;德国工业标准EN 60747-5-2(VDE 0884第2部分):2003-01;德国工业标准EN 60950(VDE 0805):2001-12;欧洲工业标准EN 60950:2000;VIORM=891V峰值。

应用

*交流电机控制

*数据采集系统

*A/D+光隔离器的更换。

一般说明

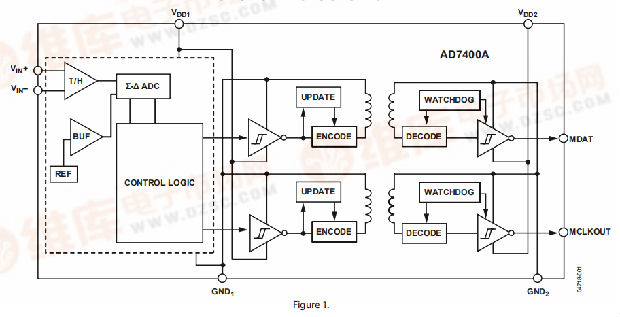

AD7400A1是一个二阶∑-Δ调制器,它将模拟输入信号转换为高速、1位数据流,并基于analog Devices,Inc.iCoupler®技术进行片上数字隔离。AD7400A通过5 V电源工作,并接受±200 mV的差分输入信号(±320 mV满刻度)。模拟量输入由模拟调制器连续采样,无需外部采样和保持电路。输入信息以数据速率为10mhz的密度包含在输出流中。利用适当的数字滤波器可以重建原始信息。串行I/O可以使用5 V或3 V电源(VDD2)。

串行接口被数字隔离。高速CMOS与单片空芯变压器技术相结合,意味着片上隔离提供了优于光耦器件等替代器件的优异性能。该部分包含一个片上参考。AD7400A采用16导SOIC和8导鸥翼面贴装式倾角,工作温度范围为-40°C至+125°C。

功能框图

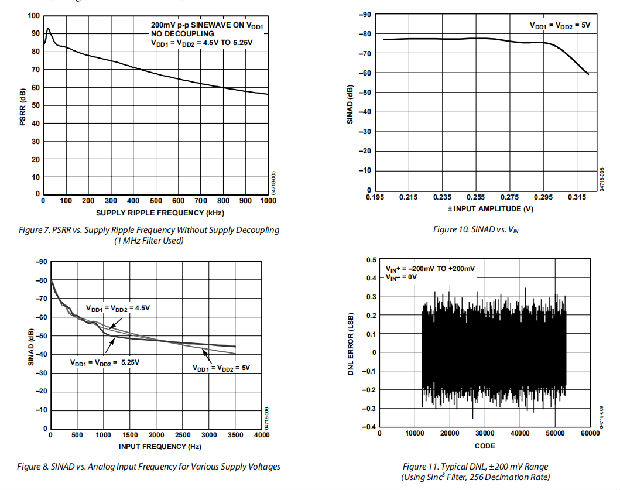

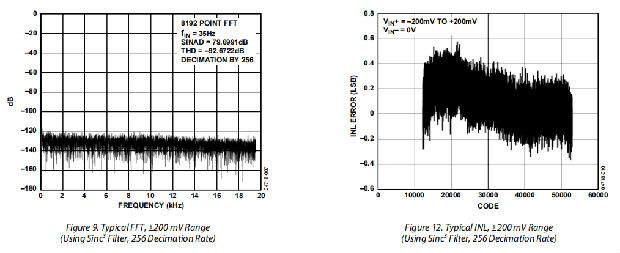

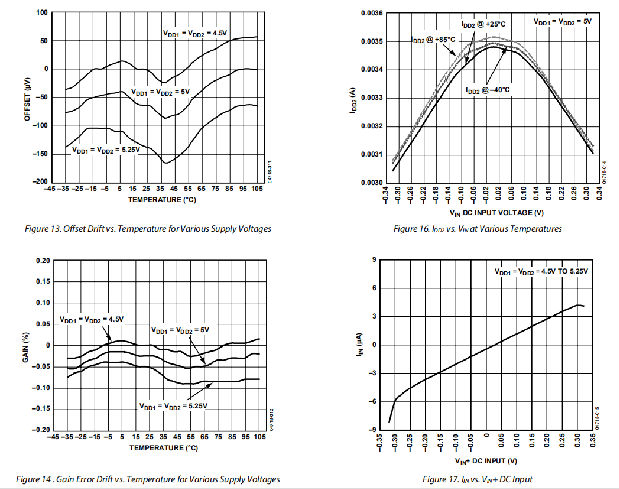

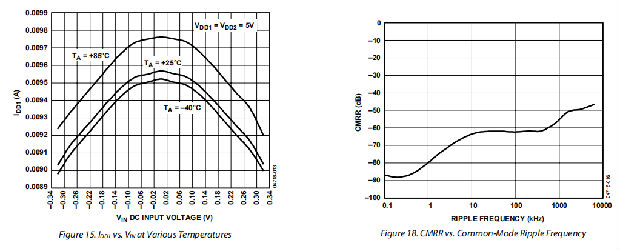

典型性能特征

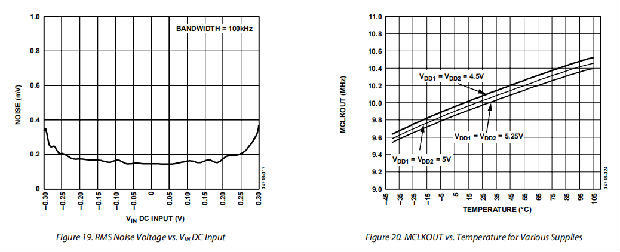

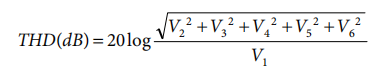

T=25°C,使用20 kHz砖墙滤波器,除非另有说明。

术语

微分非线性

差分非线性是ADC中任意两个相邻码的测量值与理想1 LSB变化之间的差值。

积分非线性

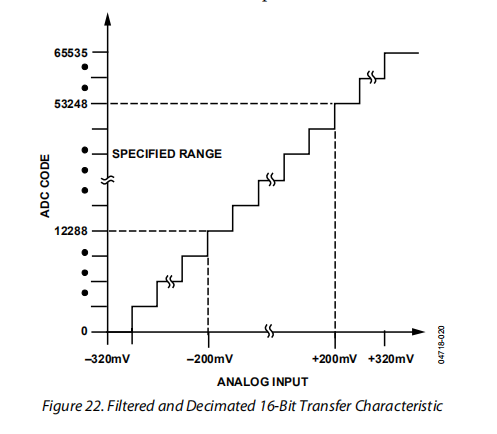

积分非线性是通过ADC传递函数端点的直线的最大偏差。传输函数的端点指定为负满标度、-200 mV(VIN+-VIN-)、16位电平的代码12288和指定的正满标度、+200 mV(VIN+-VIN-)、16位电平的代码53248。

偏移误差

偏移量是中刻度代码(16位级别的代码32768)与理想的车辆识别号+车辆识别号-(即0伏)之间的偏差。

增益误差

这包括正满标度增益误差和负满标度增益误差。正满标度增益误差是指调整偏移误差后,指定的正满标度代码(16位级别为53248)与理想的车辆识别号+-车辆识别号-(+200毫伏)之间的偏差。负满标度增益误差是补偿误差调整后,指定的负满标度代码(16位级别为12288)与理想的车辆识别号+车辆识别号-(-200毫伏)之间的偏差。增益误差包括参考误差。

信噪比(SINAD)

这个比率是在ADC输出端测得的信号与(噪声+失真)的比率。信号是基波的均方根振幅。噪声是所有非基本信号的总和,最多为采样频率(fS/2)的一半,不包括直流电。该比率取决于数字化过程中量化级别的数目;级别越多,量化噪声越小。一个理想的N位正弦波输入转换器的理论信噪比由下式给出:

信号到-(噪声+失真)=(6.02N+1.76)dB

因此,对于12位转换器,这是74分贝。

有效位数(ENOB)

ENOB的定义是:

ENOB=(SINAD–-1.76)/6.02

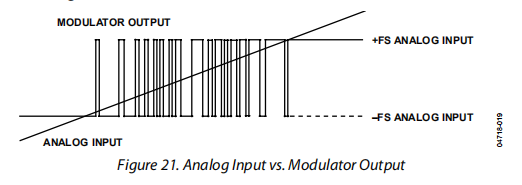

总谐波失真(THD)

THD是谐波的均方根和与基波的比值。对于AD7400A,定义为:

其中:V1是基波的均方根振幅。

V2、V3、V4、V5和V6是第二次谐波至第六次谐波的均方根振幅。

峰值谐波或杂散噪声

峰值谐波或杂散噪声定义为ADC输出频谱中下一个最大分量(不包括直流电)的均方根值与基波的均方根值之比。通常,本规范的值由频谱中的最大谐波确定,但对于谐波埋在噪声层中的adc,它是噪声峰值。

共模抑制比

共模抑制比是指在±200 mV频率f下,ADC输出功率与施加在频率f的共模电压V+和V-上的200 mV p-p正弦波功率之比:

CMRR (dB) = 10log(Pf/PfS)

式中:Pf是ADC输出中频率f处的功率。

PfS是ADC输出中频率fS处的功率。

电源抑制比

电源的变化影响满标度转换,但不影响转换器的线性度。PSRR是指定满标度(±200 mV)过渡点的最大变化,这是由于电源电压与标称值的变化引起的(见图7)。

隔离瞬态抗扰度

隔离瞬态抗扰度规定了施加在隔离边界上的瞬态脉冲的上升/下降速率,超过此速率时钟或数据将被破坏。(使用瞬态脉冲频率为100 kHz。)

操作理论

电路信息

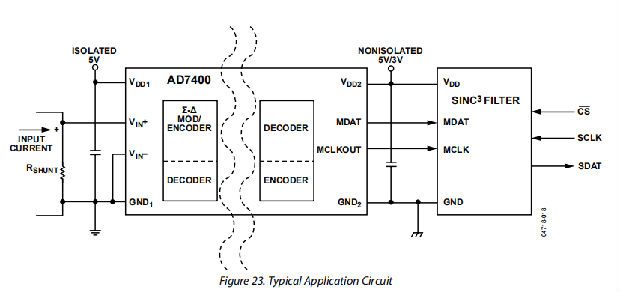

AD7400A隔离∑-Δ调制器将模拟输入信号转换为高速(10 MHz典型)的单位数据流;调制器的单位数据的时间平均值与输入信号成正比。图23显示了一个典型的应用电路,其中AD7400A用于在模拟输入、电流感应电阻器和数字输出之间提供隔离,然后由数字滤波器处理以提供N位字。

模拟输入

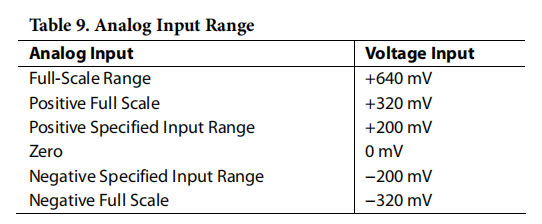

AD7400A的差分模拟量输入由开关电容电路实现。该电路实现了将输入信号数字化为1位输出流的二阶调制器级。采样时钟(MCLKOUT)为转换过程以及输出数据帧时钟提供时钟信号。该时钟源位于AD7400A内部。调制器对模拟输入信号进行连续采样,并与内部电压基准进行比较。在转换器的输出端出现一个数字流,该数字流准确地表示随着时间推移的模拟输入(见图21)。

0V的差分信号(理想情况下)在MDAT输出引脚处产生一个1和0的流。这个输出在50%的时间内是高的,而在50%的时间内是低的。一个200毫伏的差分输入产生一个1和0的流,高达81.25%。-200 mV的差分输入产生1和0的流,在时间上高达18.75%。

320毫伏的差分输入产生理想的所有输入流。这是AD7400A的绝对满标度范围,而200 mV是指定的满标度范围,如表所示9。

要重建原始信息,需要对输出进行数字过滤和抽取。建议使用Sinc滤波器,因为它比AD7400A调制器高一个数量级。如果使用256抽取率,则得到的16位字速率为39 kHz,假设内部时钟频率为10 MHz。图22显示了AD7400A相对于16位输出的传输函数。

差分输入

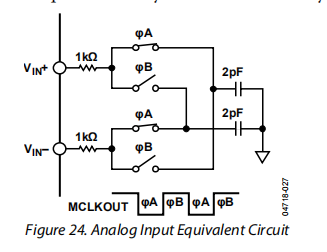

调制器的模拟输入是开关电容设计。模拟信号通过高线性采样电容器转换成电荷。模拟输入的简化等效电路图如图24所示。驱动模拟输入的信号源必须能够每半个MCLKOUT周期向采样电容器提供电荷,并在下半个周期内达到所需的精度。

由于AD7400A对其模拟输入端的差分电压进行采样,因此通过在每个输入端提供低共模噪声的输入电路来获得低噪声性能。用于驱动模拟输入的放大器在获得AD7400A的高性能方面起着关键作用。

当电容性负载切换到运放的输出端时,振幅瞬间下降。运放试图纠正这种情况,在这个过程中,达到了它的转换率极限。这种非线性响应会导致过度振铃,从而导致失真。为了解决这个问题,可以在放大器和AD7400A的输入端之间连接一个低通RC滤波器。每个输入端的外部电容器有助于提供采样过程中产生的电流尖峰,电阻器将运放与负载的瞬态特性隔离。

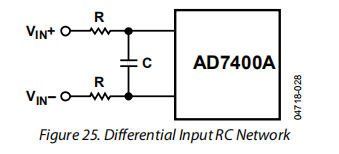

图25显示了驱动差分输入以获得最佳性能的推荐电路配置。两个输入管脚之间的一种电容器,它能使一个输入所需的大部分电荷有效地由另一个输入提供。串联电阻再次将任何运放与采样过程中产生的电流峰值隔离。电阻器和电容器的建议值分别为22Ω和47 pF。

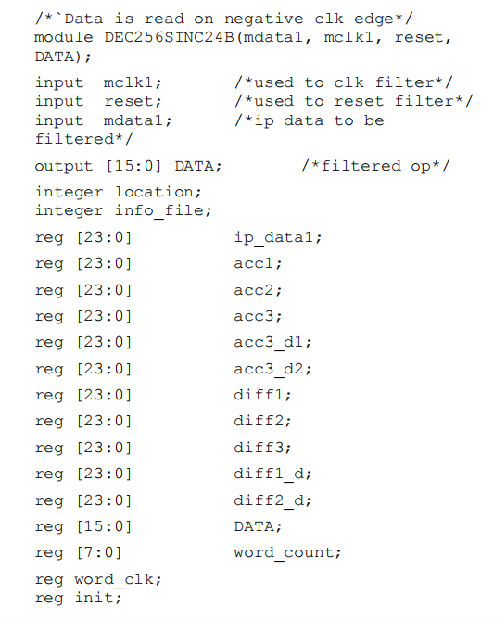

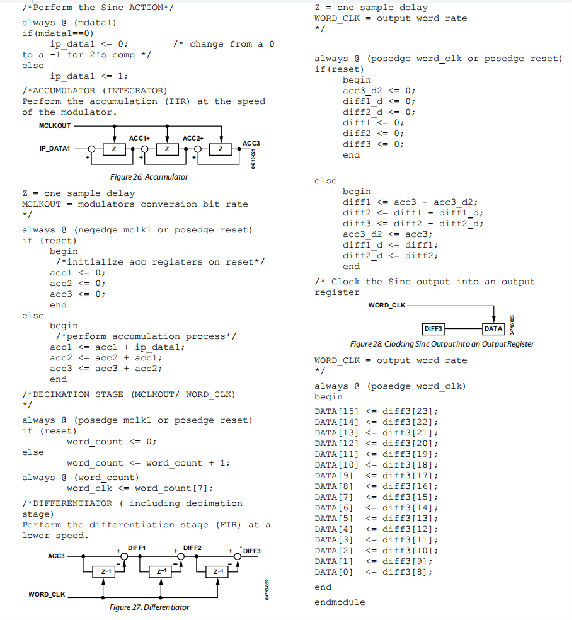

数字滤波器

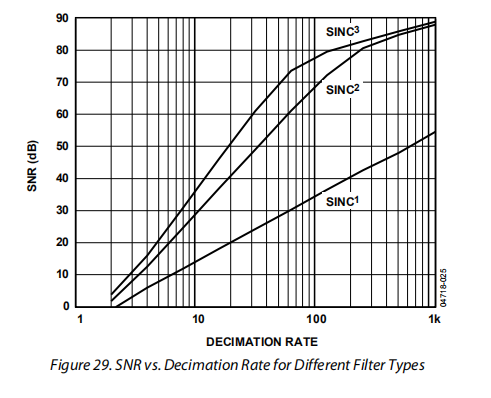

建议与AD7400A一起使用Sinc滤波器。该滤波器可以在FPGA或DSP上实现。下面的Verilog代码提供了一个在Xilinx®Spartan II 2.5v FPGA上实现Sinc滤波器的示例。此代码可以编译为另一个FPGA,例如Altera®设备。注意,在这种情况下,数据是在负时钟边缘读取的;但是,如果愿意,可以在正时钟边缘读取。图29显示了在不同的过滤器类型中使用不同抽取率的效果。

应用程序信息

接地及布置

强烈建议在V和V上使用值为100 nF的电源去耦。一个或两个V管脚上的去耦不会显著影响性能。在涉及高共模瞬态的应用中,应注意确保隔震屏障上的板耦合最小化。此外,电路板布局的设计应确保发生的任何耦合都会对给定组件侧的所有管脚产生同样的影响。未能确保这一点可能会导致引脚之间的电压差超过设备的绝对最大额定值,从而导致闭锁或永久性损坏。使用的任何去耦装置应尽可能靠近电源插脚。

模拟输入中的串联电阻应最小化,以避免任何失真效应,特别是在高温下。如果可能的话,均衡每个模拟输入上的源阻抗以最小化偏移。注意模拟输入PCB轨迹上的不匹配和热电偶效应,以减少偏移漂移。

评估AD7400A性能

一个简单的独立的AD7400A评估板可与分裂的地面和AD7400A包下的分裂板,以确保隔离。此板允许访问设备上的每个管脚进行评估。外部电源和所有其他电路(如数字滤波器)必须由用户提供。

绝缘寿命

所有绝缘结构,经受足够的时间和/或电压,都容易击穿。除了监管机构进行的测试外,模拟设备还进行了一系列广泛的评估,以确定AD7400A内绝缘结构的寿命。

这些测试使设备群承受连续的交叉隔离电压。为了加速故障的发生,选定的测试电压值超过了正常使用的电压值。记录这些装置的失效时间值,并用于计算加速度系数。然后使用这些因素计算正常运行条件下的故障时间。表7中所示的值是以下两个值中的较小值:

•确保至少50年持续使用寿命的价值。

•CSA/VDE批准的最大工作电压。

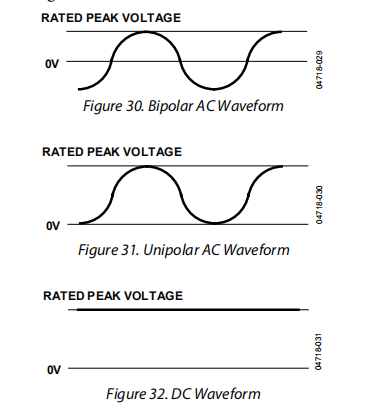

还应注意,AD7400A的寿命根据施加在隔离栅上的波形类型而变化。根据波形是双极性交流、单极性交流还是直流,I耦合器的绝缘结构会受到不同的压力。图30、图31和图32显示了不同的隔离电压波形。

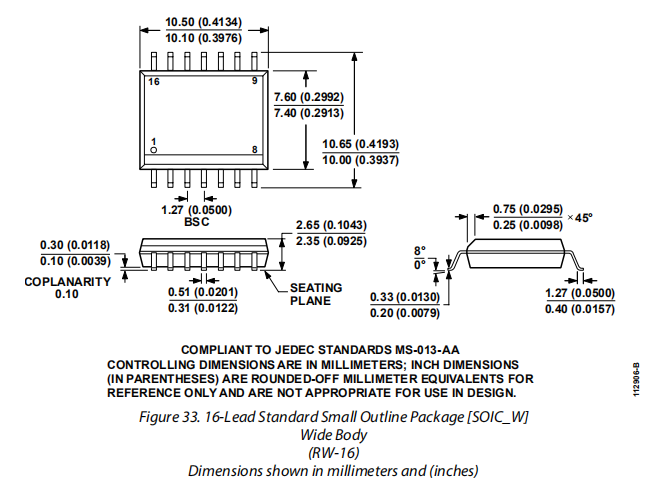

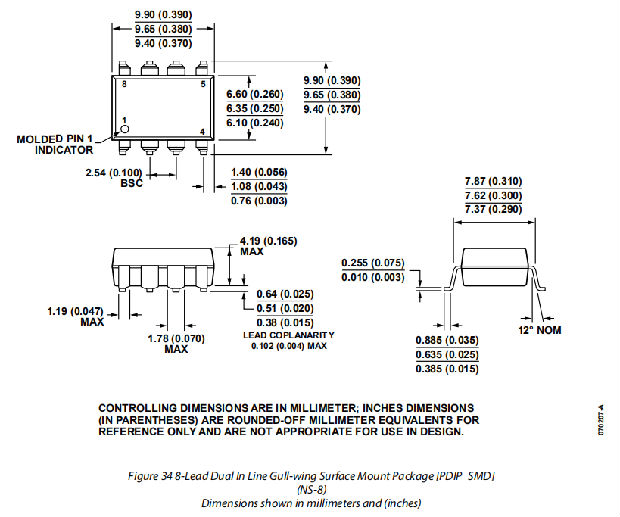

外形尺寸