AD5543点击型号即可查看芯片规格书

AD5553点击型号即可查看芯片规格书

特征

16位分辨率AD5543;14位分辨率AD5553;±1 LSB DNL;±2用于AD5543的LSB INL;±1 LSB INL用于AD5553;低噪声12 nV/√Hz;低功率,IDD=10 A;0.5 s沉淀时间;4Q乘参考输入;2毫安满标度电流 20%,VREF=10伏;内置RFB有助于电压转换;3线接口;超紧凑型MSOP-8和SOIC-8封装。

应用

自动测试设备;仪表;数字控制校准;工业控制可编程逻辑控制器。

一般说明

AD5543/AD5553是精密的16/14位、低功耗、电流输出、小外形因数数模转换器,设计用于在一个5V电源和一个±10V倍频参考电压下工作。

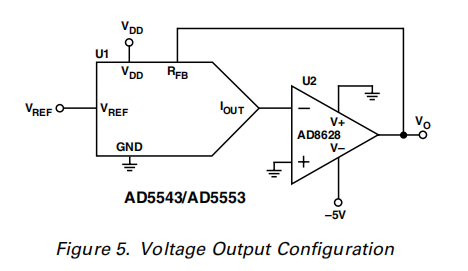

应用的外部参考VREF确定满标度输出电流。当与外部运放结合时,内部反馈电阻器(RFB)有助于R-2R和温度跟踪以实现电压转换。

串行数据接口使用串行数据输入(SDI)、时钟(CLK)和芯片选择(CS)提供高速、3线微控制器兼容的输入。

AD5543/AD5553采用超紧凑型(3 mm*4.7 mm)MSOP-8和SOIC-8封装。

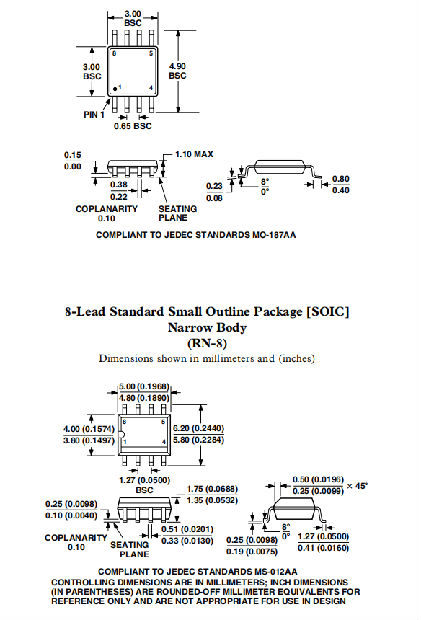

功能框图

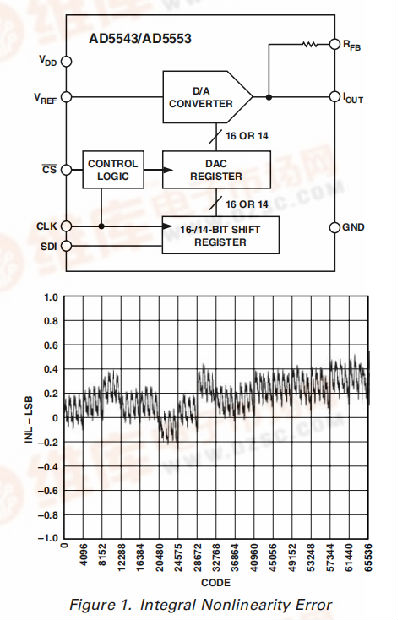

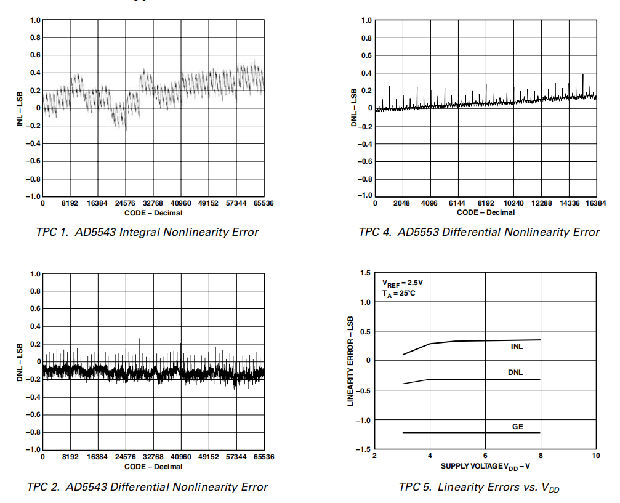

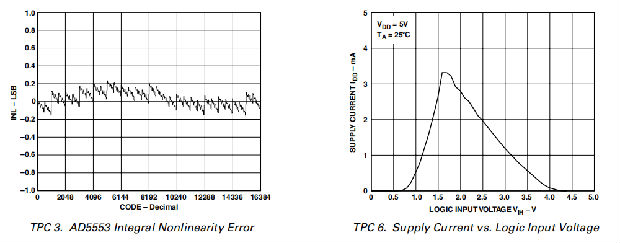

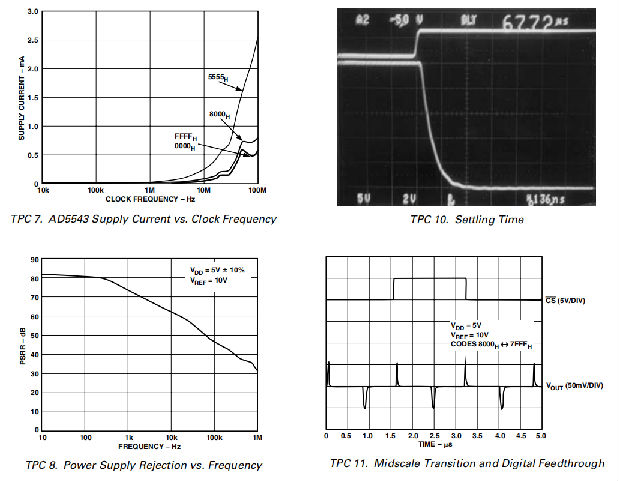

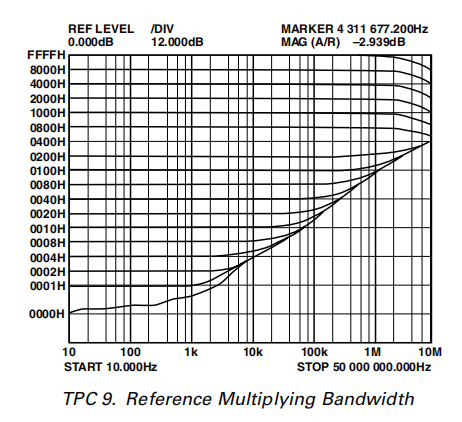

AD5543/AD5553–典型性能特征

电路操作

AD5543/AD5553包含16/14位、电流输出、数模转换器、串行输入寄存器和DAC寄存器。两个转换器都使用3线串行数据接口。

D/A转换器段

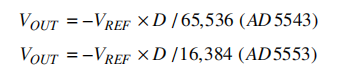

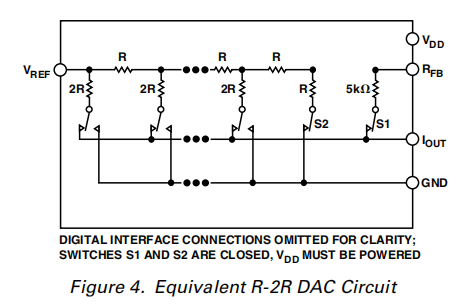

DAC架构使用了电流控制的R-2R梯形图设计。图4显示了典型的等效DAC结构。DAC包含一个与外部运算放大器一起使用的匹配反馈电阻器(见图5)。通过RFB和IOUT端子分别连接到运算放大器输出和逆变节点,可以实现如下精确的电压输出:

注意,输出电压极性与直流参考电压的VREF极性相反。

这些数模转换器设计用于在负或正参考电压下工作。VDD电源引脚仅由内部逻辑用于驱动DAC开关的“开”和“关”状态。

注意,匹配开关与内部5 kΩ反馈电阻器串联使用。如果用户试图测量RFB,则必须向VDD供电以实现连续性。

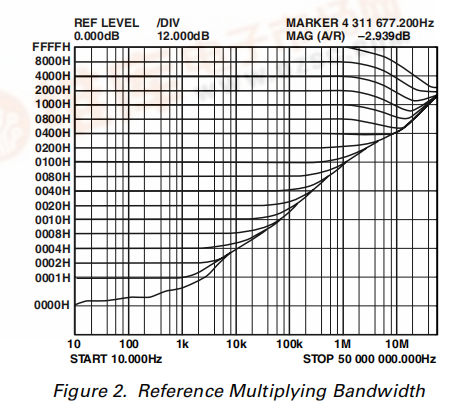

这些数模转换器也被设计用来容纳交流参考输入信号。AD5543可在-12 V至+12 V范围内调节输入参考电压。参考电压输入显示恒定的标称输入电阻值为5 kΩ,±30%。DAC输出(IOUT)依赖于代码,产生各种电阻和电容。外部放大器的选择应考虑AD5543在放大器的反向输入节点上产生的阻抗变化。反馈电阻与DAC梯形电阻并联,控制输出电压噪声。为了保持良好的模拟性能,建议电源绕过0.01μF至0.1μF陶瓷或片式电容器,并与1μF钽电容器并联。由于电源的频率抑制比降低,用户必须避免使用开关电源。

串行数据接口

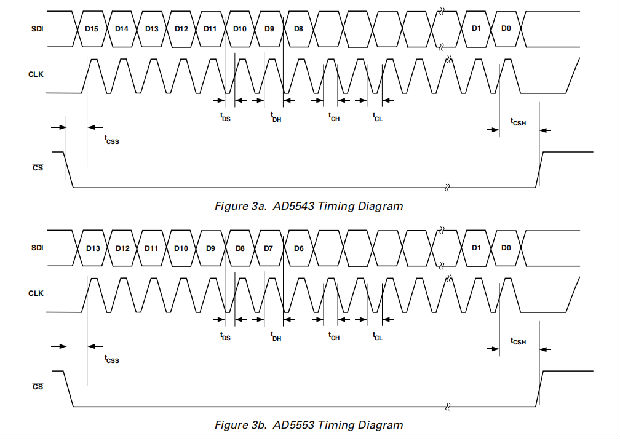

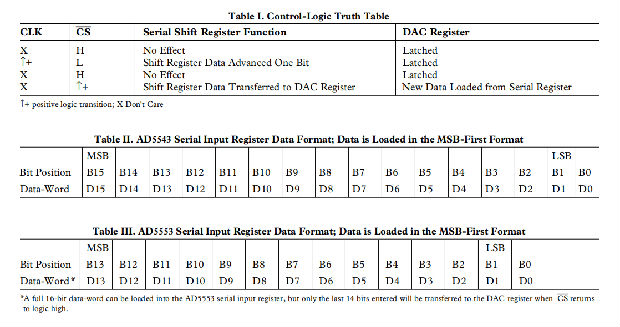

AD5543/AD5553使用3线(CS、SDI、CLK)串行数据接口。新的串行数据以16位数据字格式输入AD5543的串行输入寄存器。首先加载MSB。表II定义了16个数据字位。根据接口定时规范中规定的数据设置和保持时间要求,数据放置在SDI引脚上,并在CLK正时钟边缘的寄存器中计时。当CS引脚被选通以将串行寄存器数据传输到DAC寄存器时,只有最后16位进入串行寄存器。由于大多数微控制器以8位字节输出串行数据,因此可以将两个数据字节写入AD5543/AD5553。加载串行寄存器后,CS的上升沿将串行寄存器数据传输到DAC寄存器;在此选通期间,不应切换CLK。对于AD5553,16位时钟周期,忽略两个LSB。

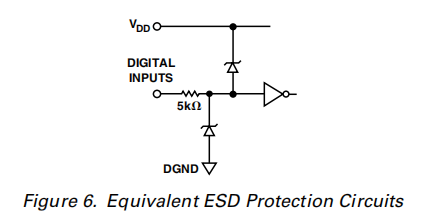

ESD保护电路

所有逻辑输入引脚都包含反偏ESD保护齐纳二极管,如图6所示,齐纳二极管接地(GND)和VDD。

PCB布局和电源旁路

采用紧凑、最小引线长度的PCB布局设计是一个很好的实践。通向输入端的导线应尽可能短,以尽量减小红外损耗和杂散电感。

为了获得最佳的稳定性,还必须使用高质量的电容器绕过电源。应使用0.01μF至0.1μF的片状或片状陶瓷电容器绕过设备的电源线。还应在电源处使用低ESR 1μF至10μF的钽或电解电容器,以尽量减少瞬态干扰并滤除低频纹波VREF和RFB之间的PCB金属轨迹也应匹配,以最小化增益误差。

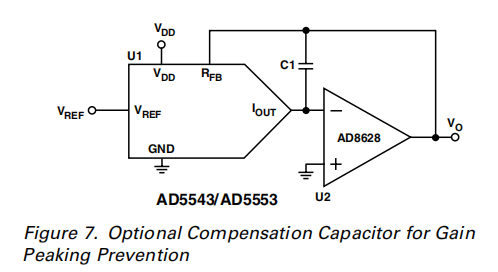

应用稳定性

在I-to-V配置中,DAC的输出端和运放的逆变节点必须尽可能地连接在一起,并且必须采用合适的PCB布局技术。由于每一个代码变化都对应于一个阶跃函数,因此如果运算放大器具有有限的GBP并且在逆变节点处存在过大的寄生电容,则可能会出现增益峰值。

如图7所示,可以添加可选补偿电容器C1以保持稳定性。C1应根据经验确定,但20 pF通常足以补偿。

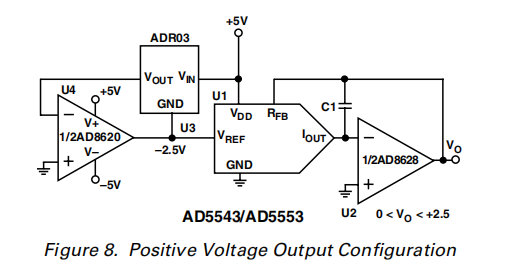

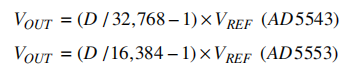

正电压输出

为了获得正电压输出,由于电阻器的公差误差,与通过反向放大器的输出反转相比,对DAC的输入施加负参考是首选的。为了产生一个负参考,参考可以通过运放进行电平移位,使参考的VOUT和GND引脚分别成为虚拟接地和-2.5v(见图8)。

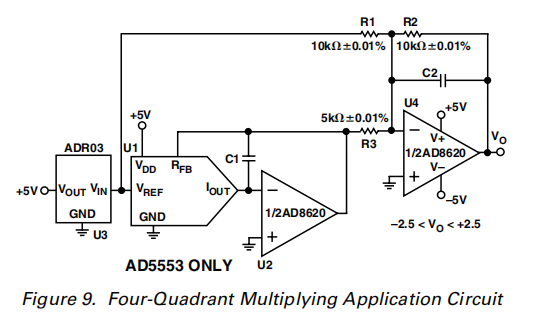

双极输出

AD5543/AD5553本质上是一个2象限乘法D/a转换器。也就是说,它可以很容易地设置为单极输出操作。满标度输出极性与参考输入电压成反比。

在某些应用中,可能需要产生全四象限乘法能力或双极输出摆幅。通过使用配置为求和放大器的附加外部放大器U4,这很容易实现(见图9)。在该电路中,第二放大器U4提供2的增益,该增益将输出跨距幅度增加到5v。使用与参考电压2.5v偏移的外部放大器偏置可产生完整的四象限乘法电路。该电路的传输方程表明,当输入数据(D)从代码0(VOUT=-2.5 V)递增到中刻度(VOUT=0 V)再到满刻度(VOUT=+2.5 V)时,会产生正负输出电压。

对于AD5543,电阻容限成为用户应注意的主要误差。

可编程电流源

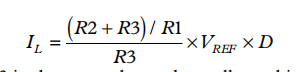

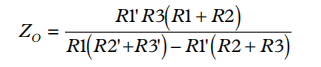

图10显示了一个多功能的V-I转换电路,使用了一个改进的霍尔电流泵。除了提供精确的电流转换外,该电路还支持双向电流流和高压合规性。该电路可用于负载高达500Ω的4至20毫安电流变送器。如图10所示,如果电阻网络匹配,负载电流为:

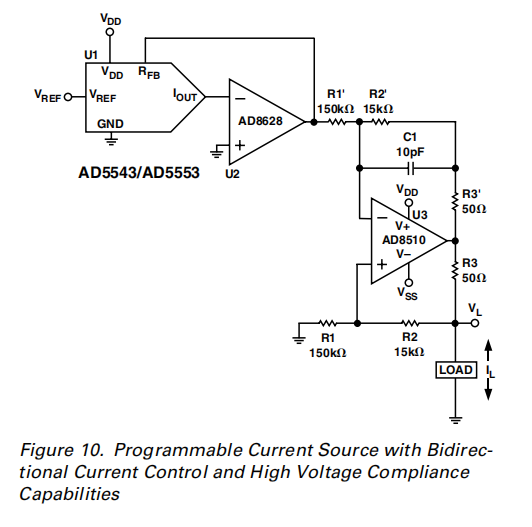

右3在理论上可以使小电流达到所需的U3输出电流驱动能力。这种电路是多功能的,因此AD8510可以±两个方向的20毫安,电压柔度接近15伏,这主要受到U3的供电电压的限制。但是,用户必须注意补偿。如果没有C1,可以显示输出阻抗变为:

如果电阻完全匹配,则ZO是无限的,这是理想的,并且表现为理想的电流源。另一方面,如果它们不匹配,ZO可以是正的,也可以是负的。负的会引起振荡。因此,需要C1来防止振荡。对于关键应用,C1可以根据经验找到,但通常落在少数pF的范围内。

外形尺寸8-铅微粒体包[MSOP](RM-8)

尺寸单位为毫米