特征

利用优势和兼容性构建CMOS和IXYS HDMOSTM工艺。

锁存保护

高峰值输出电流:8A峰值

在4.5V到25V之间工作

在故障情况下禁用输出的能力

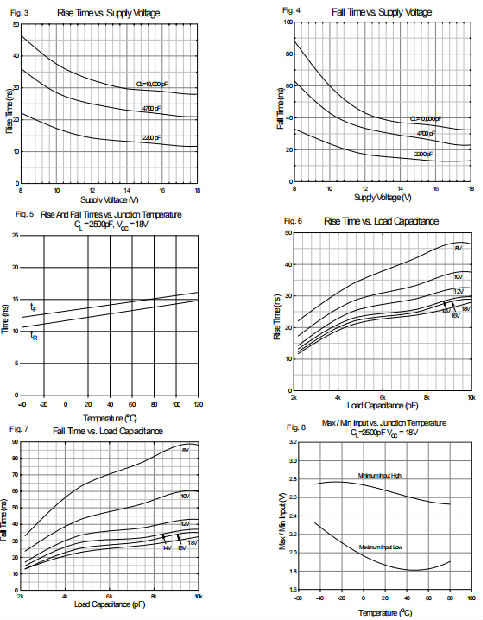

高容性负载驱动能力:2500pF in<15ns

相应的上升和下降时间

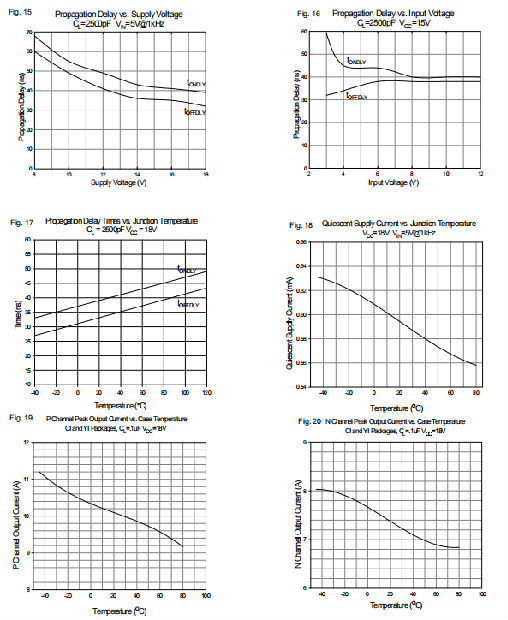

低传播延迟时间

低输出阻抗

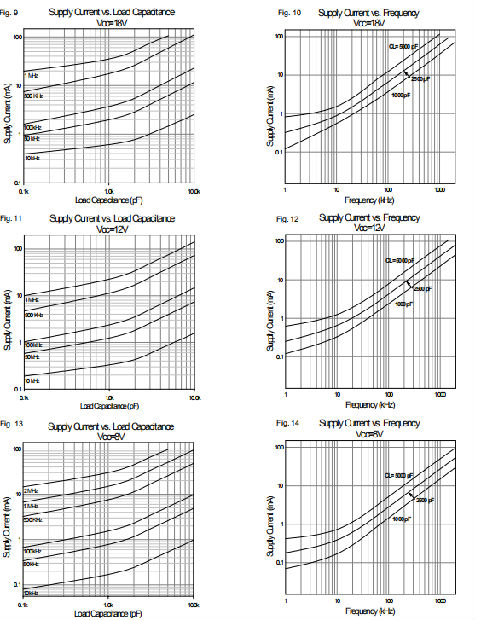

低供电电流

应用

驱动mosfet和igbt

短路时限制di/dt

电机控制

线路驱动器

脉冲发生器

本地电源开/关开关

开关电源(SMPS)

直流-直流转换器

脉冲变压器驱动器

D类开关放大器

一般说明

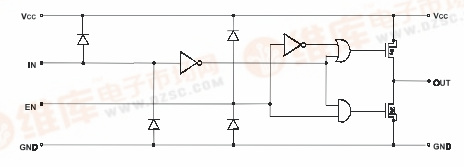

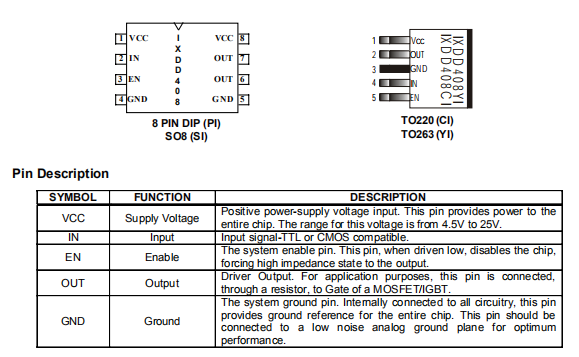

IXDD408是高速大电流门驱动器专为驱动最大的mosfet和IGBTs的最小切换时间和最大切换时间实际频率限制。IXDD480可以产生电压上升和跌落时间小于30ns。驱动程序的输入是与TTL或CMOS兼容,完全免疫在整个操作范围内锁定。设计在IXDD408中,几乎消除了小的内部延迟、交叉传导/电流发射。它的特点在工作电压和功率方面有很宽的安全裕度使IXDD408在性能和价值上无与伦比。IXDD408具有一种独特的功能,可以禁用在故障条件下输出。当逻辑下限为强制进入启用输入,两个最终输出阶段mosfet(NMOS和PMOS)被关闭。作为一个结果,IXDD408的输出进入三态模式并在以下情况下实现了MOSFET/IGBT的软关断检测到短路。这有助于防止损坏如果是这样的话,MOSFET/IGBT可能会发生这种情况由于dv/dt过电压传输而突然关闭。IXDD408在标准8针P-DIP(PI)中提供,SOP-8(SI),5针至-220(CI)和至-263(YI)表面安装组件。

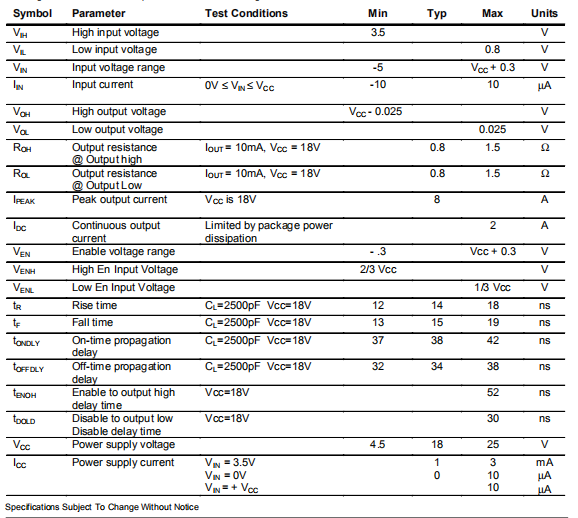

电气特性

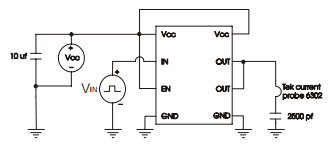

除非另有说明,否则TA=25 oC、 4.5V≤VCC≤25V。所有与接地有关的电压测量。按照测试条件中的描述配置IXDD408。

注1:超出所列“绝对最大额定值”的参数操作设备可能导致永久性设备损坏。典型值表示设备运行的条件,但不表示保证特定的性能限制。保证规范仅适用于列出的试验条件。长期暴露在绝对最大额定条件下可能会影响设备的可靠性。

注意:这些设备对静电放电敏感;遵循适当的静电放电程序在处理和组装此组件时。

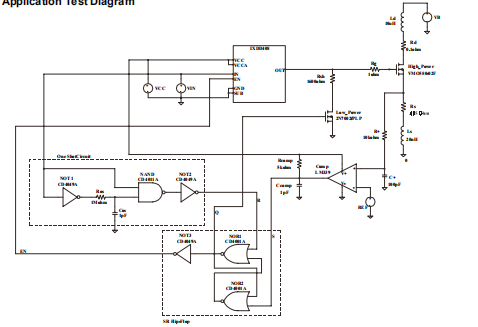

大功率MOSFET模块中的短路,如VM0580-02F(580A,200V),如图26所示,可导致通过模块的电流超过1500A在因热失控而自毁之前达到或超过10微秒。因此,需要一些保护电路来关闭MOSFET模块。但是,如果模块关闭速度过快,会有电压瞬变的危险Ldi/dt引起的漏极(其中L表示总电感与排水管串联)。如果这些电压瞬变超过MOSFET的额定电压,这会导致雪崩击穿。IXDD408具有独特的能力,可以轻轻地关闭大功率MOSFET模块,大大减少了这些Ldi/dt瞬态。因此,IXDD408有助于防止两种危险;过流和雪崩故障di/dt引起的过电压瞬变。IXDD408的设计不仅能在正常情况下提供±8A条件,但也允许它的输出进入一个高阻抗状态。这允许IXDD408输出控制检测到过电流时的单独弱下拉电路限制和单独控制dVGS/dt闸门的停机条件关掉。该电路如图27所示。参考图27,保护电路应包括一种比较器,其正输入与源相连接在VM0580-02中。应在输入端添加低通滤波器以消除由电压引起的任何故障通过连接源电阻和地面。(这些小故障可能会导致比较器)。

比较器的输出应连接到SRFF(设置复位触发器)。触发器控制两个启用信号,以及低功率MOSFET栅极。请注意CMOS 4000-串联装置的VCC范围为3至15 VDC(带18 VDC为最大允许限值)。一种低功率MOSFET,如2N7000,与电阻器,将使VMO580-02F栅极电压下降逐步地。电阻的选择应确保RC时间常数为100us,其中“C”是VMO580-02F。为了恢复正常操作,需要在SRFF的输入以再次启用IXDD408。此重置可以通过在IXDD408输入信号和SRFF重启输入。唯一的机会将在IXDD408输入上升时产生脉冲,并且脉冲将SRFF输出重置为正常工作。当发生短路时,低值电流传感电阻器(Rs=0.005 Ohm)上的电压降在MOSFET源和地之间,增加。这个在预设水平触发比较器。SRFF驱动低输入使能管脚禁用IXDD408输出。这个SRFF还打开低功率MOSFET(2N7000)。这样,大功率MOSFET模块就被轻轻地关闭了通过IXDD408,防止其破坏。

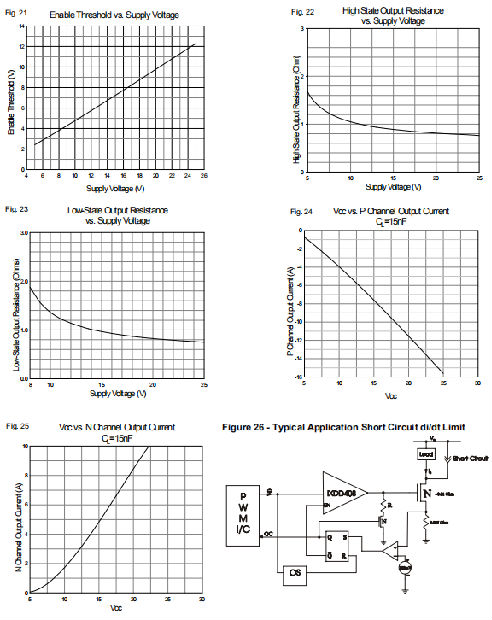

设计高速MOSFET驱动电路时利用IXDD408,保持一定的设计是非常重要的记住标准,以便优化驱动程序的性能。需要特别注意供应旁路,接地,最小化输出引线电感。例如,我们使用IXDD408向5000pF电容性负载,从0伏到25伏,25ns…使用下列公式:I=&Δt=25ns我们可以确定充电5000pF至25伏在25纳秒的时间内,需要5安培的恒定电流电流不是恒定的,会在附近某处达到峰值8A条)。

电源旁路

为了使我们的设计能够正确地打开负载,IXDD408必须能够从电源中吸取5A的电流在25年代。这意味着必须有非常低的阻抗在驱动器和电源之间。最常见的实现这种低阻抗的方法是绕过驱动器上的电源,其电容值为大小大于负载电容。通常,这个将通过设置两种不同类型的旁路来实现电容器,具有互补阻抗曲线,非常接近。(这些电容器应小心选用低电感、低电阻、高脉冲电流的服务电容器)。导线长度可能在高频辐射由于有电感,所以应注意保持长度这些旁路电容器和IXDD408之间的导线达到绝对最小值。接地为了使设计正确地关闭负载,IXDD408必须能够将这5A的电流排放到接地系统。有三条回流路径需要考虑的是:路径1在IXDD408之间而且它很重。路径2在IXDD408和它的电源之间供应。路径3在IXDD408和任何逻辑之间正在驾驶它。这三条路都应该在电阻和电感尽可能短实用。此外,应尽一切努力保持这些三条地面路径明显分开。否则,(对于实例),负载返回的接地电流可能产生一个对驱动IXDD408的逻辑线。

输出引线电感

与电源旁路和接地同等重要的是与输出引线电感有关的问题。尽一切努力应该在司机和装载尽可能短和宽。如果必须放置驱动器距离负载2“以上,则输出引线应当作传输线。在这种情况下,双绞线应该考虑,每个双绞线的回线应尽可能靠近驱动器,并直接连接到负载的接地端子。

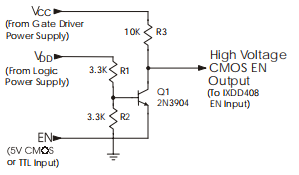

IXDD408的使能(EN)输入为高电压CMOS逻辑电平输入,其中EN输入阈值为1/2 VCC,可能与5V CMOS或TTL输入电平不兼容。IXDD408 EN输入是专门为用高压CMOS逻辑提高抗噪声能力水平。在典型的门驱动器应用中,VCC=15V和EN输入阈值为7.5V,5V CMOS逻辑高输入应用于这个典型的IXDD408应用程序的EN输入将是被误解为逻辑上的低级,可能导致不受欢迎的或意外的结果。下面的注释是可选的TTL或5V CMOS电平的自适应。

图28中的电路减轻了这种潜在的逻辑电平翻译TTL或5V CMOS逻辑输入时的误解至IXDD408 EN所需的高压CMOS逻辑电平输入。从图中可以看出,VCC是栅极驱动电源,通常设置在8V到20V之间,而VDD是逻辑电源电源,通常在3.3V到5.5V之间。电阻器R1和R2形成一个分压器网络,使Q1基位于预期TTL逻辑转换的中点水平。TTL或5V CMOS逻辑低,VTTLLOW=~<0.8V,输入应用于Q1发射器将驱动它。这会导致级别转换器输出,Q1采集器输出设置为VCESATQ1+VTTLLOW=<~2V,这足够低解释为高压CMOS逻辑低(<1/3VCC=5VVCC=15V,见IXDD408数据表。)TTL高,VTTLHIGH=>~2.4V,或5V CMOS高,V5VCMOSHIGH=~>3.5V,用于图28将导致Q1偏离。这将导致第一季度集电极由R3向上拉至VCC=15V,并提供高压CMOS逻辑高输出。高压CMOS应用于IXDD408 EN输入的逻辑EN输出将启用它允许门驱动器作为8安培的输出完全工作。图28中电路的总组件成本小于如果购买数量大于1K件,则超过0.10美元。它是建议物理放置水平仪转换器电路应靠近TTL源或CMOS逻辑电路最大限度地抑制噪声。