特征

用户可编程软启动

主动低停机

用户可编程最大负载

循环

可接近的5V参考电压

欠压锁定

运行至1MHz

0.4A源/0.8A汇场效应管驱动器

低100微安启动电流

经济型一次侧控制器

说明

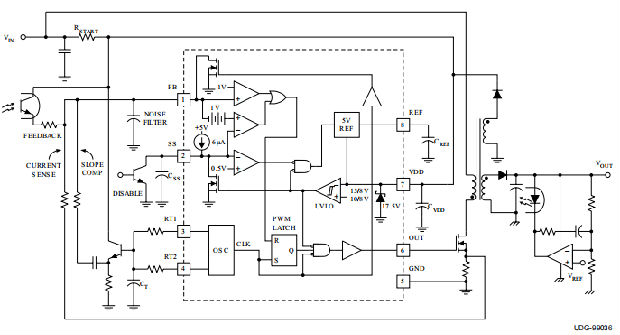

UCC3809系列BCDMOS经济型低功耗集成电路包含离线和隔离所需的所有控制和驱动电路直流-直流固定频率电流模式开关电源最少的外部零件数量。内部实现的电路包括欠压锁定,启动电流小于100微安,用户交流可接受电压基准,确保锁定操作的逻辑,脉宽调制分流器,以及图腾极输出级至接收器或源峰值电流。这个输出级适用于驱动N通道mosfet,在关断时很低国家。

振荡器频率和最大占空比编程为电阻器和电容器。UCC3809系列还具有全循环软开始。

该家族有UVLO阈值和滞后水平离线和直流-直流系统,如左表所示。

UCC3809和UCC2809在8针SOIC(D)、PDIP中提供(N) ,TSSOP(PW)和MSOP(P)包。小TSSOP和MSOP软件包使该设备非常适合用于电路板空间和高度都很优越。

典型应用图

绝对最大额定值*

VDD、VDD、VDD、VDD、VDD、VDD、VDD、VDD、VDD、VDD、VDD、VDD、VDD。19伏

IVDD。。。25毫安

IOUT(tpw<1毫秒,占空比<10%)。。。0.4A至0.8A

RT1,RT2,不锈钢。。。。。。0.3V至参考电压+0.3V

IREF。。。。。。。。。。。。。。。。。。。。。。。。。。-15毫安

储存温度。。。-65-C至+150-C

结温。。。。。。-55摄氏度至150摄氏度

铅温度(焊接,10秒)。。。+300摄氏度

可能发生损坏的值。

除非另有说明,否则所有电压均与接地有关。

电流为正流入,负流出规定的热量-2。有关包装的热限制和注意事项,请参阅数据手册的包装部分。

管脚说明

FB:该引脚是电流检测的求和节点反馈、电压感应反馈(通过光耦)和坡度补偿。导出坡度补偿从正时电容器的上升电压外部小信号NPN晶体管缓冲。

外部高频滤波器电容该节点到GND的放电由内部250 on在脉宽调制关闭时间内的电阻NMOS FET,并提供RC时间设定的有效前缘冲裁电流反馈电阻常数FB输入电阻和高频滤波电容该节点对地电容。GND:所有参考接地和电源接地功能。

输出:这个引脚是大电流功率驱动器输出。一个建议最小串联栅极电阻为3.9 在高偏压下运行时限制栅极驱动电流电压。

参考:内部5V参考输出。这个参考是缓冲,可在参考引脚上使用。REF应该是绕过0.47 F陶瓷电容器。

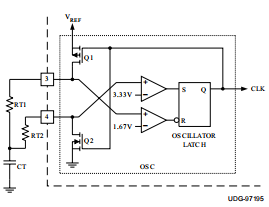

RT1:该引脚连接到正时电阻器RT1和控制内部振荡器的正斜坡时间(Tr=0.74 (CT+27pF) RT1)。正阈值内部振荡器通过非活动定时来感应电阻器RT2,连接到引脚RT2和正时电容器CT。

RT2:该引脚连接到正时电阻器RT2和控制内部振荡器的负斜坡时间(Tf=0.74 (CT+27pF) RT2)。负阈值通过非活动定时感测内部振荡器的电阻器RT1,连接到引脚RT1和正时电容器CT。

这个针有两个功能。软起动正时电容器连接到SS并由内部微安电流源。正常软启动时SS为放电至至少0.4V,然后向正电压过渡至1V在这段时间内,输出驱动器保持在低位。作为党卫军从1V到2V的充电软启动由增加输出占空比。如果SS低于0.5V,输出驱动器被抑制并保持在低位。用户可接近的5V电压基准也会变低和IVDD

VDD:此设备的电源输入连接。这个引脚并联调节在17.5V以下DMOS输出驱动级的额定电压。视频显示器应使用1 F陶瓷电容器旁路。

应用程序信息

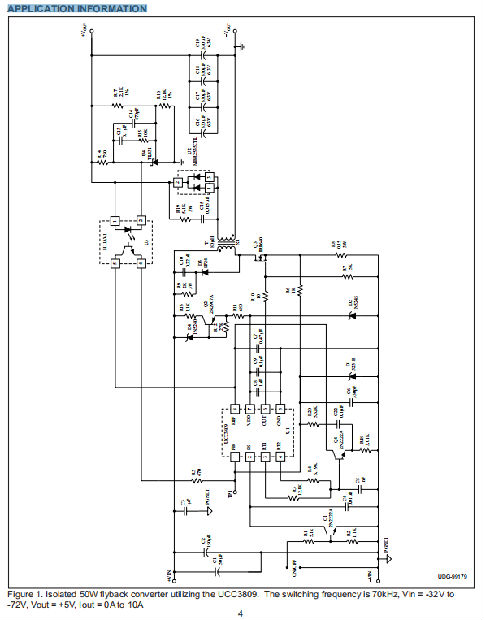

典型的应用程序图显示

使用UCC3809的反激变换器。

电容器CREF和CVDD分别是参考电压和IC输入电压的局部去耦电容器。两个电容器都应该是低ESR和ESL陶瓷,放置在尽可能靠近IC引脚的位置,然后返回直接连接到芯片的接地引脚以获得最佳稳定性。REF提供了许多IC函数的内部偏差,CREF应至少为0.47μF,以防止REF从下垂。

FB引脚UCC3809的基本前提是传感反馈信号来自光耦由位于在第二面。这个信号和电流感应信号和FB引脚,并与1V阈值进行比较,如典型应用图。超过1V阈值重置脉冲宽度调制锁存器并调制输出驱动器实时性很像UC3842。在没有FB信号的情况下,输出将遵循os cillator的编程最大开启时间。添加坡度补偿时,使用小电容器与振荡器波形的交流耦合在将此信号求和到FB引脚之前。正确地选择光耦的发射电阻,电压检测信号可以迫使FB节点超过当被比较的输出超过所需水平时的1V阈值。这样做会驱动UCC3809占空比为零。振荡器

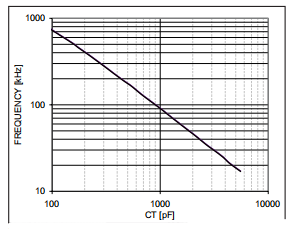

以下公式设置振荡器频率:

F CT-pF-RT-RT[](……)OSC=•+•+–0 74 27 1 2 1。

D RT CT pF F最大OS C=••+•0 74 1 27。( )

当Q1开启时,CT通过Q1的RDS(on)充电

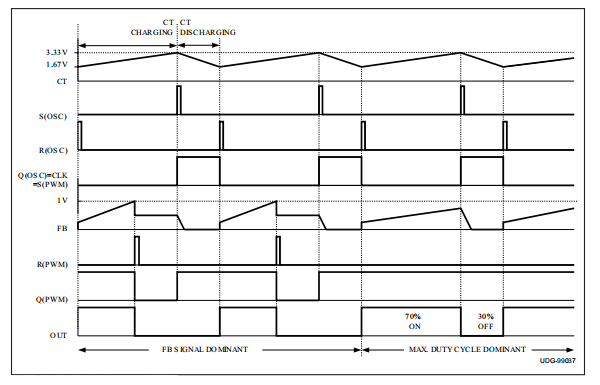

第1部分。在充电过程中,CT的电压为通过RT2感应到。振荡器锁存器的S输入,S(OSC)是电平敏感的,因此通过上阈值(设置为2/3vref或3.33V(典型的5.0V参考电压))设置振荡器的Q输出(CLK信号)锁紧。高CLK信号导致关闭Q1和打开Q2。CT现在通过RT2和第2季度的RDS(开)。CT从3.33V放电到下部阈值(对于典型的5.0V,设置为1/3 VREF或1.67V参考)通过RT1感应。oscil lator锁存器R(OSC)的R输入也是电平敏感的,并重置CT超过1.67V阈值时CLK信号低,关闭Q2并打开Q1,启动另一个充电循环。

图显示了与振荡器锁存器和脉宽调制锁存器相关的波形(如典型应用图所示)。高CLK信号不仅启动CT的放电循环,它还打开内部NMOSFB管脚上的FET导致任何外部电容用于连接到此插针的前缘消隐被卸到地上。通过排出任何外部电容器在外部完全接地开关关断时间,转换器的抗噪性为增强型,允许用户在较小的RC组件中设计前缘冲裁。高CLK信号还设置了PWM锁存器的电平敏感S输入,S(脉宽调制),高,导致高输出,Q(脉宽调制),as如图所示。此Q(脉宽调制)信号将保持高电平直到接收到复位信号R(脉宽调制)。高R(脉冲宽度调制)信号源于FB信号穿过1V阈值,或在软启动期间,或如果SS引脚被禁用。

假设满足UVLO阈值,只要Q(PWM)高且S(PWM),也称为CLK,是低的。只要FB当CLK低时,信号触发1V阈值。如果FBCLK低时,信号不超过1V阈值,输出信号将由最大占空比控制由用户编程的循环。图说明了最大值设计的各种波形占空比70%。

申请信息(续)

CT的建议值为1nF,频率为100 kHz或更小的范围和更小的CT,以获得更高的频率。RT1的最小推荐值RT2分别为10kΩ和4.32kΩ。使用这些值之间保持至少20:1的比率内部FET和外部定时电阻的RDS(on),使得温度上的频率变化最小。因为振荡器对电容耦合,通过看电路上常见的RT1-RT2-CT节点与直接看引脚3和引脚4相反的电路板。为了良好的抗噪性,RT1和RT2应放置为尽可能靠近IC的引脚3和4。CT应该是直接返回到接地引脚o

申请信息(续)

同步

两种同步方案如图所示可以用UCC3809的内部振荡器成功实现。两种方案都允许访问斜坡补偿所需的正时斜坡对编程最大占空比的影响最小。

在没有同步脉冲的情况下,PWM控制器将以RT1、RT2和计算机断层扫描。此自由运行频率必须大约为比同步脉冲频率低15%到20%以确保自由运行的振荡器不穿过比较器所需同步脉冲之前的阈值。

选项I使用同步脉冲将引脚3拉低,触发内部1.67V比较器重置RS锁定并启动充电循环。的谷电压当使用此项同步时,CT波形更高配置,减少斜坡充放电倍,从而增加工作频率;另一方面,CT电压波形的整体形状不改变。

选项II使用同步脉冲叠加CT波形峰值上的同步电压。这个触发内部3.33V比较器,启动放电循环。同步脉冲和自由脉冲相加在CT节点处运行振荡器波形,导致CT峰值电压的峰值。

UCC3802和UCC3809一次侧脉宽调制控制器