ADS5413点击型号即可查看芯片规格书

特征

-12位分辨率

-65-MSPS最大采样率

-2-Vpp差分输入范围

-3.3-V单电源操作

-1.8-V至3.3-V输出电源

-400兆瓦总功耗

-两种补码输出格式

-片上S/H与占空比调节电路

-内部或外部参考

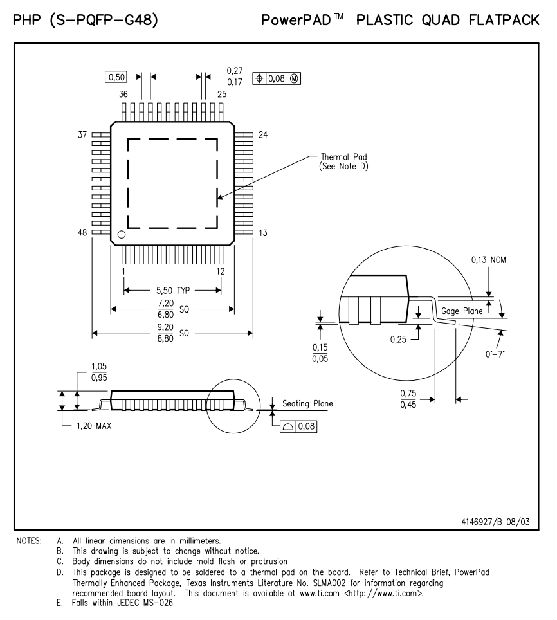

-带电源板的48针TQFP封装(7毫米x 7毫米机身尺寸)

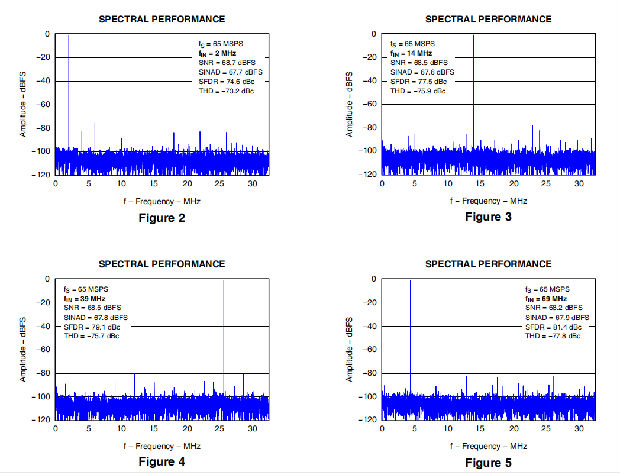

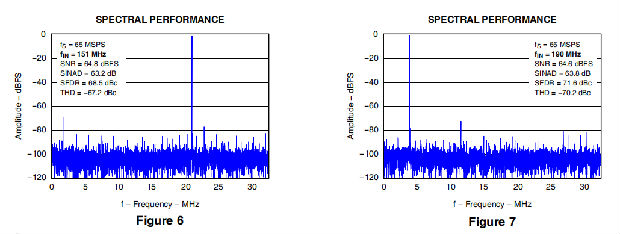

-65 MSPS和190 MHz输入下64.5-dBFS信噪比和72 dBc SFDR

-断电模式

-单端或差分时钟

-1-GHz−3-dB输入带宽

应用

-高中频采样接收器

-医疗成像

-便携式仪器

说明

ADS5413是一款低功耗、12位、65-MSPS、CMOS流水线模数转换器(ADC),可在单个3.3伏电源下工作,同时提供从1.8伏到3.3伏的数字输出电平选择。低噪声、高线性度和低时钟抖动使ADC非常适合高输入频率采样应用。片上占空比调整电路允许使用非50%的占空比。对于需要低抖动或异步采样的应用程序,这可以忽略。设备也可以使用单端或差分时钟进行计时,而不会改变性能。内部参考可以绕过使用外部参考,以适应应用的精度和低漂移要求。

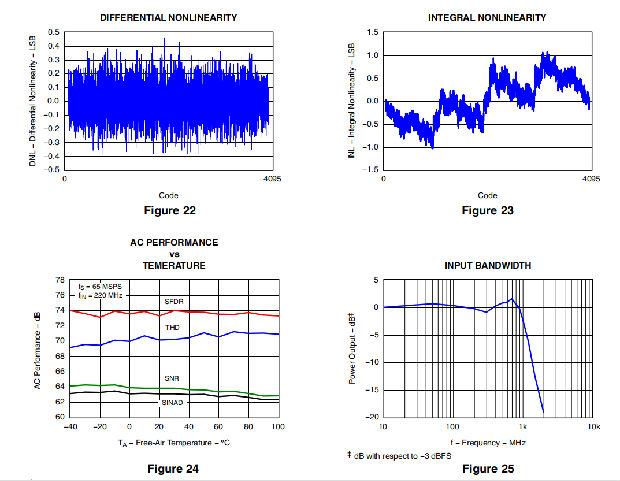

设备在整个温度范围内(-40°C至+85°C)指定。

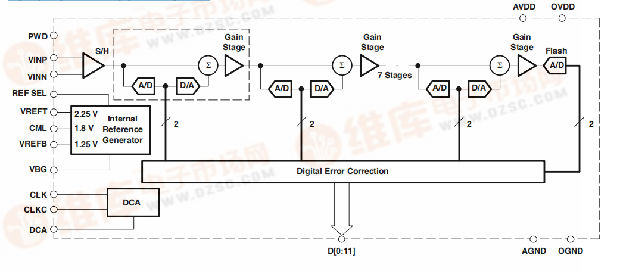

功能框图

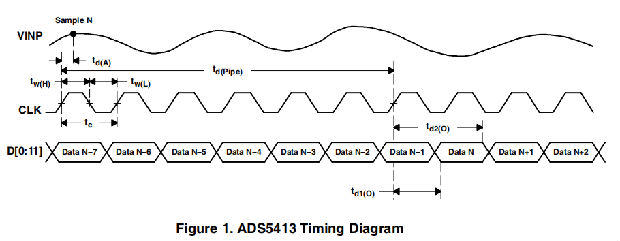

时序图

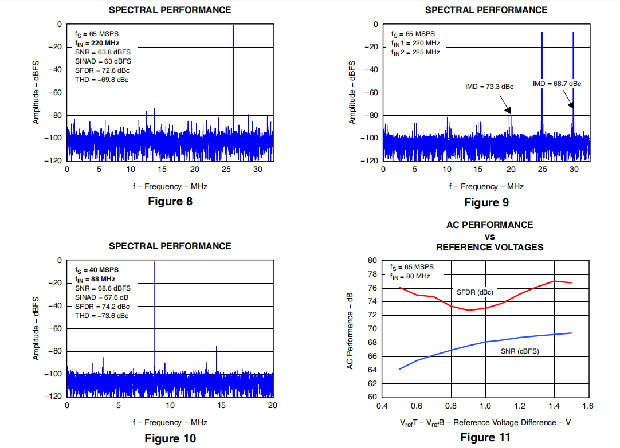

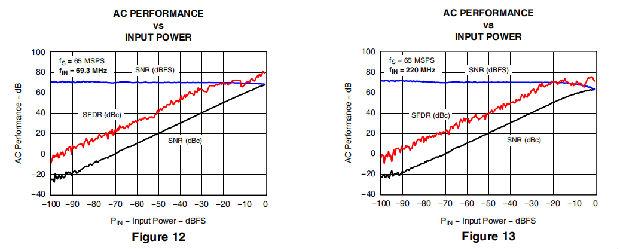

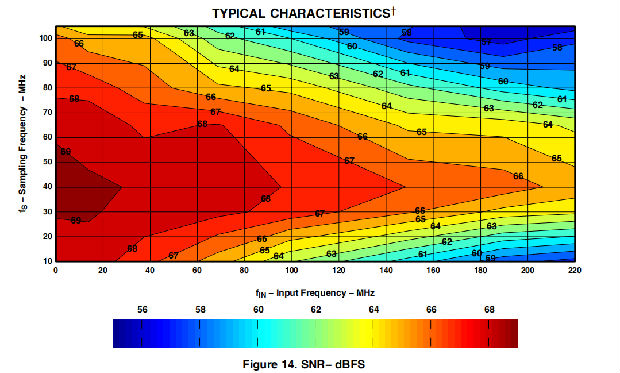

典型特征

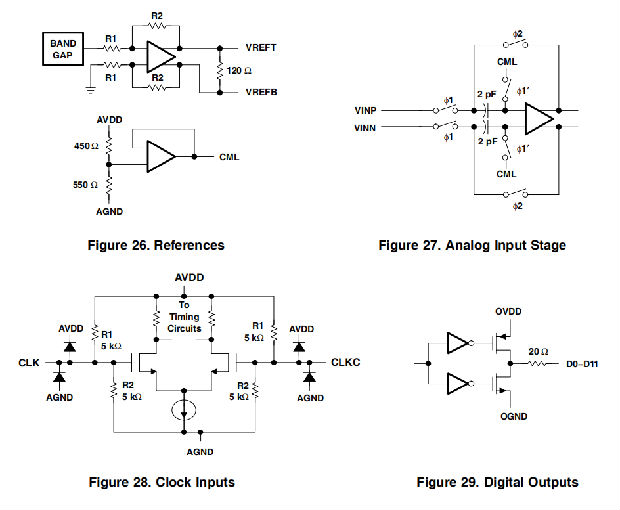

等效电路

应用程序信息

变频器运行

ADS5413是一个12位流水线ADC。它的低功耗(400兆瓦)在65毫秒/秒和高采样率是用先进的低压CMOS工艺建立的最先进的开关电容流水线结构实现的。ADS5413模拟核心由3.3V电源供电,消耗了大部分电源。为了增加接口灵活性,数字输出电源(OVDD)可以设置为1.6v到3.6v。ADC核心由10个流水线级和一个flash ADC组成。每个阶段每阶段产生1.5位。利用上升和下降的时钟边缘每半个时钟通过管道传播样本,总共六个时钟周期。

模拟输入

ADS5413的模拟输入由使用开关电容技术实现的差分跟踪保持放大器组成,如图27所示。这种差分输入拓扑,加上紧密匹配的电容器,产生高水平的交流性能,直至高采样和输入频率。

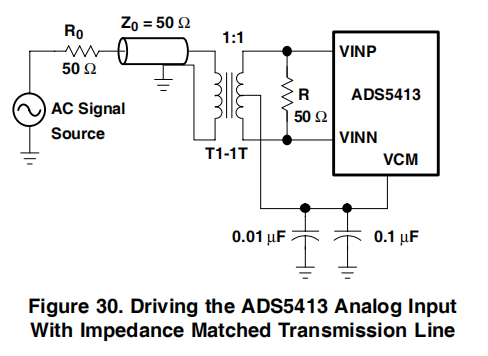

ADS5413要求每个模拟输入(VINP和VINM)外部偏置在内部电路(CML,引脚6)的共模电平上。

对于全刻度差分输入,输入信号的每条差分线(引脚3和4)在CML+(Vreft+Vrefb)/2和CML-(Vreft+Vrefb)/2之间对称摆动。最大摆幅由上参考电压(REFT)和下参考电压(REFB)之间的差值决定。总差动满标度输入摆幅为2(Vreft-Vrefb)。有关输入满标度的可能调整,请参阅参考电路部分。

虽然可以在单端配置中驱动输入,但是当模拟输入被差分驱动时,ADS5413获得最佳性能。图30中的电路显示了一种可能的配置。单端信号被馈送到主电源射频变压器。由于输入信号必须偏向内部电路的共模电压,因此来自ADS5413的共模(CML)基准连接到次级电路的中心抽头。为了确保稳定的低噪声CML基准,当CML输出通过0.1-μF和0.01-μF低电感电容器接地时,获得最佳性能。

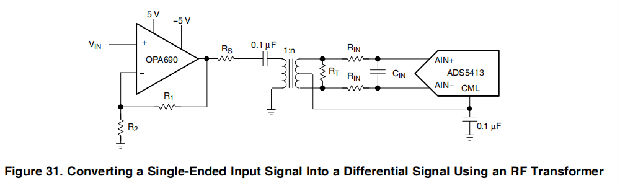

如果需要对输入的模拟信号进行缓冲或应用增益,则可以将单端放大器与射频变压器组合,如图31所示。Texas Instruments提供多种运算放大器,如THS3001/2、OPA847或OPA695,可根据应用情况进行选择。可以放置R和C以将源与ADC的开关输入隔离,并实现低通RC滤波器以限制ADC中的输入噪声。虽然不需要,但建议为这三个元件布置电路,以便在必要时对原型进行微调。然而,输入差分线之间的任何失配都会导致高输入频率下的性能下降,其主要特征是偶次谐波的增加。在这种情况下,应特别注意保持两个输入之间尽可能多的电气对称性。这包括做空R并让Cin unprophed离开。

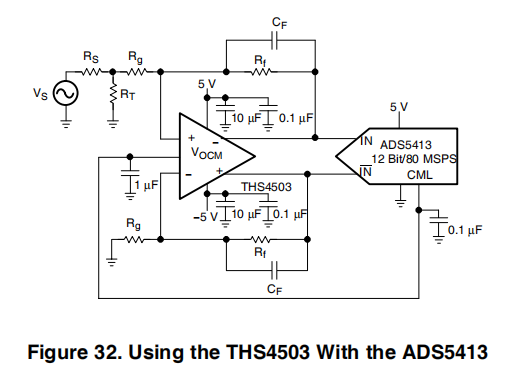

另一种可能性是使用差分输入/输出放大器,可以简化需要输入-直流耦合应用的驱动电路。这种放大器结构灵活(见图32),可用于单端到差分转换、信号放大和ADC前的滤波。

参考电路

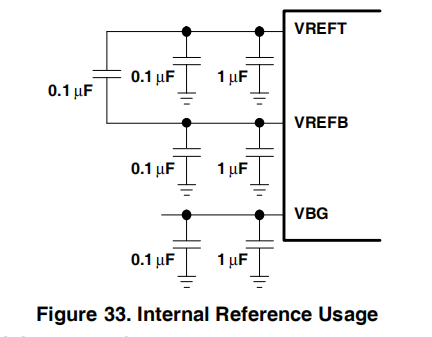

在设计中,ADS5413有自己的内部参考信号发生器,节省了外部电路。为了获得最佳性能,最好将VREFB和VREFT与接地连接,并在两个管脚之间并联一个1μF和一个0.1μF去耦电容器,以及一个0.1μF电容器(见图33)。带隙电压输出不是用于ADS5413外部的电压源。但是,应使用1-μF和0.01-μF并联电容器将其与接地分离。

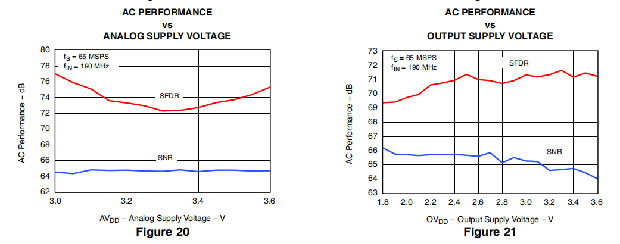

为了更大的设计灵活性,可以使用管脚48禁用内部参考。默认情况下,该引脚与70-kΩ下拉电阻器内部连接至接地,从而启用内部参考电路。将该引脚与AVDD连接可使内部参考发电机断电,允许用户为VREFT(引脚9)和VREFB(引脚8)提供外部电压。除了现在传输到外部电路的功耗降低(通常为56mw)之外,它还允许精确设置输入范围。为了进一步消除与外部因素(如温度或电源电压)的任何变化,用户可以直接访问内部电阻分压器,而无需任何中间缓冲。参考输入引脚的等效电路如图26所示。ADC的核心是为参考引脚之间的1v差而设计的。然而,用户可以使用这些管脚来设置不同的输入范围。图11显示了不同VREFT-VREFB电压设置下-1 dBFS采样率为65 MHz和80 MHz单音输入的SNR和SFDR的变化。

时钟输入

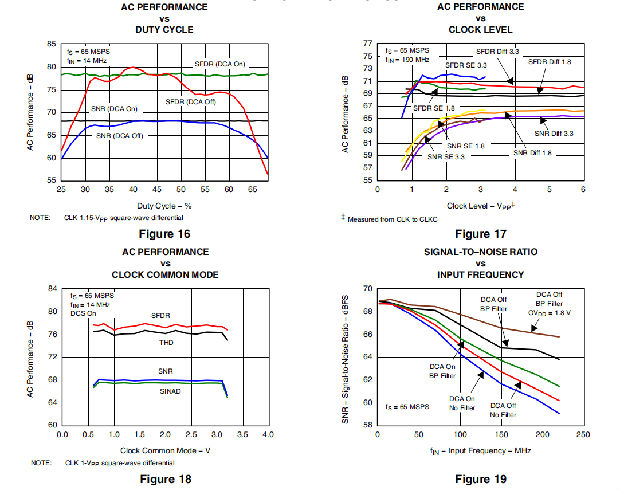

ADS5413时钟输入可以用差分时钟信号或单端时钟输入驱动,单端和差分输入配置之间的性能差别很小或没有差别(见图17)。时钟输入的共模在内部使用5-kΩ电阻器设置为AVDD/2(见图28)。

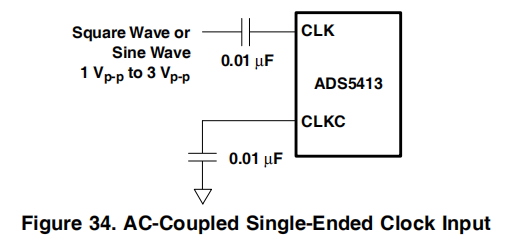

当使用单端时钟输入驱动时,最好使用0.01-μF电容器将CLKC输入接地(见图34),而CLK与0.01μF交流耦合至时钟源。

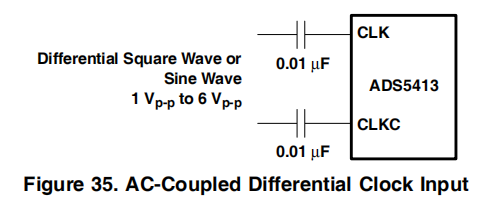

ADS5413时钟输入也可以差分驱动。在这种情况下,最好使用0.01-μF电容器将两个时钟输入连接到差分输入时钟信号(见图35)。差分输入摆幅可以在1V和6V之间变化,性能几乎没有下降(见图17)。

虽然建议使用交流耦合配置来设置时钟的共模,但是对于不能使用交流配置的情况,可以使用不同的共模来操作ADS5413。图18显示了ADS5413对不同时钟公共模式的性能。

ADS5413可以用正弦波或方波驱动。内部ADC核心使用时钟的两个边缘进行转换处理。这意味着理想情况下,应提供50%的占空比。然而,ADC包括车载占空比调节器(DCA),该调节器将可能不是50%的输入时钟占空比调节为50%的占空比,以供内部使用。默认情况下,该电路在内部启用(上拉电阻为70 kΩ),从而放宽外部时钟的设计规范。图16显示了两种情况下,在启用和禁用DCA的情况下,65 MHz时钟和14 MHz输入信号的ADC性能与时钟占空比的关系。然而,在某些情况下,用户可能更愿意禁用DCA。对于异步时钟,即当采样周期故意不恒定时,应禁用此电路。另一种情况是高输入频率采样。对于高输入频率,应提供低抖动时钟。从这个意义上说,我们建议带通滤波器的来源,从而提供一个正弦时钟占空比为50%。在这种情况下使用DCA是没有好处的,它会给内部时钟增加噪声,增加抖动,降低性能。图19显示了不同时钟方案的性能与输入频率的关系。最后,添加DCA会引入输入时钟和输出数据之间的延迟,更重要的是,该延迟随外部条件(如温度)的变化稍大。要禁用DCA,用户应将其接地。

断电

当掉电(引脚16)与AVDD连接时,该设备将其功耗降低到典型值23mw。将该引脚连接到GND或保持其未连接(提供一个内部70-kΩ下拉电阻器)可使设备工作。

数字输出

ADS5413输出格式为2s补码。通过将OVDD电压设置在1.6v和3.6v之间,可以调整输出的电压水平,从而允许直接与多个数字系列接口。为了获得更好的性能,客户应该选择应用程序中所需的较小的输出摆幅。为了提高性能,主要是在更高的输出电压摆幅配置上,建议在输出端增加一个串联电阻,限制峰值电流。此电阻器的最大值受应用程序的最大数据速率限制。通常值在0Ω和200Ω之间。此外,限制外部痕迹的长度也是一个好的做法。

所有的数据表图都是在最坏的情况下获得的,其中OVDD为3.3v。外部串联电阻为150Ω,负载为74AVC16244缓冲器,如评估板中使用的那样。在这种配置中,ADC输出的上升沿是5ns,这允许一个窗口捕获10.4ns的数据(不包括其他因素)。

规范的定义

模拟带宽

模拟带宽是模拟输入频率,在该频率下,基频的频谱功率(由FFT分析确定)相对于在低输入频率下测量的值降低3db。

孔径延迟

CLK命令上升沿50%点与模拟输入采样时刻之间的延迟。

孔径不确定性(抖动)

孔径延迟的采样-采样变化。

微分非线性

数字输出处任何单个LSB转换与模拟输入处理想1 LSB步的平均偏差。

积分非线性

传递函数与用最小二乘曲线拟合确定的最佳直线以1lsb的分数测量的参考线的偏差。

时钟脉冲宽度/占空比

脉冲宽度高是CLK脉冲保持逻辑1状态以达到额定性能的最小时间量;脉冲宽度低是CLK脉冲保持低状态的最小时间量。在给定的时钟速率下,这些规范定义了可接受的时钟占空比。

最大转换率

进行参数测试的时钟频率。

电源抑制比

输入偏移电压变化与电源电压变化的比率。

信噪比和失真(SINAD)

所有其他谱分量(包括谐波,但不包括直流电)之和的均方根信号振幅(设为满刻度以下1分贝)与均方根值之比。

信噪比(无谐波)

有效值信号振幅(在满标度以下1dB处设置)和所有其他谱分量之和的有效值之比,不包括前五次谐波和直流电。

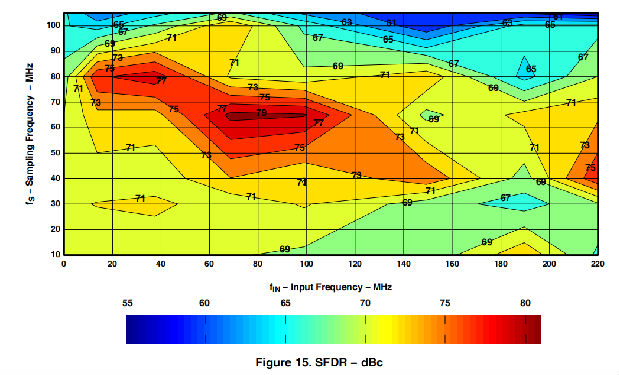

无杂散动态范围

峰值杂散频谱分量的均方根信号振幅与均方根值之比。峰值杂散分量可以是谐波,也可以不是谐波,并在dBc中报告。

双音互调失真抑制

输入音调的均方根值与dBc中报告的最差三阶互调产物的均方根值之比。