TFP401A点击型号即可查看芯片规格书

特点

支持最高165MHz的像素速率(包括60Hz时1080p和WUXGA)

符合数字视频接口(DVI)规范(一)真彩色,24位/像素,1670万色,每时钟1或2像素

用于最佳固定阻抗匹配的激光修剪内部终端电阻器

最多可容忍一个像素时钟周期的偏差

4×过采样

降低功耗–1.8 V核心操作,3.3 V I/O和电源(二)

使用时间交错像素输出减少地面反弹

使用TI PowerPAD,噪音低,功耗高™ 包装

采用TI 0.18-微米EPIC-5 CMOS工艺的先进技术

TFP401A具有HSYNC抖动抗扰性(三)

(1) 数字视觉接口规范(DVI)是由数字显示工作组(DDWG)开发的用于数字显示器高速数字连接的行业标准。

TPF401和TFP401A符合DVI规范版本。1.0分。

(2) TFP401/401A有一个内部电压调节器,从外部3.3 V电源提供1.8 V核心电源。

(3) TFP401A采用了额外的电路,通过引入

应用程序

高清电视

高清PC显示器

数字视频

高清投影仪

DVI/HDMI接收器(仅限HDMI视频)

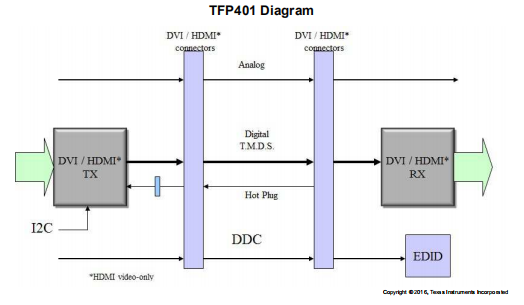

说明

德州仪器TFP401和TFP401A是TI PanelBus™ 平板显示器产品,端到端DVI 1.0兼容解决方案综合系列的一部分。TFP401/401A主要针对台式液晶显示器和数字投影仪,适用于任何需要高速数字接口的设计。

TFP401和TFP401A支持24位真彩色像素格式的高达1080p和WUXGA的显示分辨率。TFP401/401A提供了设计灵活性,可以驱动每个时钟一个或两个像素,支持TFT或DSTN面板,并提供了一个时间交错像素输出选项,以减少地面反弹。

werPAD先进的封装技术带来了一流的功耗、占地面积和超低接地电感。

TFP401和TFP401 a结合了PanelBus电路创新和TI先进的0.18微米EPIC-5cmos工艺技术,以及TI PowerPAD封装技术,实现了可靠、低功耗、低噪声、高速的数字接口解决方案。

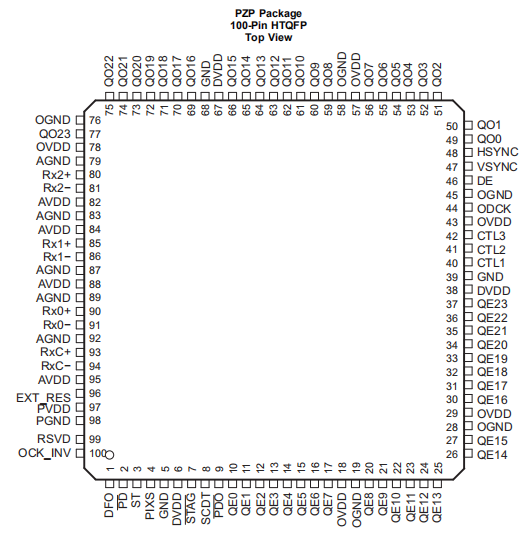

针配置和功能

概述

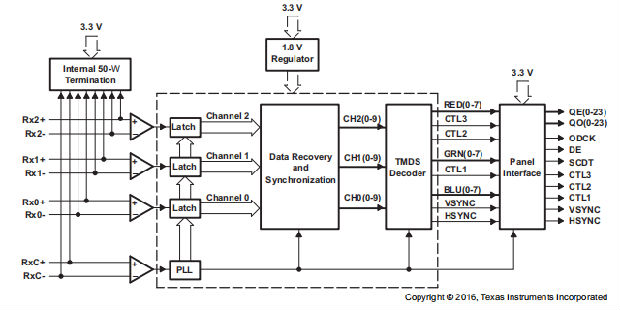

TFP401/401A是数字视觉接口(DVI)兼容的TMDS数字接收机,用于数字平板显示系统接收和解码TMDS编码的RGB像素数据流。在数字显示系统中,主机(通常是PC或工作站)包含TMDS兼容的发送器,该发送器接收24位像素数据以及适当的控制信号,并将其编码成适合通过双绞线传输到显示设备的高速低压差分串行比特流。显示设备通常是平板显示器,需要与TMDS兼容的接收器(如TI TFP401/401A)将串行比特流解码回源于主机的相同24位像素数据和控制信号。然后,该解码数据可直接应用于平板驱动电路以在显示器上产生图像。由于主机和显示器之间的距离可以达到或超过5米,因此最好采用像素数据的串行传输。为了支持最高达UXGA的现代显示分辨率,需要一个具有良好抖动和倾斜容忍度的高带宽接收器。

功能框图

特征描述

TMDS像素数据和控制信号编码

TMDS代表转换最小化差分信号。在给定的时间内,仅传输给定像素的两个可能TMDS字符中的一个。发射机保持对先前发送的1和0的运行计数,并发送使转换次数最小化的字符,以近似传输线的直流平衡。

三个TMDS通道用于在活动显示时间DE=高期间接收RGB像素数据。这三个通道还接收控制信号,HSYNC、VSYNC和用户定义的控制信号CTL[3:1]。这些控制信号在非活动显示或消隐期间接收。消隐时间是当DE=低时。表1将接收到的输入数据映射到DVI兼容系统中的相应TMDS输入信道。

TFP401/401A时钟和数据同步

TFP401/401A从具有等于像素时间tpix的周期的DVI发射机接收时钟参考。这个时钟的频率也被称为像素速率。由于Rx[2:0]上的TMDS编码数据包含每8位像素10位,因此Rx[2:0]串行比特率是像素率的10倍。例如,支持60hz刷新率的UXGA分辨率所需的像素速率为165mhz。TMDS串行比特率是像素率的10倍,即1.65gb/s。由于这种高速数字比特流在三个长距离(3-5米)的独立信道(或双绞线)上传输,数据流和输入参考时钟之间的相位同步无法保证。此外,三个数据通道之间的偏差也是常见的。TFP401/401A使用输入数据流的4×过采样方案,以实现与高达1-tpix信道对信道倾斜容限的可靠同步。由于反射和外部噪声源在时钟和数据线上累积的抖动也是高速串行数据传输的典型;因此,TFP401/401A设计具有高的抖动容限。

TFP401/401A的输入时钟由锁相环(PLL)调节以消除时钟的高频抖动。PLL提供四个不同相位的10×时钟输出,以定位和同步TMDS数据流(4×过采样)。在活动显示期间,像素数据被编码为过渡最小化,而在空白处,控制数据被编码为过渡最大化。符合DVI标准的发射机需要在最短时间段(128 tpix)内空白发射,以确保在接收机看到转换最大化码时有足够的时间进行数据同步。当数据传输最大化时,在空白期间进行同步,可确保可靠的数据位边界检测。对于三个输入信道中的每一个,与数据流的相位同步是唯一的,并且只要链路保持活跃就保持同步。

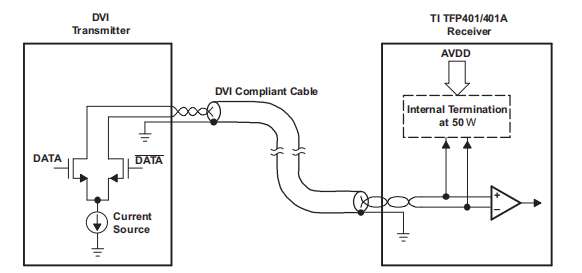

TFP401/401A TMDS输入电平和输入阻抗匹配

TFP401/401A接收器的TMDS输入具有固定的AVDD单端终端。TFP401/401A采用激光微调工艺进行内部优化,精确地将阻抗固定在50Ω。该设备在外部引脚上有或没有电阻器时正常工作,因此它与电流插座保持插入兼容。固定阻抗消除了外部电阻的需要,同时提供与标准50ΩDVI电缆的最佳阻抗匹配。

DVI发射器和TFP401/401A接收器连接的概念示意图。发射机通过电流源驱动双绞线,通常通过开漏式输出驱动器实现。与TFP401/401A输入处的电缆阻抗匹配的内部电阻器提供到AVDD的上拉。当然,当发射机断开且TFP401/401A DVI输入保持未连接时,TFP401/401A接收机输入向上拉至AVDD。TFP401/401A设计用于响应150 mV至1.56 V的差分信号波动,共模电压范围为(AVDD–300 mV)至(AVDD–37 mV)。

DVI钛TFP401/401A

发射机接收机

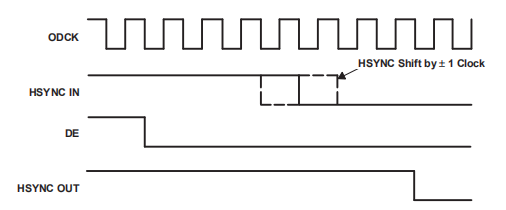

TFP401A具有HSYNC抖动抗扰性

市面上有几种DVI发射机在TMDS加密过程中会对传输的HSYNC和VSYNC信号产生抖动。HSYNC信号可以在任一方向上从标称移动一个像素位置(一个时钟),从而导致高达两个HSYNC移动周期。这种抖动会传递到DVI接收器,如果HSYNC的位置持续移动,接收器可能会失去对输入定时的跟踪,从而导致显示器上出现像素噪声。因此,具有HSYNC抖动抗扰性的DVI兼容接收机应用于所有可能连接到具有HSYNC抖动问题发射机的主机pc的显示器。

TFP401A集成了HSYNC再生电路,为这些不兼容发射机提供无缝接口。数据启用(DE)信号的位置总是相对于数据固定的,而与HSYNC的位置无关。TFP401A接收机使用DE和时钟信号来重建稳定的垂直和水平同步信号。该电路对接收器的HSYNC输出进行滤波,HSYNC被移到最近的第八位边界,产生关于数据的稳定输出,这确保了在显示定时控制器的输入端精确的数据同步。

此HSYNC再生电路对监视器是透明的,即使传输了

HSYNC是稳定的。例如,符合DVI 1.0标准的发射机(如TFP6422和TFP420)的PanelBus线不存在HSYNC抖动问题。TFP401A可在兼容或不兼容发射机上正常工作。相比之下,TFP401非常适合控制设计传输部分的客户,例如捆绑系统制造商和内部监视器使用(监视器和面板模块之间的DVI连接)。

设备功能模式

TFP401/401A操作模式

TFP401/401A通过向系统设计者提供可配置的选项或操作模式来支持不同的系统架构,从而提供了系统设计的灵活性和价值。表2概述了可以支持的各种面板模式以及适当的外部控制引脚设置。

输出驱动器断电

(PDO=低)。将PDO拉低会使所有输出驱动器(CTL1和SCDT除外)进入高阻抗状态。SCDT输出指示链路已禁用或链路未激活,可直接绑定到PDO输入,以在链路未激活或电缆断开时禁用输出驱动程序。PDO管脚上的内部上拉将TFP401/401A默认为正常的非断电输出驱动模式(如果未连接)。

驱动强度

(ST=高驱动强度为高,ST=低驱动强度为低)。TFP401/401A允许在数据、控制和ODCK输出上选择输出驱动强度。有关给定ST状态下IOH和IOL电流驱动器的值,请参阅直流电特性表。高输出驱动强度提供大约两倍于低输出驱动强度的驱动。

时间交错像素输出

此选项仅适用于2像素/时钟模式(PIXS=高)。设置STAG=low timestaggers为偶数和奇数像素输出,以减少来自电源的瞬时电流浪涌量。根据PCB的布局和设计,这有助于减少系统接地反弹和电源噪声。时间参差使得在2像素/时钟模式中,偶数像素从ODCK的锁存边缘延迟0.25tcip。(tcip是ODCK的时期。当处于2pixel/clock模式时,ODCK周期为2Tpix)。

根据输出负载、像素速率、面板输入架构和板成本的系统限制,TFP401/401A驱动强度和交错像素选项允许灵活地降低系统电源噪声、地面反弹和EMI。

电源管理

TFP401/401A提供了几个系统电源管理功能。

输出驱动器断电(PDO=低)是一种中间模式,提供多种用途。在该模式下,除SCDT和CTL1外的所有输出驱动器都被驱动到高阻抗状态,而其余的设备电路保持激活状态。

TFP401/401A掉电(PD=low)是一个完全的掉电,因为它关闭了数字核心、模拟电路和输出驱动器。所有输出驱动程序都处于Hi-Z状态。除PD输入外,所有输入均被禁用。在PD被拉高之前,TFP401/401A不响应任何数字或模拟输入。

PDO和PD都有内部上拉,因此如果不连接,它们会将TFP401/401A默认为正常工作模式。

同步检测

TFP401/401A提供一个输出SCDT来指示链路活动。TFP401/401A监视DE上的活动,以确定链路是否处于活动状态。当一百万(1e6)个像素时钟周期在DE上没有转换通过时,TFP401/401A将链路视为非活动的,并且SCDT被低驱动。当SCDT较低时,如果在1600像素时钟周期内检测到两个去转换,则认为链路处于活动状态,SCDT被拉高。

SCDT可用于向系统电源管理电路发送信号,以便在链路被视为非活动时启动系统断电。SCDT还可以直接连接到TFP401/401A PDO输入,以便在链路不活动时关闭输出驱动器。不建议使用SCDT驱动PD输入,因为一旦完全断电,模拟输入将被忽略,SCDT状态不会改变。最好使用外部系统电源管理电路来驱动局部放电。

申请信息

TFP401是DVI(数字视觉接口)兼容的数字接收机,用于数字平板显示系统接收和解码TMDS编码的RGB像素数据流。数字显示系统主机,通常是PC或工作站,包含一个DVI兼容的发射机,它接收24位像素数据和适当的控制信号,并将它们编码成适合通过双绞线传输到显示设备的高速低压差分串行比特流。显示设备,通常是平板显示器,将需要像TI TFP401这样的DVI兼容接收器来解码串行比特流,使其返回到源于主机的相同24位像素数据和控制信号。然后,该解码数据可直接应用于平板驱动电路以在显示器上产生图像。由于主机和显示器之间的距离可以达到或超过5米,因此,优先采用像素数据的串行传输。TFP401将支持高达UXGA的分辨率。

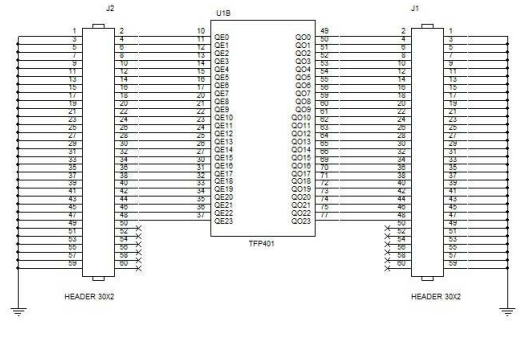

典型应用

数据和控制信号

从接收器输出的数据和控制信号的跟踪长度应尽可能保持接近相等。痕迹分离高度应为~5X。一般来说,如果可能的话,痕迹也应该小于2.8英寸(可以接受较长的痕迹)。延迟=85×SQRT ER,其中

ER=4.35

50%树脂的相对介电常数FR-4@1ghz

延迟=177 pS/英寸(1)

上升沿长度=TR(皮秒)÷延迟,其中

TR=3纳秒

=3000 ps÷177 ps/英寸

=16.9英寸(2)

上升沿长度÷6=集中电路的最大轨迹长度,其中

16.9÷6=2.8英寸(3)

数据和控制信号设计

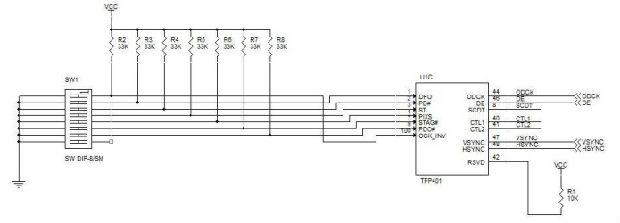

配置选项

TFP401可以根据所需的输出格式配置为多种模式,例如1字节/时钟、2字节/时钟、下降/上升时钟边缘。您可以为将来的配置更改留下占位符

配置选项设计

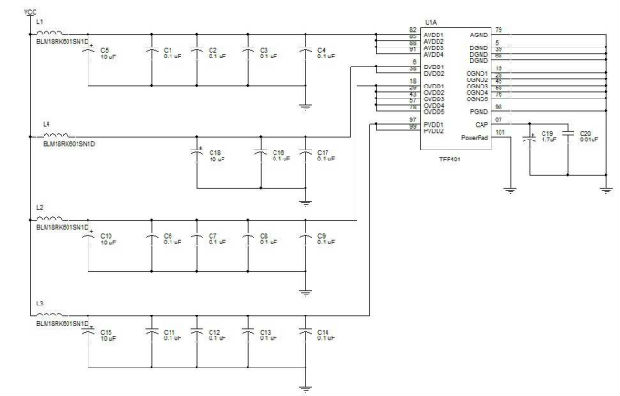

电源去耦数字、模拟和PLL电源必须相互分离,以避免PLL和核心上的电气噪声

电源解耦设计

应用曲线

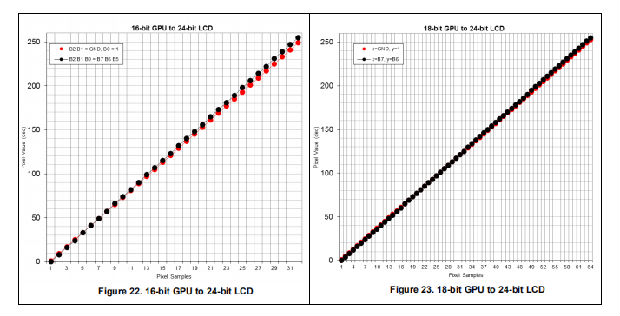

有时面板不支持与图形处理器单元(GPU)相同的格式。在这些情况下,用户必须决定如何连接未使用的位。图22和图23显示了18位GPU和24位LCD之间的不匹配,其中“x”和“y”表示面板的2 LSB。

电源建议

使用实心接地平面,并将接地平面与尽可能多的过孔连接在一起。这将为电流提供一条理想的返回路径。每个电源应位于单独的分离电源平面上,每个电源平面应尽可能大的面积。用通孔将PanelBus接收器的电源和接地针脚以及所有旁路盖连接到适当的电源或接地平面。过孔应尽可能的厚和短,目标是减少电感。

在每个DVD设备引脚(引脚6、38、67)和接地之间尽可能靠近地放置一个0.01 uF电容器。应在电源和0.01 uF电容器之间放置22 uF钽电容器。在电源和22 uF电容器之间应使用铁氧体磁珠。DVD光盘:

在每个OVDD设备引脚(引脚18、29、43、57、78)和接地之间尽可能靠近地放置一个0.01 uF电容器。应在电源和0.01 uF电容器之间放置22 uF钽电容器。在电源和22 uF电容器之间应使用铁氧体磁珠。出生日期:

在每个AVDD设备引脚(引脚82、84、88、95)和接地之间尽可能靠近地放置一个0.01 uF电容器。应在电源和0.01 uF电容器之间放置22 uF钽电容器。在电源和22 uF电容器之间应使用铁氧体磁珠。平均日:

将三个0.01 uF电容器尽可能平行放置在PVDD装置引脚(引脚97)和接地之间。应在电源和0.01 uF电容器之间放置22 uF钽电容器。在电源和22 uF电容器之间应使用铁氧体磁珠。PVCC公司:

布局指南

层叠

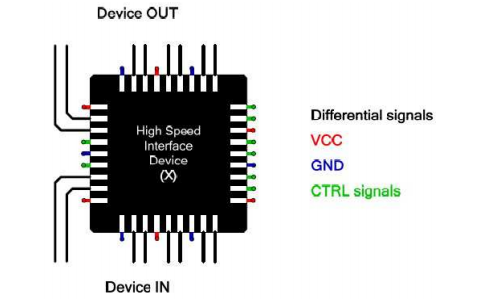

德州仪器高速接口(HSI)设备的引脚具有差分信号对,其余信号包括供电轨、VCC和接地,以及控制引脚等低速信号。例如,假设设备X是中继器/re驱动器,因此其输入和输出都是高速差分信号。这些指导原则可应用于其他高速设备,如驱动器、接收器、多路复用器等。完成低EMI PCB设计至少需要四层。层叠加应按以下顺序(自上而下):高速差分信号层、地平面、电源平面和控制信号层。

层叠

指南(续)

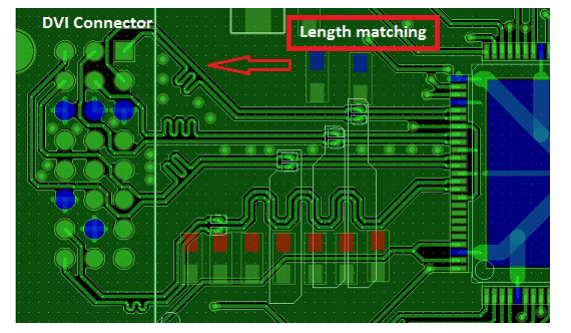

12.1.2路由高速差分信号记录道(RxC-,RxC+,Rx0-,Rx0+,Rx1-,Rx1+,Rx2-,Rx2+)

应控制跟踪阻抗以获得最佳性能。每对差分对的长度应相等,对称,对地阻抗应相等,线间距为2X至4X高。4倍高度的差分迹线分离产生约6%的串扰(6%对阻抗的影)。建议差分跟踪布线应并排进行,尽管差分跟踪紧密耦合在一起并不重要,因为在PCB跟踪上无法实现紧密耦合。PCBs上的典型比率仅为20-50%,99.9%是一条平衡良好的双绞线。

每个差分记录道应尽可能短(最好<2“),不带90”角。这些高速传输轨迹应位于第1层(顶层)。RxC-,RxC+,Rx0-,Rx0+,Rx1-,Rx1+,Rx2-,Rx2+信号都是直接从DVI连接器引脚到设备的,不需要外部组件。

DVI连接器

清除连接器插脚的孔时,插脚之间应留有空间,以便通过插脚区域进行连续接地。在信号引脚通孔周围的接地平面上留有足够的间距,但是,在通孔之间留有足够的铜,以允许接地电流在通孔之间流动。避免在整个连接器周围形成一个大的接地平面槽,最大限度地减小通孔电容是目标。

布局示例

DVI连接器跟踪匹配:

DVI连接器布线

示例(续)保持数据线尽可能远离彼此。

数据线路由

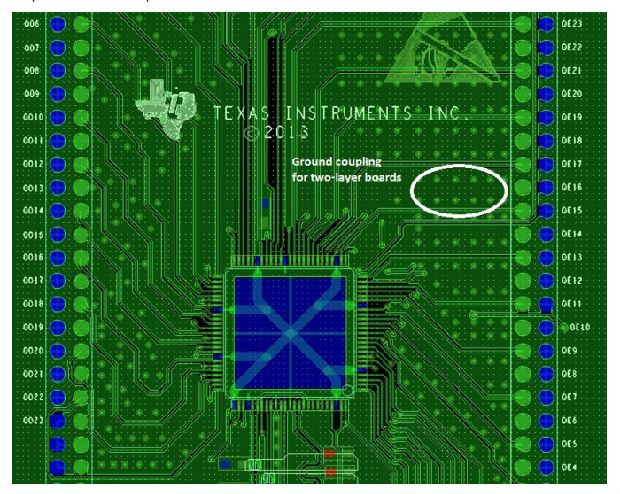

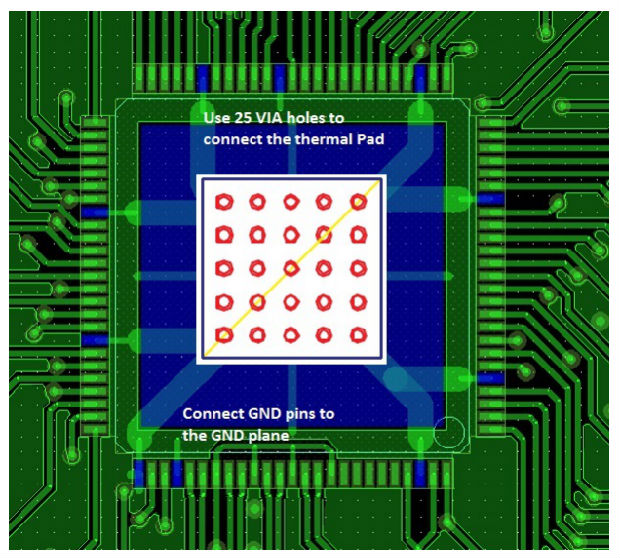

示例(续)将隔热垫接地。

商标

PowerPAD、PanelBus是德州仪器的商标。

所有其他商标均为其各自所有者的财产。

静电放电注意事项

这些设备具有有限的内置ESD保护。在储存或搬运过程中,导线应短接在一起,或将装置放置在导电泡沫中,以防止静电损坏MOS栅极。

术语表

SLYZ022-TI词汇表。

本词汇表列出并解释了术语、首字母缩略词和定义。

机械、包装和订购信息

以下页面包括机械、包装和可订购信息。此信息是指定设备可用的最新数据。本资料如有更改,恕不另行通知,也不作修改。有关此数据表的基于浏览器的版本,请参阅左侧导航。

TI PowerPAD 100-TQFP组件

TFP401/401A封装在TI的热增强PowerPAD 100-TQFP封装中。电源板组件为14 mm×14 mm×1 mm TQFP外形,引线间距为0.5 mm。PowerPAD软件包有一个特别设计的模具安装板,与相同外形的典型TQFP软件包相比,它提供了更好的热性能。TI 100-TQFP电源板封装提供了一个背面焊接面,直接连接到模具安装板,以增强热传导。TFP401/401A的背面不需要焊接到应用板上,因为在没有焊接的情况下,器件的功耗在封装能力范围内。

出于电气考虑,建议将设备背面焊接到PCB接地平面。

由于模垫与芯片基板电连接,因此与芯片接地相连,因此将电源板背面连接至PCB接地平面有助于改善EMI、接地反弹和电源噪声性能。