ADSP-21469点击型号即可查看芯片规格书

摘要

高性能32位/40位浮点处理器;为高性能音频处理而优化;单指令、多数据(SIMD)计算建筑学;5兆片上RAM,4兆片上ROM;工作频率高达450兆赫;适用于汽车应用;与SHARC家族所有其他成员兼容的代码,可用于独特的以音频为中心的外围设备,如数字应用接口内容保护协议),串行端口,精密时钟发电机,S/PDIF收发器,异步采样率转换器、输入数据端口等。

一般说明

ADSP-21467/ADSP-21469 SHARC处理器是具有模拟设备的超级哈佛架构的DSP的SIMD SHARC系列的成员。这些处理器的源代码与ADSP-2126x、ADSP-2136x、ADSP-2137x和ADSP-2116x DSP兼容,并与第一代ADSP-2106x SHARC处理器在SISD(单指令、单数据)模式下兼容。这些32位/40位浮点处理器针对高性能音频应用进行了优化,具有大型片上SRAM、多条内部总线以消除I/O瓶颈,以及创新的数字应用程序/外围接口(DAI/DPI)。

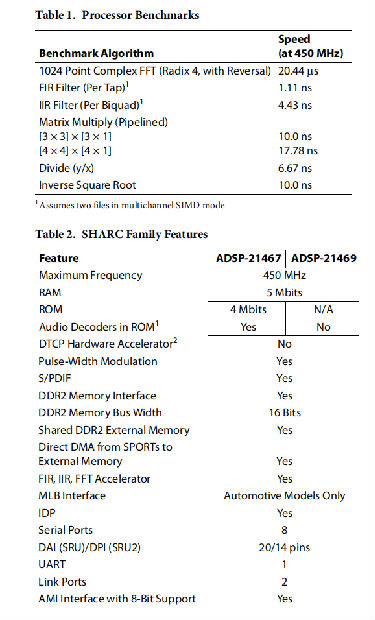

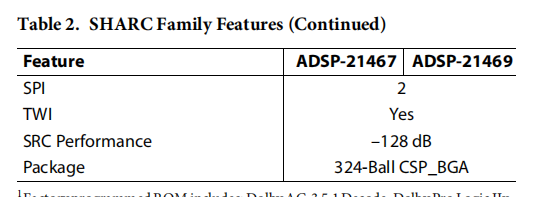

表1显示了处理器的性能基准,表2显示了产品的特性。

1、工厂编程ROM包括:杜比AC-3 5.1解码、杜比Pro逻辑IIx、杜比智能混频器(eMix)、杜比音量后处理器、杜比耳机v2、DTS Neo:6和解码、DTS 5.1解码(96/24)、数学表/旋转因子/256和512 FFT和ASRC。

2、有关支持DTCP的ADSP-21467/ADSP-21469处理器的可用性的更多信息,请与您当地的模拟设备销售办事处联系。

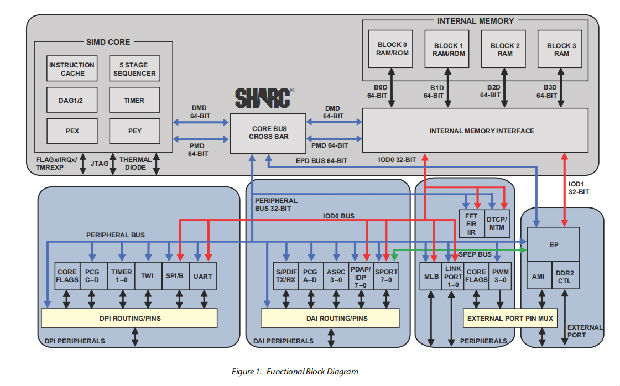

图1显示了构成处理器的两个时钟域。核心时钟域包含以下功能:

•两个处理元件(PEx、PEy),每个元件都有一个ALU、乘法器、移位器和数据寄存器文件

•数据地址生成器(DAG1、DAG2)

•带指令缓存的程序序列器

•一个带引脚的周期间隔计时器

•PM和DM总线能够在每个核心处理器周期支持内存和核心之间的2×64位数据传输

•片上SRAM(5 Mbits)

•片上掩模可编程ROM(4mbits)

•JTAG测试访问端口,用于模拟和边界扫描。JTAG通过用户断点提供软件调试,允许灵活的异常处理。

图1还显示了外围时钟域(也称为I/O处理器),它包含以下功能:

•用于32位数据传输的IOD0(外围DMA)和IOD1(外部端口DMA)总线

•核心连接的外围和外部端口总线

•带有AMI和DDR2控制器的外部端口

•4个用于脉宽调制控制的单元

•1个用于内部到内部存储器传输的MTM单元

•数字应用接口,包括四个精密时钟发生器(PCG)、一个用于串行和并行互连的输入数据端口(IDP)、一个S/PDIF接收器/发射器、四个异步采样率转换器、八个串行端口、一个灵活的信号路由单元(DAI SRU)。

•数字外围接口,包括两个定时器、一个2线接口、一个UART、两个串行外围接口(SPI)、2个精密时钟发生器(PCG)和一个灵活的信号路由单元(DPI SRU)。

如第1页图1所示,处理器使用两个计算单元,在一系列DSP算法上比以前的SHARC处理器提供显著的性能提升。使用SIMD计算硬件,处理器可以在450mhz下运行2.7gflops,在400mhz下运行2.4gflops。

家庭核心架构

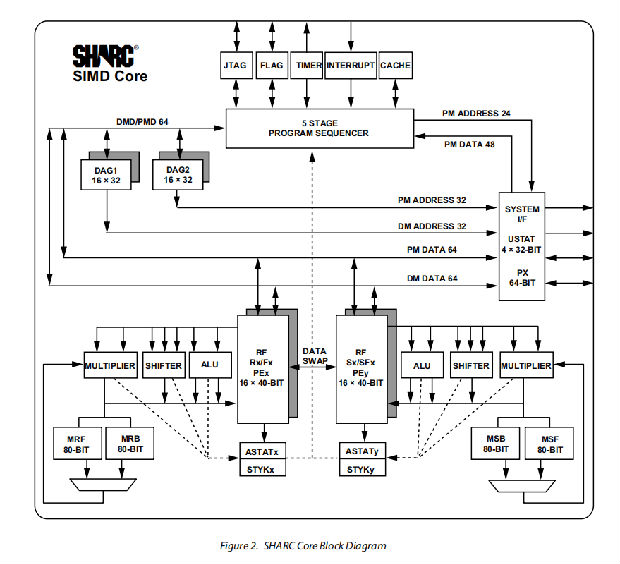

这些处理器在汇编级与ADSP-2137x、ADSP-2136x、ADSP-2126x、ADSP-21160和ADSP-21161以及第一代ADSP-2106x SHARC处理器代码兼容。ADSP-21467/ADSP-21469处理器与ADSP-2126x、ADSP-2136x、ADSP-2137x和ADSP-2116x SIMD SHARC处理器共享体系结构功能,如图2所示并在以下各节中详细说明。

SIMD计算引擎

处理器包含两个计算处理元素,它们作为单个指令、多数据(SIMD)引擎运行。处理元素称为PEX和PEY,每个元素都包含一个ALU、乘法器、移位器和寄存器文件。PEX始终处于活动状态,可通过在MODE1寄存器中设置PEYEN模式位来启用PEY。启用此模式时,在两个处理元素中执行相同的指令,但每个处理元素对不同的数据进行操作。该体系结构能够有效地执行数学密集型的DSP算法。

进入SIMD模式也会影响在存储器和处理元件之间传输数据的方式。在SIMD模式下,需要两倍的数据带宽来维持处理单元中的计算操作。由于这一要求,进入SIMD模式也会使内存和处理元素之间的带宽增加一倍。在SIMD模式下使用DAGs传输数据时,每次访问内存或寄存器文件时都会传输两个数据值。

独立的并行计算单元

在每个处理单元中都有一组计算单元。计算单元包括算术/逻辑单元(ALU)、乘法器和移位器。这些单元在一个周期内执行所有操作。每个处理单元中的三个单元并行排列,最大化计算吞吐量。单个多功能指令执行并行运算单元和乘法器操作。在SIMD模式下,并行ALU和乘法器操作同时发生在两个处理单元中。这些计算单元支持IEEE 32位单精度浮点、40位扩展精度浮点和32位定点数据格式。

计时器

一种能产生周期性软件中断的核心定时器。核心计时器可以配置为使用标志3作为计时器过期信号。

数据寄存器文件

通用数据寄存器文件包含在每个处理元素中。寄存器文件在计算单元和数据总线之间传输数据,并存储中间结果。这些10端口、32寄存器(16个主寄存器、16个次寄存器)寄存器文件,结合处理器增强的哈佛体系结构,允许计算单元和内部内存之间无约束的数据流。PEX中的寄存器称为R0-R15,PEY中的寄存器称为S0-S15。

上下文切换

许多处理器的寄存器都有辅助寄存器,可以在为快速上下文切换提供中断服务期间激活。寄存器文件中的数据寄存器、DAG寄存器和乘法器结果寄存器都有辅助寄存器。主寄存器在复位时激活,而辅助寄存器由模式控制寄存器中的控制位激活。

通用寄存器

这些寄存器可用于一般用途的任务。这个USTAT(4)寄存器允许对核心的所有系统寄存器(控制/状态)进行简单的位操作(设置、清除、切换、测试、异或)。

数据总线交换寄存器(PX)允许在64位PM数据总线和64位DM数据总线之间,或在40位寄存器文件和PM/DM数据总线之间传递数据。这些寄存器包含处理数据宽度差的硬件。

指令和四个操作数的单周期获取

处理器采用增强的哈佛架构,其中数据存储器(DM)总线传输数据,程序存储器(PM)总线传输指令和数据(见图2)。通过其独立的程序和数据存储总线以及片上指令缓存,处理器可以在一个周期内同时获取四个操作数(每个数据总线两个操作数)和一个指令(从缓存)。

指令缓存

处理器包含一个片上指令缓存,它支持三总线操作来获取一条指令和四个数据值。缓存是选择性的,只缓存取数与PM总线数据访问冲突的指令。该缓存允许核心、循环操作(如数字滤波器乘法累加)和FFT蝶形处理的全速执行。

支持零开销硬件循环缓冲区的数据地址生成器

这两个数据地址生成器(DAG)用于间接寻址和在硬件中实现循环数据缓冲区。圆形缓冲器允许有效编程延迟线和数字信号处理所需的其他数据结构,通常用于数字滤波器和傅里叶变换。处理器的两个DAG包含足够的寄存器,可以创建多达32个循环缓冲区(16个主寄存器集,16个辅助寄存器集)。DAG自动处理环绕的地址指针,减少开销,提高性能,并简化实现。循环缓冲区可以在任何内存位置开始和结束。

灵活指令集

48位指令字可容纳各种并行操作,以实现简洁的编程。例如,处理器可以有条件地在两个处理元素中执行乘法、加法和减法,同时在一条指令中从内存中分支和获取最多四个32位值。

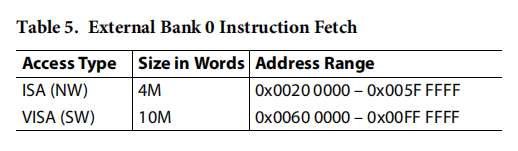

可变指令集体系结构(VISA)

除了支持以前SHARC处理器的标准48位指令外,这些处理器还支持16位和32位的新指令。这个称为可变指令集体系结构(VISA)的特性将多余/未使用的位放入48位指令中,以创建更高效、更紧凑的代码。程序序列器支持从内部和外部DDR2内存获取这些16位和32位指令。需要使用VISA选项构建源模块,以便代码生成工具创建这些更有效的操作码。

片上存储器

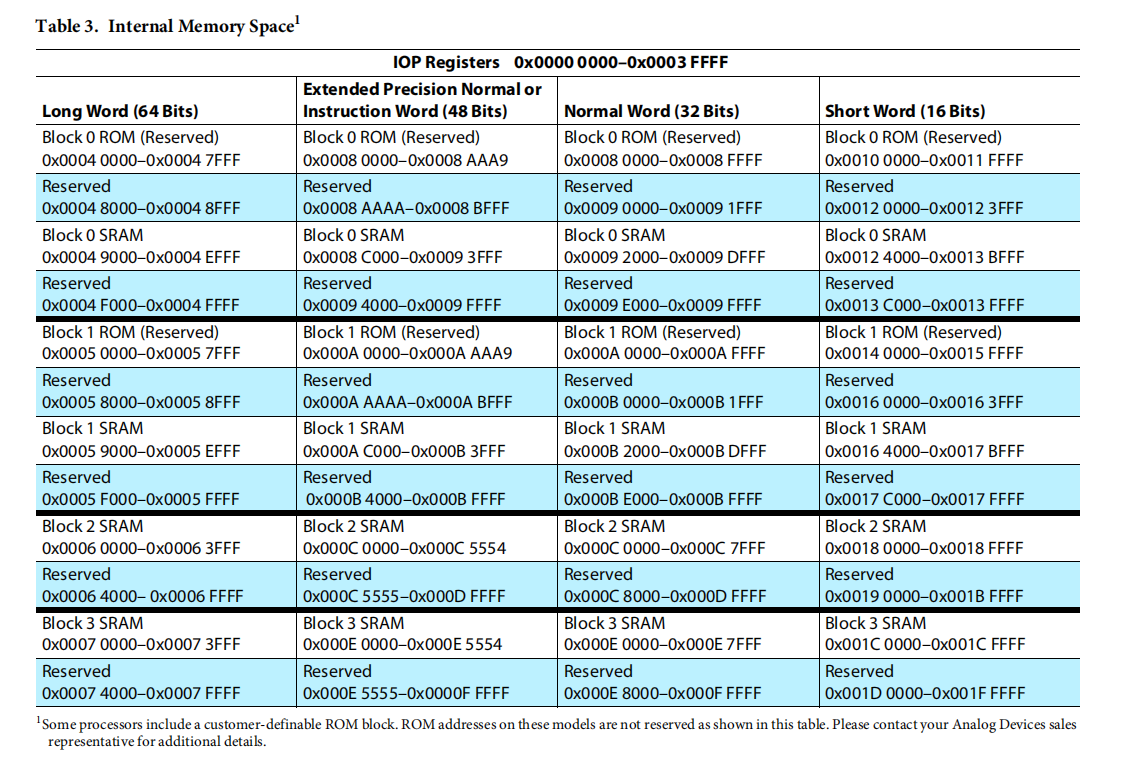

处理器包含5兆内存。每个块可以配置为不同的代码和数据存储组合(见表4)。每个内存块支持核心处理器和I/O处理器的单周期独立访问。内存体系结构与其单独的onchip总线相结合,允许在一个周期内从核心和I/O处理器进行两次数据传输。

处理器的SRAM可以配置为最多160k字的32位数据、320k字的16位数据、106.7k字的48位指令(或40位数据)或最大为5 Mbits的不同字大小的组合。所有内存都可以作为16位、32位、48位或64位字访问。支持16位浮点存储格式,有效地将可存储在芯片上的数据量加倍。32位浮点和16位浮点格式之间的转换在一条指令中执行。虽然每个存储块可以存储代码和数据的组合,但是当一个块使用DM总线存储数据进行传输,而另一个块使用PM总线存储指令和数据进行传输时,访问效率最高。

使用DM总线和PM总线,其中一条总线专用于一个内存块,确保两次数据传输的单周期执行。在这种情况下,指令必须在缓存中可用。

表3中的内存映射显示处理器的内部内存地址空间。48位空间部分描述了这个地址范围对于检索48位内存的指令是什么样的。32位部分描述此地址范围对于检索32位内存的指令的外观。

片上存储器带宽

内部内存体系结构允许程序同时对四个块中的任何一个进行四次访问(假设没有块冲突)。总带宽由DMD和PMD总线(2×64位,CCLK速度)和IOD0/1总线(2×32位,PCLK速度)实现。

非安全只读存储器

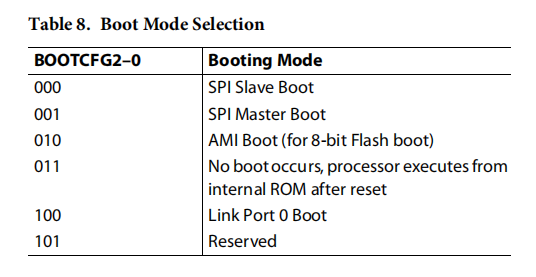

对于非安全ROM,使用BOOTCFG管脚选择引导模式,如第10页表8所示。在这种模式下,仿真始终处于启用状态,IVT被放置在内部RAM上,BOOTCFGx=011的情况除外。

基于ROM的安全性

ROM安全特性提供硬件支持,通过在启用时防止未经授权读取内部代码来保护用户软件代码。使用此功能时,处理器不引导加载任何外部代码,只从内部ROM执行。此外,处理器不能通过JTAG端口自由访问。相反,必须通过JTAG或测试访问端口扫描的唯一64位密钥将分配给每个客户。

数字传输内容保护

DTCP规范定义了一种加密协议,用于保护音频娱乐内容在穿越高性能数字总线(如IEEE 1394标准)时免受非法复制、截取和篡改。只有通过另一个经批准的副本保护系统(如DVD内容加扰系统)传送到源设备的合法娱乐内容才受此副本保护系统的保护。

家庭周边建筑

处理器包含一组丰富的外围设备,支持多种应用,包括高质量音频、医学成像、通信、军事、测试设备、3D图形、语音识别、马达控制、成像和其他应用。

外部端口

外部端口接口支持通过核心和DMA访问外部存储器。外部存储器地址空间分为四组。任何银行都可以编程为异步或同步存储器。外部端口由以下模块组成。

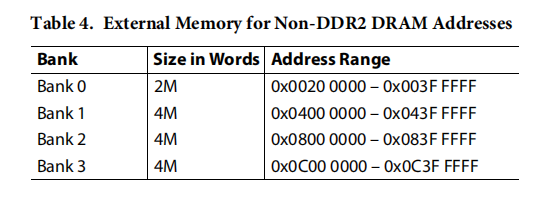

•异步存储器接口,可与SRAM、闪存和其他符合标准异步SRAM访问协议的设备进行通信。AMI支持0银行的2万字外部存储器和1银行、2银行和3银行的4万字外部存储器。

•DDR2 DRAM控制器。可支持最大为2 GB的外部内存设备。

•仲裁逻辑,用于协调通过外部端口在内部和外部存储器之间的核心和DMA传输。

外部存储器

处理器上的外部端口为各种工业标准存储设备提供了高性能、无胶接口。外部端口可用于通过其单独的内部DDR2存储器控制器与同步和/或异步存储器设备接口。16位DDR2 DRAM控制器连接到工业标准的同步DRAM设备,而第二个8位异步内存控制器用于连接到各种内存设备。四个内存选择管脚允许多达四个独立的设备共存,支持同步和异步设备类型的任何所需组合。非DDR2 DRAM外部存储器地址空间如表4所示。

对外部存储器的SIMD访问

DDR2控制器支持64位EPD(外部端口数据总线)上的SIMD访问,允许在正常字空间(NW)中访问PEy单元上的互补寄存器。这提高了性能,因为在SISD模式下不需要显式加载免费寄存器。

VISA和ISA访问外部存储器

DDR2控制器还支持VISA代码操作,因为VISA指令是压缩的,所以减少了内存负载。此外,总线取数减少,因为在最佳情况下,一个48位取数包含三个有效指令。还支持从传统的ISA操作执行代码。请注意,无论VISA/ISA如何,代码执行仅受银行0的支持。表5显示了在每种模式下获取指令的地址范围。

享外部存储器

处理器支持与其他ADSP-2146x处理器连接到公共共享外部DDR2内存,以创建共享外部总线处理器系统。这种支持包括:

•共享外部总线的分布式片上仲裁

•固定和旋转优先总线仲裁

•总线超时逻辑

•总线锁

多个处理器可以共享外部总线,而无需额外的仲裁逻辑。仲裁逻辑包含在芯片上,允许最多连接两个处理器。第14页的表10提供了多处理器系统中使用的管脚的说明。

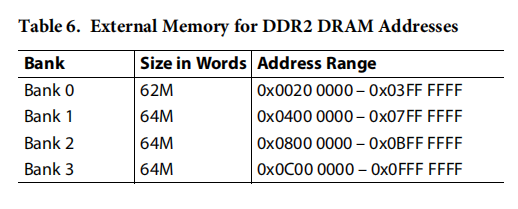

DDR2支持

处理器支持16位DDR2接口,最高工作频率为核心时钟的一半。支持从外部内存执行。可支持最大为2 GB的外部内存设备。

DDR2 DRAM控制器

DDR2 DRAM控制器提供一个16位接口,最多可连接四组工业标准DDR2 DRAM设备。完全符合DDR2 DRAM标准,每个银行都可以有自己的内存选择行(DDR2 CS3–DDR2 CS0),并且可以配置为包含32 MB到256 MB的内存。DDR2 DRAM外部内存地址空间如表6所示。

一组可编程定时参数可用于配置DDR2 DRAM存储组以支持内存设备。

请注意,显示的外部存储库地址是用于正常字(32位)访问的。如果48位指令和32位数据都放在同一个外部存储库中,则在映射它们时必须小心,以避免重叠。

异步内存控制器

异步内存控制器为多达四组独立的内存或I/O设备提供可配置接口。每个存储组都可以用不同的定时参数独立编程,从而能够连接到各种各样的存储设备,包括SRAM、Flash和EPROM,以及与标准存储控制线接口的I/O设备。第0列占用2个字的窗口,而第1、2和3列占用处理器地址空间中的4个字的窗口,但是,如果没有完全填充,这些窗口就不会被内存控制器逻辑设置为连续的。

外部端口吞吐量

基于400MHz时钟的外部端口的吞吐量,AMI为66M字节/秒,DDR2为800M字节/秒。

链接端口

两个8位宽的链路端口可以连接到其他DSP或外围设备的链路端口。链路端口是具有八条数据线、一条确认线和一条时钟线的双向端口。链路端口可以在166兆赫的最大频率下工作。

媒体B

该汽车模型有一个MLB接口,允许处理器作为媒体本地总线设备运行。它包括对3针和5针媒体本地总线协议的支持。它支持高达1024fs(49.25M位/秒,FS=48.1khz)的速度和高达31个逻辑通道,每个媒体本地总线帧最多有124字节的数据。

MLB接口支持MOST25和MOST50数据速率。不支持同步传输模式。

脉冲宽度调制

脉冲宽度调制模块是一种灵活的、可编程的脉冲宽度调制波形发生器,可编程以产生与电机和发动机控制或音频功率控制相关的各种应用所需的开关模式。PWM发生器可以产生中心对准或边缘对准的PWM波形。此外,它还可以在成对模式下的两个输出端上产生互补信号,或在非成对模式下产生独立信号(适用于一组四个脉冲宽度调制波形)。当产生中心对准的PWM波形时,PWM发生器能够在两种不同的模式下工作:单更新模式或双更新模式。

整个PWM模块有四组,每组四个PWM输出。因此,该模块总共产生16个PWM输出。每个脉冲宽度调制组在四个脉冲宽度调制输出端产生两对脉冲宽度调制信号。

数字应用接口(DAI)

数字应用接口(DAI)提供将各种外围设备连接到任何DAI引脚(DAI_P20–1)的能力。

程序使用信号路由单元(SRU)进行这些连接,图1所示。

SRU是一个矩阵路由单元(或多路复用器组),它使DAI提供的外围设备能够在软件控制下互连。这使得通过使用比不可配置的信号路径更大的一组算法,可以在更广泛的应用中容易地使用与DAI相关的外围设备。

DAI包括以下各节中描述的外围设备。

串行端口

处理器具有八个同步串行端口,为各种数字和混合信号外围设备(如模拟设备的AD183x系列音频编解码器、ADC和DAC)提供廉价接口。串行端口由两条数据线、一个时钟和帧同步组成。数据线可以编程为发送或接收,并且每个数据线都有一个专用的DMA信道。

当所有八个运动都启用时,串行端口最多可支持16个音频数据的发送或16个接收DMA通道,或每帧128个通道的四个全双工TDM流。

串行端口以fPCLK/4的最大数据速率运行。串行端口数据可以通过专用的DMA通道自动地在片上存储器/外部存储器之间传输。每个串行端口都可以与另一个串行端口一起工作,以提供TDM支持。一个运动提供两个发射信号,而另一个运动提供两个接收信号。帧同步和时钟是共享的。

串行端口以五种模式工作:

•标准的数字信号处理器串行模式

•多信道(TDM)模式

•I2S模式

•压缩I2S模式

•左对齐模式

S/PDIF兼容数字音频接收器/发射器

S/PDIF接收机/发射机没有单独的DMA信道。它接收串行格式的音频数据,并将其转换为双相编码信号。输入到接收器/发射器的串行数据可以格式化为左对齐、I2S或右对齐,字宽为16、18、20或24位。

到S/PDIF接收器/发射器的串行数据、时钟和帧同步输入通过信号路由单元(SRU)路由。它们可以来自多种来源,如运动、外部引脚和精密时钟发生器(PCG),并由SRU控制寄存器控制。

异步采样率转换器

异步采样率转换器(ASRC)包含四个ASRC块,与AD1896 192 kHz立体声异步采样率转换器的核心相同,提供高达128db的信噪比。ASRC块用于跨独立立体声通道执行同步或异步采样率转换,而不使用内部处理器资源。四个SRC块还可以配置为一起工作,以转换多声道音频数据,而不存在相位不匹配。最后,ASRC可用于清除来自抖动时钟源(如S/PDIF接收器)的音频数据。

输入数据端口

IDP提供多达八个串行输入通道,每个通道都有自己的时钟、帧同步和数据输入。八个通道被八个深度FIFO自动多路复用为一个32位。数据总是格式化为64位帧,并分成两个32位字。串行协议设计用于接收I2S、左对齐采样对或右对齐模式下的音频通道。一个帧同步周期表示一个64位左/右对,但数据以32位字(即一次发送一半帧)的形式发送到FIFO。处理器支持24位和32位I2、24位和32位左对齐以及24位、20位、18位和16位右对齐格式。

精密时钟发生器

精密时钟发生器(PCG)由四个单元A、B、C和D组成,每个单元产生一对从时钟输入信号导出的信号(时钟和帧同步)。这些单元在功能上是相同的,并且彼此独立运行。每个单元产生的两个信号通常用作串行位时钟/帧同步对。

数字外围接口(DPI)

数字外围接口提供到两个串行外围接口(SPI)端口、一个通用异步收发器(UART)、12个标志、一个2线接口(TWI)和两个通用定时器的连接。DPI包括以下各节中描述的外围设备。

串行外围接口

处理器包含两个串行外围接口端口(SPI)。SPI是一种工业标准的同步串行链路,使SPI兼容端口能够与其他SPI兼容设备通信。SPI由两个数据管脚、一个设备选择管脚和一个时钟管脚组成。它是一个全双工同步串行接口,支持主模式和从模式。SPI端口可以在多主环境中工作,它可以与多达四个其他SPI兼容设备(作为主设备或从设备)连接。SPI兼容的外设实现还具有可编程波特率、时钟相位和极性。SPI兼容端口使用开漏驱动程序来支持多主机配置并避免数据争用。

UART端口

处理器提供全双工通用异步收发(UART)端口,与PC标准UART完全兼容。UART端口为其他外设或主机提供简化的UART接口,支持全双工、支持DMA、异步串行数据传输。UART还具有使用9位地址检测的多处理器通信能力。这使得它可以通过RS-485数据接口标准在多点网络中使用。UART端口还支持5到8个数据位、1或2个停止位以及无奇偶校验。UART端口支持两种操作模式:

•PIO(编程I/O)–处理器通过写入或读取I/O映射的UART寄存器来发送或接收数据。数据在发送和接收时都是双缓冲的。

•DMA(直接存储器访问)–DMA控制器传输发送和接收数据。这减少了在存储器之间传输数据所需的中断次数和频率。

计时器

处理器共有三个定时器:一个核心定时器可产生周期性软件中断,两个通用定时器可产生周期性中断,并可独立设置为在三种模式之一下运行:

•脉冲波形生成模式

•脉冲宽度计数/捕获模式

•外部事件监视程序模式

核心定时器可以配置为使用FLAG3作为定时器过期信号,每个通用定时器有一个双向pin和四个寄存器来实现其操作模式。单个控制和状态寄存器独立启用或禁用两个通用计时器。

2线接口端口(TWI)

TWI是一个双向,2线串行总线,用于移动8位数据,同时保持与I2C总线协议的一致性。TWI master包含以下功能:

•7位寻址

•在支持多主数据仲裁的多设备系统上同时进行主从操作

•数字滤波和定时事件处理

•100 kbps和400 kbps数据速率

•低中断率

I/O处理器功能

自动版本的I/O处理器提供67个DMA通道,而标准版本提供36个DMA通道,以及在以下各节中描述的一组广泛的外围设备。

DMA控制器

DMA控制器允许无需处理器干预的数据传输。DMA控制器对处理器核心独立且不可见地操作,允许在核心同时执行其程序指令时进行DMA操作。DMA传输可以发生在处理器的内部存储器及其串行端口、SPI兼容(串行外围接口)端口、IDP(输入数据端口)、并行数据采集端口(PDAP)或UART之间。

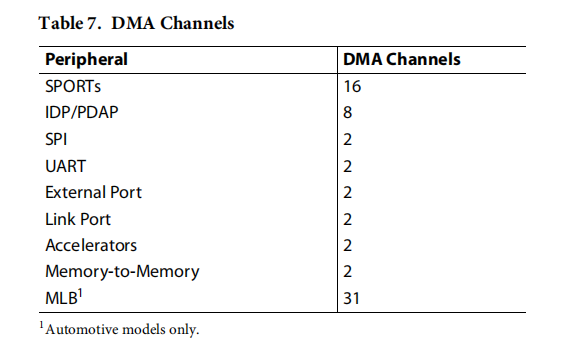

如表7所示,可提供多达67个DMA信道。可以使用DMA传输将程序下载到处理器。其他DMA功能包括在DMA传输完成时生成中断,以及用于自动链接DMA传输的DMA链。

延迟线DMA

延迟线DMA允许处理器以有限的内核交互读写外部延迟线缓冲区(从而读写外部内存)。

分散/聚集DMA

分散/聚集DMA允许对非连续内存块进行DMA读/写。

IIR加速器

IIR(无限冲激响应)加速器由1440字系数存储器(用于存储双四元系数)、数据存储器(用于存储中间数据)和一个MAC单元组成。控制器管理加速器。IIR加速器以外围时钟频率运行。

快速傅里叶变换加速器

FFT加速器实现基2复/实输入、复输出FFT,无需核心干预。FFT加速器以外围时钟频率运行。

杉木加速器

FIR(有限脉冲响应)加速器由1024字系数存储器、1024字深延迟线和四个MAC单元组成。控制器管理加速器。FIR加速器以外围时钟频率运行。

系统设计

以下各节介绍系统设计选项和电源问题。

程序启动

内部存储器通过外部端口、链路端口、SPI主设备或SPI从设备从8位EPROM启动系统电源。引导由表8中的引导配置(BOOTCFG2–0)管脚决定。

运行重置功能允许程序执行处理器核心和外围设备的重置,而无需重置PLL和DDR2 DRAM控制器或执行引导。这个复位引脚的功能也作为启动运行复位的输入。有关详细信息,请参阅ADSP-214xx SHARC处理器硬件参考。

电源

处理器有独立的电源连接,用于内部(VDD_INT)、外部(VDD_EXT)和模拟(VDD_A)电源。内部和模拟电源必须符合VDD国际规范。外部电源必须符合VDD外部规范。所有外部电源引脚必须连接到同一电源。

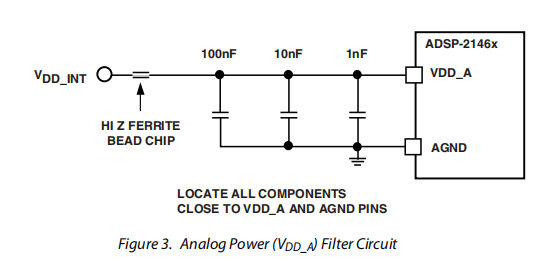

注意,模拟电源引脚(VDD_A)为处理器的内部时钟发生器PLL供电。为了产生一个稳定的时钟,建议PCB设计使用一个用于VDD_a引脚的外部滤波电路。将过滤器组件尽可能靠近VDD A/AGND引脚。有关示例电路,请参见图3。(推荐的铁氧体芯片是muRata BLM18AG102SN1D)。

为了减少噪声耦合,印刷电路板应使用一对电源和接地平面来进行VDD输入和接地。使用宽记录道将旁路电容器连接到模拟电源(VDD_A)和接地(AGND)引脚。请注意,图3中指定的VDD_A和AGND引脚是处理器的输入,而不是板上的模拟接地平面AGND引脚应直接连接到芯片上的数字接地(GND)。

目标板JTAG模拟器连接器

JTAG仿真器的模拟器件DSP工具产品线在仿真过程中利用处理器的IEEE 1149.1jtag测试访问端口对目标板处理器进行监控。模拟设备JTAG模拟器的DSP工具产品线提供全处理器速度的仿真,允许检查和内存、寄存器和处理器堆栈的修改。处理器的JTAG接口确保模拟器不会影响目标系统加载或计时。

有关JTAG模拟器操作的模拟设备SHARC DSP工具产品线的完整信息,请参阅相应的模拟器硬件用户指南。

开发工具

模拟设备通过一整套软件和硬件开发工具支持其处理器,包括集成开发环境(包括CrossCore Embedded Studio和/或VisualDSP++)、评估产品、模拟器和各种软件插件。

集成开发环境(IDE)

对于C/C++软件编写和编辑、代码生成和调试支持,模拟设备提供了两种IDE。

最新的IDE CrossCore Embedded Studio基于Eclipse框架。它支持大多数模拟设备处理器系列,是未来处理器(包括多核设备)的首选IDE。CrossCore Embedded Studio无缝集成了可用的软件插件,以支持实时操作系统、文件系统、TCP/IP堆栈、USB堆栈、算法软件模块和评估硬件板支持包。

其他的模拟设备IDE,VisualDSP++,支持CrossCore嵌入式Studio发布之前引入的处理器系列。该IDE包括模拟设备VDK实时操作系统和开源TCP/IP协议栈。有关更多信息,请访问/visualdsp。请注意,VisualDSP++将不支持未来的模拟设备处理器。

EZ-KIT Lite评估板

对于处理器评估,模拟设备提供广泛的EZ-KIT Lite评估板。包括处理器和关键外设,评估板还支持片上仿真能力等评估和开发功能。还提供了各种EZ扩展器,这些扩展器是提供额外专门功能的子卡,包括音频和视频处理。有关更多信息,请访问并搜索“ezkit”或“ezextender”。

EZ-KIT Lite评估套件

以更经济有效的方式了解模拟设备处理器,模拟设备提供了一系列的EZKIT Lite评估工具包。每个评估套件包括一个EZ-kit Lite评估板、下载可用IDE评估版本的说明、USB电缆和电源。EZ-KIT Lite板上的USB控制器连接到用户PC的USB端口,使所选IDE评估套件能够模拟电路中的板上处理器。这允许客户下载、执行和调试EZ-KIT Lite系统的程序。它还支持车载闪存设备的电路内编程,以存储用户特定的启动代码,从而实现独立操作。随着CrossCore Embedded Studio或VisualDSP++的完整版本的安装(单独出售),工程师可以为支持的EZKit或任何使用支持的模拟设备处理器的自定义系统开发软件。

用于CrossCore Embedded Studio的软件加载项

模拟设备提供与CrossCore Embedded Studio无缝集成的软件插件,以扩展其功能并缩短开发时间。插件包括评估硬件的板支持包、各种中间件包和算法模块。这些加载项中的文档、帮助、配置对话框和编码示例在加载项安装后可通过CrossCore Embedded Studio IDE查看。

评估硬件的板支持包

EZ-KIT Lite评估板和EZ的软件支持-扩展子卡由称为板支持包(BSP)的软件加载项提供。bsp包含所需的驱动程序、相关的发行说明,并为给定的评估硬件选择示例代码。特定BSP的下载链接位于相关EZ-KIT或EZExtender产品的网页上。该链接位于产品网页的产品下载区域。

中间件包

模拟设备分别提供中间件插件,如实时操作系统、文件系统、USB堆栈和TCP/IP堆栈。有关详细信息,请参阅以下网页:

•/ucos3

•/ucfs

•/ucusbd

•/lwip

算法模块

为了加快开发速度,模拟设备提供了执行流行的音频和视频处理算法的插件。这些可与CrossCore Embedded Studio和VisualDSP++一起使用。有关更多信息,请访问并搜索“Blackfin软件模块”或“SHARC软件模块”。

设计与模拟器兼容的DSP板(目标)

对于嵌入式系统的测试和调试,模拟设备提供了一系列的模拟器。在每个JTAG DSP上,模拟设备提供IEEE 1149.1jtag测试访问端口(TAP)。使用这个JTAG接口可以方便地进行电路内仿真。模拟器通过处理器的TAP访问处理器的内部特性,允许开发人员加载代码、设置断点、查看变量、内存和寄存器。处理器必须停止以发送数据和命令,但一旦模拟器完成某个操作,DSP系统将设置为全速运行,而不会影响系统计时。模拟器要求目标板包含一个头部,该头部支持将DSP的JTAG端口连接到模拟器。

有关目标板设计问题的详细信息,包括机械布局、单处理器连接、信号缓冲、信号终端和模拟器吊舱逻辑,请参阅模拟设备网站()上的EE-68:模拟设备JTAG仿真技术参考-使用“EE-68”上的站点搜索。本文档定期更新,以跟上对模拟器支持的改进。

附加信息

本数据表概述了ADSP-21467/ADSP-21469体系结构和功能。有关核心体系结构和指令集的详细信息,请参阅SHARC Processor Programming Reference。