W88111AF点击型号即可查看芯片规格书

一般说明

Winbond W88111AF/W88112F支持ATAPI CD-ROM规范(SFF 8020)。一些ATAPI操作由硬件执行,以最小化系统开销,包括ATAPI命令和数据包传输、数据传输、ATAPI软重置命令和执行驱动器诊断命令。它还支持影子驱动器。

Winbond W88111AF/W88112F支持各种类型的微处理器、DRAM和DSP。

W88111AF/W88112F支持高达12/20倍的驱动速度。它还支持CD-ROM、CD-ROM/XA、CD-I、视频CD、照片CD和CD Plus格式。

W88111AF/W88112F的功能包括CD-ROM数据解扰、实时错误第3层Reed Solomon产品类代码(RSPC)的修正、错误检测和数据传输

W88111AF/W88112F具有每个P字和Q字一个字节的实时ECC校正功能。它还可以执行重复的ECC传递,以提高数据的可靠性。

W88111AF/W88112F最多支持1兆字节的DRAM。它还支持环控制寄存器增加外部RAM控制的灵活性。

W88111AF/W88112F的主机接口支持使用PIO、单字DMA和多字DMA模式。有一个8字节的FIFO来提高IDE接口的吞吐量。

W88111AF/W88112F支持从外部RAM到主机的多块传输。

W88112F支持加速纠错/检测以提高系统性能。

W88112F支持自动目标头搜索、自动头比较和解码器中断状态收集以减少固件开销。

W88111AF/W88112F一般特征

T支持ATAPI CD-ROM标准(SFF 8020)

T支持CD-ROM、CD-ROM/XA、CD-I、Video CD、Photo CD和CD Plus格式

T支持最高12倍的驱动速度

T支持各种类型的微处理器和DSP

T支持各种行业标准DRAM

T支持环控寄存器,增加DRAM控制的灵活性

T支持CD-ROM数据解扰

T支持对每个P字和Q字的一个字节错误进行实时校正

T支持CD-ROM数据的错误检测

T支持重复纠错和检错通道

T8字节FIFO提高IDE接口吞吐量

T以PIO、单字DMA和多字DMA模式向主机传输数据

T多块传输

T100针PQFP

W88112F增强功能

T支持驱动速度高达20倍的45ns DRAM

T误差修正/检测加速高达33%

T自动目标标题搜索

T自动标题比较

T解码器中断状态采集

T高速行驶状态有效定时控制

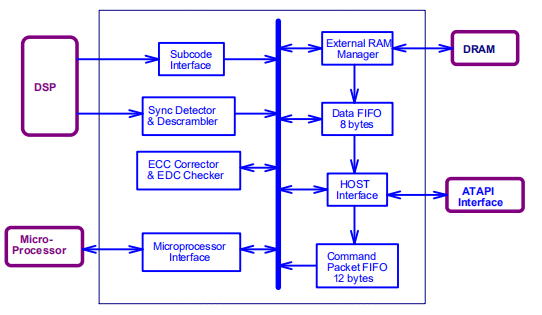

方块图

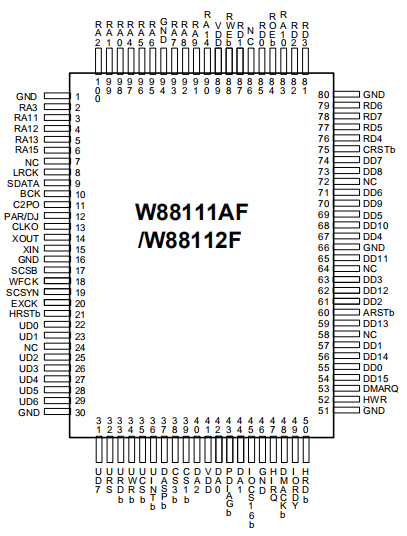

引脚配置

寄存器描述

IR-索引寄存器(读/写)当URS(引脚32)低时,微处理器可以访问索引寄存器。价值IR指定当URS(pin 32)高时微处理器访问哪个内部寄存器。注意在每次读或写任何寄存器之后,IR的4个最低有效位将增加,除了用于PFAR(00h)。由于IR不会自动从00h增加到01h,因此连续读取地址00h将重复读取寄存器PFAR(00h)。此功能加快了ATAPI命令包。

PFAR-包FIFO访问寄存器(读取00h)当SCoD(20h.2)较高时,从主机发出的ATAPI命令包由12字节接收分组先进先出。标记TENDb(01h.6)用于检查数据包FIFO是否已满。微处理器可以通过重复读取寄存器PFAR(00h)来读取ATAPI命令包。一旦先进先出变为空时,如果微处理器读取PFAR,则返回值FFh。

包FIFO还可用于接收小于12字节的命令参数。首先控制位SCoD(20h.2)设置为高,以选择由ATAPI数据寻址的包FIFO港口。当DRQ(37h.3)从0变为1时,ATBLO(34h)的低位4位被锁定为FIFO门槛。当FIFO中的字节数达到阈值时,标志TENDb(01h.6)变为低激活和标志FPKT(30h.1)变为高激活。一旦FPKT变高,任何数据写入ATAPI数据端口被拒绝。

中断控制寄存器(写01h)位7:PFNEEN-包FIFO非空中断启用如果该位高,当PFNEb(01h.7)变为低激活时,激活UINTb(引脚36)。

位6:TENDEN-传输结束中断启用当TENDb(01h.6)变为低激活时,如果该位为高,则激活UINTb(pin36)。坦登是如果主机在HIIEN(2Eh.7)为选择高和驱动器。

位5:SRIEN-扇区就绪中断启用当SRIb(01h.5)变为低电平时,如果该位为高电平,则激活UINTb(pin36)

位4、3、2:保留

位1:DTEN-数据传输启用Set DTEN high启用数据传输逻辑。此位应在下列任何一项之前设置触发数据传输:

·主机写入数据包FIFO

·从外部RAM读取主机

·主机从DF0读取到DF7为了减少微处理器的干扰,在以下操作:

·触发ADTT(17h.2)

·当启用APKTEN(18h.7)并且驱动器为挑选出来的

位0:保留中断原因寄存器(读取01h)位7:PFNEb-包FIFO非空中断标志当数据包FIFO通过

ATAPI数据端口。如果PFNEEN(01h.7),则当PFNEb变为低激活时,激活UINTb(引脚36)已启用。微处理器通过寄存器读取最后一个字节后,PFNEb被停用功率因数校正(00h)。

位6:TENDb-传输结束中断标志在下列数据传输结束时,该位变为活动低位:

·主机写入数据包FIFO

·从外部RAM读取主机

·主机从寄存器DF0(40h)读取到DF7(47h)

标记TDIR(30h.5)和FPKT(30h.1)可用于确定发生哪种类型的传输端。

如果启用TENDEN(01h.6),则当TENDb变为低激活时,激活UINTb(pin36)。

将任何值写入寄存器TACK(07h)将停用此标志。

位5:SRIb-扇区就绪中断标志此位用于指示一个扇区已准备好访问。读取寄存器STAT3(0Fh)停用SRIb。

位4:HCIb-主机命令中断标志此位由以下事件激活:

·如果启用了ARSTIEN(2Fh.1),主机将发出ATAPI软重置命令

·如果启用了SHIEN(2Eh.2),主机将向不存在的从驱动器发出命令

·如果启用了HIIEN(2Eh.7),主机将发出执行驱动器诊断命令

·如果启用HIIEN(2Eh.7),则ATAC(2Fh.6)将变为高激活状态

·如果启用HIIEN(2Eh.7),则在ATAPI设备控制寄存器中设置主机位SRST位3:TBSYb-传输忙标志当以下事件触发到主机的数据传输时,此位变为低激活:

·将任何值写入寄存器THTRG(06h)

·设置位ADTT(17h.2)高主机读取要传输的最后一个字节后,TBSYb将被停用。位2:MBTIb-多块传输中断标志此位由以下事件激活:

·当启用RPIEN(2Ah.5)时,RPINT(30h.3)变为高激活状态

·当启用MBKIEN(13h.2)时,MBTI(30h.4)变为高激活状态

微处理器可以读取寄存器MISS2(30h)来判断哪个事件发生。位1:DFRDYb-数据FIFO就绪触发数据传输后,自动填充8字节数据FIFO。这个钻头习惯表示数据FIFO已准备好供主机读取。

位0:SCIb-子码中断标志如果启用了SCIEN(2Ch.4),则当发生以下事件之一时,此位变为低激活:

·ISS(22h.0)变为高激活状态

·NESBK(22h.1)变为高激活状态

·MSS(22h.2)变为高激活状态

当激活子码中断时,微处理器可以将寄存器subsa(22h)读取到确定中断的原因。写入寄存器SCIACK(22h)使子码中断失效。

初步/保密

ATAPI CD-ROM解码器和控制器

-15-初步/机密修订版A0.1TBCL/TBCH-传输字节/字计数器(读/写02h/03h)在触发数据传输之前,应通过12位传输字节/字计数器。应将字节数减1写入此计数器使用8位数据传输时。当使用16位数据传输。主机读取一个字节或字后,计数器将减少一个,直到当该计数器为零时,传输结束中断被激活。

TACL/TACH-传输地址计数器-(写入04h/05h)触发数据传输前,应设置要传输数据的外部RAM地址通过16位传输地址计数器。此计数器中的此数字指定第一个可用的相对于块开头的数据地址。还应指定块号通过传输块寄存器TBL/TBH(24小时/25小时)。主机读取一个字节/字后,TACL/TACH增加到下一个可用的数据地址。

TBL/TBH—传输块寄存器(读/写24小时/25小时)在触发数据传输之前,要传输的数据的外部RAM块应该通过传输块寄存器。TBL/TBH形成一个9位寄存器,用于指定第一个RAM块传输,而TACL/TACH(04h/05h)指定相对于这个内存块。结束时,TBL/TBH中的RAM块数不会自动增加每次传输,除非通过指定寄存器MBTC0(12h)使用多块传输。THTRG-传输到主机触发寄存器-(写入06h)无论写入什么值,此寄存器都用于触发数据传输。

当位UDTS(1Fh.6)较低时,THTRG之后从外部RAM到主机的数据传输触发。触发THTRG自动填充数据FIFO,然后标记DFRDYb(01h.1)当数据FIFO准备就绪时变为低激活状态。

当位UDTS(1Fh.6)高时,数据传输的路径是从寄存器DF0-DF7(40h-47h)到主人。在这种情况下,应使用寄存器TBCL(02h)设置小于8的数据计数触发THTRG和位UDTT(1Fh.7)应在触发THTRG后设置为1后跟0。

TACK-传输确认-(写入07h)写入寄存器TACK使TENDb(01h.6)及其相应的微处理器中断失效不管写了什么数据。

头0到头3-头寄存器(读取03h到07h)这四个寄存器用来保存每个扇区的头字节信息。标题寄存器应该在STAVAb(0F.7)变为低激活状态后立即读取。注意,头字节如果在启用ECC时设置了错误的模式,则不可信。如果位SHDEN(0Bh.0)已启用,寄存器HEAD0-3用于保存子标题字节。

BIAL/BIAH-缓冲初始地址寄存器-(写入08h/09h)在启用外部RAM缓冲之前,应该设置BIAL/BIAH来控制第一个字节跟随每个数据扇区的数据同步。用于缓冲的RAM块由寄存器DDBL/DDBH(28h/29h)中的数字加一。为了便于后续的数据传输微处理器应将适当的值设置为BIAH/BIAL(模式1为FF,F0h,模式2为FF,E8h)确定模式后,第一个用户数据字节将位于每个数据的偏移量00h处封锁。

BACL,BACH-缓冲地址计数器(读取0Ah/0Bh)启用外部RAM缓冲后,缓冲写入计数器会自动增加从BIAL/BIAH指定的值开始,每次缓冲一个数据字。EIAL/EIAH-ECC初始地址寄存器-(读08h/09h,写0Ch/0Dh)EIAL/EIAH用于保持要校正的数据块的初始地址偏移。内容BIAL/BIAH(08h/09h)将在每次数据同步开始时自动加载到EIAL/EIAH,使其在正常操作期间无需读取或写入EIAL/EIAH。ECC的RAM块由寄存器DDBL/DDBH(28h/29h)中的数字控制。

SCBL/SCBH-子码块寄存器-(读/写26h/27h)

SCBL/SCBH形成一个9位寄存器,包含最新可用子码数据的块号主机可以读取的。SCBL/SCBH中的数字加1指向RAM块,即缓冲传入子代码。SCBL/SCBH中的数目在子代码末尾增加了一个块缓冲。

DDBL/DDBH-解码数据块寄存器(读/写28h/29h)DDBL/DDBH构成一个9位寄存器,包含最新可用解码数据块的编号解码器中断后。此块编号应用于指定TBL/TBH(24小时/25小时)在触发到主机的数据传输之前。这个解码的数据块号加1点到缓冲输入串行数据并在每个数据块末尾增加一个的DRAM块缓冲。

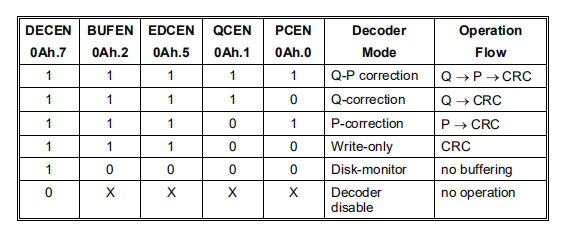

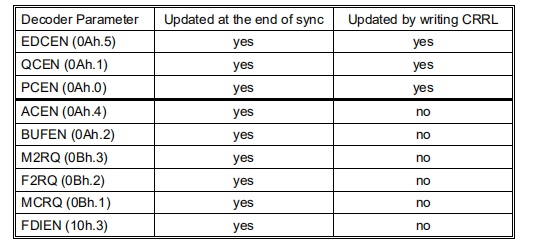

CTRL0-控制寄存器0-(写入0Ah)位7:DECE-解码逻辑启用将此位设置为高将启用解码逻辑。位5:EDCEN-错误检测和纠正启用将此位设置为高将启用ECC和EDC逻辑。

位4:ACEN-自动校正启用当此位在模式2 ECC期间设置为高时,纠错类型自动由副标题字节中的格式位的设置确定。当此位在模式2 ECC,纠错类型由F2RQ(0Bh.2)控制。

位2:BUFEN-缓冲启用将此位设置为高将启用传入的DSP数据缓冲。当该位为高时寄存器头0-3(04h-07h)和子0-3(14h-17h)是从外部RAM而不是从输入的串行数据。当BUFEN低时,QCEN或PCEN的任何设置都没有意义。

位1:QCEN-Q码字校正启用当该位高时,Q码字RSPC校正逻辑被启用。

位0:PCEN-P码字校正启用当该位高时,P码字RSPC校正逻辑被启用。

CTRL1-控制寄存器1-(写入0Bh)位7:SIEN-同步插入启用当该位高时,扇区边界由内部同步插入逻辑确定。

位6:SDEN-同步检测启用当该位高时,扇区边界由输入的串行数据确定。

位5:DSCREN-解扰器启用将此位设置为高将启用解扰逻辑。

位4:CWEN-修正数据写入启用将此位设置为高可以将校正后的数据写入外部RAM。

位3:M2RQ-模式2 ECC请求将此位设置为高将启用模式2 ECC校正逻辑。模式1 ECC校正将为如果该位低,则执行。

位2:F2RQ-表单2请求

如果将此位设置为高,则请求以模式2 form-2格式处理数据M2RQ(0Bh.3)高。

位1:MCRQ-模式字节检查请当该位为高位时,ECC逻辑将检查第4个报头字节,并将M2RQ(0Bh.3)设置为确定是否需要执行ECC校正。

位0:SHDEN-副标题开关启用当该位为高位时,寄存器HEAD0-3用于提供子标题字节。STAT0-状态寄存器0-(读取0Ch)位7:CRCOK-循环冗余检查正常此位用于指示最近可用扇区的循环冗余检查是否通过。

位6:ILSYN-非法同步模式

如果SDEN(0Bh.6)为高,则当检测到同步模式小于2352时,该位变为高检测到/插入上次同步模式后的字节数。位5:NOSYN-无同步模式

如果SIEN(0Bh.7)为高,则当在2352字节处未检测到同步模式时,此位变为高在检测到/插入上一个同步模式之后。位4:LBKF-长块标志

如果SIEN(0Bh.7)低,则当在2352字节处未检测到同步模式时,该位变为高在检测到/插入上一个同步模式之后。位3:WSHORT-Word Short当输入的串行数据速率太高而无法由W88111AF/W88112F。

位2:SBKF-短块标志如果SDEN(0Bh.6)低,则当检测到同步模式小于2352字节时,该位变为高在检测到/插入上一个同步模式之后。

位2:F2RQ-表单2请求如果将此位设置为高,则请求以模式2 form-2格式处理数据M2RQ(0Bh.3)高。

位1:MCRQ-模式字节检查请求当该位为高位时,ECC逻辑将检查第4个报头字节,并将M2RQ(0Bh.3)设置为确定是否需要执行ECC校正。

位0:SHDEN-副标题开关启用当该位为高位时,寄存器HEAD0-3用于提供子标题字节。STAT0-状态寄存器0-(读取0Ch)

位7:CRCOK-循环冗余检查正常此位用于指示最近可用扇区的循环冗余检查是否通过。

位6:ILSYN-非法同步模式如果SDEN(0Bh.6)为高,则当检测到同步模式小于2352时,该位变为高检测到/插入上次同步模式后的字节数。

位5:NOSYN-无同步模式如果SIEN(0Bh.7)为高,则当在2352字节处未检测到同步模式时,此位变为高在检测到/插入上一个同步模式之后。

位4:LBKF-长块标志如果SIEN(0Bh.7)低,则当在2352字节处未检测到同步模式时,该位变为高在检测到/插入上一个同步模式之后。

位3:WSHORT-Word Short当输入的串行数据速率太高而无法由W88111AF/W88112F。

如果SDEN(0Bh.6)低,则当检测到同步模式小于2352字节时,该位变为高在检测到/插入上一个同步模式之后。

位1:FDIF-快速解码器中断标志如果启用了FDIEN(10h.3),则当头/副头字节准备就绪时,该位变高在ECC完成之后和CRC完成之前。同时,UINTb(引脚36)和STAVAb(0Fh.7)变为低激活状态,从而加速以下微处理器操作。当CRC完成时,FDIF被停用。当CRC为完成。因此,如果启用了FDIEN(10h.3),则应该使用CRCVAb(10h.7)来确定当中断激活时,CRCOK(0Ch.7)可用。位0:UEBK-块中不可纠正的错误此位用于指示在最新的可用数据块中至少有一个数据被纠正。STAT1-状态寄存器1-(读取0Dh)位4:HDERA-头擦除如果在不包括模式字节的头字节中检测到至少一个擦除标志,则此位为高。删除模式字节将导致RMOD3-0(0Eh.7-4)全部变高。位0:SHDERA-副标题擦除如果在至少一个子标题字节对中检测到两个字节的擦除标志,则此位为高。

如果禁用BUFEN(0Ah.2),则从引脚C2PO锁定擦除。否则,标题和副标题在缓冲下列扇区时,从外部RAM中检索字节。

DHTACK-DRAM到主机传输确认-(写入0Eh)写入DHTACK时,不管写入了什么数据,都会使TENDb(0Eh.6)从外部RAM到主机的数据传输端失效。STAT2-状态寄存器2-(读取0Eh)

位7-4:RMOD[3:0]-原始模式位RMOD[2:0]直接从第4个头字节的第2-0位锁定,如果有,RMOD3为高模式字节中的其他5位之一为高。如果模式字节擦除是检测。

位3:模式2-模式2选择标志该位反映M2RQ(0Bh.3)的设置。位2:NOCOR-无校正如果由位EDCEN(0Ah.5)和QCEN(0Ah.1)或PCEN(0Ah.0)启用ECC逻辑,则该位如果ECC逻辑中断以下情况,则变为高:

·CWEN(0Bh.4)被禁用。

·启用MCRQ(0Bh.1)时检测到模式不匹配。

·启用MCRQ(0Bh.1)时检测到模式擦除。如果为第四个头字节设置传入的C2PO标志,指示不可靠的模式数据。

·当ECC逻辑设置为模式2时,启用窗体2。不应更正表2块。表单2可以通过控制位F2RQ(0Bh.2)或子标题中的表单位启用如果启用了ACEN(0Ah.4),则为字节。

·当ECC逻辑设置为模式2并启用ACEN时,窗体位擦除。形式位擦除如果为子标题字节中的两个表单位设置了传入的C2PO标志,则检测到。

·启用SDEN(0Bh.6)时,ILSYN(0Ch.6)变高。位1:RFERA-原始形式擦除当检测到表单位擦除时,此位变高。如果子模式字节(字节18和22中的位5)中的两个表单位都设置了传入的C2PO标志。当SRIb(01h.5)变为低激活时,RFERA变为有效,并保持有效直到下一个阻止同步。

位0:RFORM-原始表单位如果传入串行数据的子模式字节中的格式位高,则此位为高。RFORM格式当标志SRIb(01h.5)变为低激活时变为有效,并在下一个块之前保持有效同步

FRST-固件重置寄存器-(写入0Fh)写入寄存器FRST,无论写入什么值,都会重置W88111AF/W88112F的大部分逻辑,但以下除外:

·寄存器CCTL1(1Ah)和输出引脚CLKO

·寄存器DSPSL(1Bh)

·寄存器HICTL1(20h)

·寄存器SICTL0(21h)

·寄存器RAMCF(2Ah)

·寄存器MEMCF(2Bh)

·寄存器SICTL1(2Ch)

·寄存器MISC0(2Eh)

·寄存器MISS1(2Fh)

·寄存器MISC1(2Fh.7-5,3-0)

·ATAPI驱动器选择寄存器中的位DRV

·ATAPI设备控制寄存器中的SRST和nIEN位标记FRST(2Fh.1)由固件重置设置。

STAT3-状态寄存器3-(读取0Fh)位7:STAVAb-有效状态有效此位用于指示有关解码器逻辑的头、指针和状态寄存器可用。

位5:ECF—错误修正标志此位用于指示至少有一个字节已在最新可用的封锁。

位4:EINC-ECC不完整标志如果启用了EINCEN(10h.1),则当以下块的校正为在前一个块完成之前触发。当如果启用了EINCEN,EINC将变为高。

位1:在块标志中检测到C2DF-C2如果C2WEN(10h.2)为高,则当检测到至少一个C2PO标志时,C2DF变为高在上一个街区。

位6,3,2,0:保留控制写入寄存器(写入10h)位7:定义0

位6:SWEN-同步写入启用如果这个位是高的,BUFEN(0Ah.2)的变化将同步到下一个扇区的末尾同步。C2PO标志的缓冲也由SWEN if C2WEN(10h.2)和BUFEN控制(0AH.2)都已启用。位5:SDSS-子码和DSP同步该位提供CD-DA格式数据的同步。如果该位高,则写入外部RAM的串行数据将在结束后的第一个左下通道字节开始子代码块。

位4:DCKEN-数字信号处理器时钟启用如果该位高,则内部解码器逻辑使用来自DSP的时钟。DCKEN应该设置为高在dece(0Ah.7)设置为高之前。

位3:FDIEN-快速解码器中断启用如果FDIEN(10h.3)设置为高,则在头/副标题字节为ECC完成后和CRC完成前准备就绪:

·FDIF(0Ch.1)–1

·斯塔瓦(0Fh.7)–0

·SRIb(01h.5)–0级读取寄存器STAT3(0Fh)将上述SRIb(01h.5)关闭至1。如果FDIEN(10h.3)设置为高,则在CRC完成时会发生以下事件:

·FDIF(0Ch.1)–0

·CRCVAb(10小时7分)–0

·SRIb(01h.5)–0级

·CRCOK(0Ch.7)可用读取寄存器STAT4(10h)将上述SRIb禁用为1。

SRIb(01h.5)在快速中断时变为低激活状态,如果启用了FDIEN,则CRC结束。CRCVAb公司应用于确定SRIb变为低激活状态时CRCOK是否准备就绪。

位2:C2WEN-C2标志写入启用如果该位设置为高,且BUFEN(0Ah.2)为高,则输入串行数据的C2标志将为锁定在外部RAM中。如果SWEN(10h.6),此操作将同步到同步结束很高。

位1:DRST-解码器复位将此位设置为高将重置解码逻辑。DRST自动清除。

位0:EINCEN-ECC不完整中断启用如果该位设置为高,则当下列块的校正为在前一个块的修正完成之前触发。

STAT4-状态寄存器4(读取10h)

位7:CRCVAb-CRC有效

如果启用了FDIEN(10h.3),CRCVAb在CRC完成时变为低激活状态。读这个如果启用了FDIEN,则寄存器会因完成CRC而停用SRIb(01h.5)。

位6-0:保留CRTRG-更正重试触发器-(写入11h)写入寄存器CRTRG,不管写入什么数据,都会触发解码逻辑来执行同一块的另一个校正序列。

位7-1:保留位0:CRRL-更正重试寄存器加载

在写入寄存器CRTRG(11h)时将该位设置为高,重新加载EDCEN(0Ah.5)的设置,QCEN(0Ah.1)或PCEN(0Ah.0)用于解码逻辑。

MBTC0-多块传输控制0-(读/写12h)此寄存器仅用于W88111AF,以指定多块传输逻辑的行为。这个主机接口支持多块传输,无需微处理器干预顺序:

•MBC[4:0]—要传输的块数减去1(例如3)

·TBCL(02h),TBCH(03h)–每个块中要传输的字节数/字数减1(例如1175)

·TACL(04h),TACH(05h),块的起点(例如F4h,FFh)

·TBL(24小时),TBH(25小时),要传输的第一个块的RAM块号(例5)

·ATBLO(34h),ATBLH(35h)–要传输的总字节数(例如9408)

·ADTT(17小时4分)1注意:在多块传输操作中不应设置STBCEN(18h.3)。当ADTT被设置时,主机将接收HIRQ,检查状态,然后开始读取数据。在主机读取一个块(除了最后一个块)的最后字节/字之后,如下执行硬件序列:

·TBCL(02h),TBCH(03h),重新加载

·TACL(04h),TACH(05h),重新加载

·TBL(24小时),TBH(25小时),自动递增

·MBC[4:0]——自动减量

TENDb只在最后一个块的数据传输结束时变为活动的。位7:MBVAb-多块计数器有效标志此位用于指示多块计数器MBC[4:0]足够稳定,可以由微处理器。

位6:MBINC-多块增量标志

如果微处理器设置了INCMBC(13h.0)和多块数,则该位变为高激活位增量尚未完成。位4-0:MBC[4:0]-多块计数器在触发多块传输之前,要传输的块数减去1写信给MBC[4:0]。如果MBC[4:0]为零,则执行单块传输。MBTC1-多块传输控制1-(读/写13h)位7-3:保留位2:MBTIEN-多块传输中断启用如果MBTIEN和MBTFEN都已启用,则UINTb将在每个如果MBC[4:0]中的块计数不为零,则阻塞。

位1:MBTFEN-多块传输中断标志启用如果该位为高,则在每个数据块的数据传输结束时,如果MBC[4:0]中的块计数不是零。

位0:INCMBC—递增多块计数器将该位设置为高将多块计数器MBC[4:0]增加一个。此函数在数据中很有用通过DMA模式传输到主机。由于在DMA模式传输中未指定数据计数,因此在新块可用之前,可以增加要传输的块的数量传输完成。

增强控制寄存器(写入14h)位7-2:保留位1:IR7F-在IR7处提供标志UTBY当该位为高时,标记UTBY(1Fh.7)可由索引寄存器的读取位7监视。

位0:DISAI-禁用自动增量当该位为高时,RACU/RACH/RACL地址计数器的自动增量为已禁用。注意,在触发RFTRG(2Ah.6)之前,DISAI应该为0。

第0子目至第3子目-副标题寄存器(读取时间:14h至17h)这些寄存器用于保存子标题字节的信息。如果BUFEN(0Ah.2)被禁用,子标题字节从传入的串行数据中锁定。如果启用了BUFEN(0Ah.2),则为subheader字节从外部RAM中检索。

自动顺序触发寄存器(写入17h)在触发操作完成后,下列位将自行清除。

位7:保留位6:CSRT-清除软复位触发器将此位设置为高将清除ATAPI设备控制寄存器中的位SRST。

位5:DSCT-磁盘寻道完成触发器如果ABYEN(18h.1)为高,则设置DSCT high将触发以下操作:

·设置BSY

·差示扫描量热法(37h.4)–1

·清除BSY如果ABYEN(18h.1)较低,则设置DSCT high会将DSC(37h.4)设置为1。位4:SIGT-ATAPI签名触发器将此位设置为高将使用ATAPI签名初始化任务寄存器。

·ATFEA(31小时)–00小时

·阿特尔(31h)–01h

·ATINT(32小时)–01小时

·水疗中心(33小时)–01小时

·ATBLO(34小时)–14小时

·阿特比(35小时)–EBh

·ATSTA(37小时)–00小时

注意,寄存器ATDRS(36h)不是通过触发SIGT来遵守ATAPI协议来清除的。

位3:CPFT-清除包FIFO触发器将此位设置为高将清除数据包FIFO。位2:ADTT-自动数据传输触发器如果PIO(1Fh.2)高,则设置ADTT高将触发以下PIO数据传输序列:

·设置BSY

·DTEN(01h.2)–1号

·斯科德(20h.2)–0

·ATINT(32小时)–02小时

·如果启用STBCEN(18h.3),则ATBLO/ATBHI(TBCL,H+1)’2数据传输逻辑将开始自动填充数据FIFO。下面的顺序是当DFRDYb(01h.1)变为低激活时执行:

·DRQ(37h.3)–1号

·清除BSY

·HIRQ(2小时3分)1检测到中断后,主机将检查状态,然后读取数据。STBCEN(18h.3)不应用于自动多块传输。相反,阿特布洛,ATBHI应通过固件设置为:(MBKC+1)’((TBCL,H+1)’2)如果PIO(1Fh.2)低,则设置ADRTG高将触发以下DMA数据读取序列:

·设置BSY

·DTEN(01h.1)–1号

·斯科德(20h.2)–0

·ATINT(32小时)–02小时位1:DRQT-DRQ触发器如果位PIO(1Fh.2)为高,则将此位设置为高将触发以下硬件序列:

·DRQ(37h.3)–1号

·HIRQ(2小时3分)1当位PIO低(DMA模式)时,不应触发该位。位0:SCT-状态完成触发器将此位设置为高将触发以下硬件序列:

初步/保密

·支票(37h.0)–支票(3Eh.0)

·腐蚀剂(37h.2)–氧化钙(3Eh.2)

·博士(37h.6)–博士(3EH.6)

·ATINT(32小时)–03小时

·清除BSY

·HIRQ(2小时3分)1

·APKTEN(18h.7)–1,如果AUTOEN(18h.4)很高

·上升(18h.5)–0在检测到中断后,主机读取ATAPI状态寄存器,如有必要,则读取错误注册命令完成状态。

自动顺序控制寄存器(读/写18h)位7:APKTEN-自动包传输启用将此位设置为高可启用自动数据包传输逻辑。当APKTEN高时如果主机向ATA命令发出操作码A0h,则执行以下硬件顺序如果已选择驱动器,请注册:

·设置BSY(37h.7)

·APKT(30h.0)–1

·清除数据包先进先出

·阿特尔(31h)–00h

·ATINT(32小时)–01小时

·DTEN(01h.1)–1号

·TENDEN(01h.6)–1,如果HIIEN(2Eh.7)高

·斯科德(20h.2)–1

·检查(37h.0)–0

·腐蚀(37h.2)–0

·DRQ(37h.3)–1号

·DSC(37h.4)–1,如果ASDSC(3Dh.4)高

·DY博士(37h.6)–1

·如果A0IEN(18h.0)高,则为HIRQ(2Eh,3)-1

·阿普克滕-0

·清除BSY(37h.7)在自动数据包传输期间,ATAC(2Fh.6)不会被激活。

当清除BSY后驱动器准备就绪时,主机开始发出12字节的ATAPI命令包。接收到第6个数据包字将激活以下事件。

·FPKT(30h.1)–1

·趋势B(01h.6)–0

·如果TENDEN(01h.6)已启用,则Pin UINTb激活将任何值写入寄存器TACK(07h)将停用APKT、TENDb和相应的中断。位6:ADCEN-自动DRQ清除启用当该位为高时,DRQ(37h.3)被清除为0,BSY(37h.7)在结束后被设置为1以下转移:

·主机从外部RAM读取

·主机从DF0-DF7读取

·主机写入命令包FIFO位5:ASCEN-自动状态完成启用当该位为高位时,在下列传输结束后执行状态完成:

·主机从外部RAM读取

·主机从DF0-DF7读取

·主机写入命令包FIFO

当启用ASCEN以提供DRQ(37h.3)的清除时,应启用ADCEN(18h.6)以及设置BSY(37h.7)。如果启用了ADCEN和ASCEN,则以下硬件序列在上述数据传输结束时执行:

·设置BSY

·DRQ(37小时3分)–0

·支票(37h.0)–支票(3Eh.0)

·腐蚀剂(37h.2)–氧化钙(3Eh.2)

·博士(37h.6)–博士(3Eh.6)

·ATINT(32小时)–03小时

·清除BSY

·HIRQ(2小时3分)1

·APKTEN(18h.7)–1,如果AUTOEN(18h.4)很高

·上升(18h.5)–0

在检测到中断后,主机读取ATAPI状态寄存器,如有必要,则读取错误注册命令完成状态。

位4:自动开启-状态完成后自动开启当该位为高位时,自动状态完成序列后将设置APKTEN(18h.7)由SCT(17h.0)或ASCEN(18h.5)触发。

位3:STBCEN-设置传输字节计数启用当该位高时,当ADTT时,值(TBCL,H+1)’2加载到ATBLO和ATBHI中(17h.2)被触发,PIO(1Fh.2)被设置为高。不应为多个设置STBCEN封锁转移。相反,ATBLO/ATBHI应该通过固件设置为:(MBKC+1)’(TBCL,H+2)。

位1:ABYEN-自动BSY设置启用当该位为高位时,当磁盘查找完成由DSCT(17小时5分):

·设置BSY

·差示扫描量热法(37h.4)–1

·清除BSY

·DSCT-0型位0:A0IEN-A0h命令中断启用如果该位为高,且已启用APKTEN(18h.7),则HIRQ(2Eh.3)在向ATA命令寄存器发出操作码A0h。

CCTL0-时钟控制寄存器0-(写入19h)位7:CKSTP-时钟停止将此位设置为高将停止内部时钟和pin CLKO处的时钟输出。CKSTP被以下事件取消激活:

·芯片复位或主机复位或固件复位

·选择驱动器时从主机写入命令

·主机发出诊断命令,与驱动器选择无关

·如果启用了SHDRV(3Fh.6),主机将向卷影驱动器发出命令

·主机将ATAPI设备控制寄存器中的位SRST设置为高,与驱动器选择无关位6:PJSEL—奇偶校验/跳线选择当该引脚为高,PIN PAR/JP用作缓冲RAM奇偶校验引脚。当这个针很低时将PANPAR/JP的倒值采样到控制位DRV1B(2EH。4)。取样时间为由JPSS(19h.5)控制。

位5:JPSS-跳线采样选择如果PJSEL(19H。6)是低的,则该位用于控制PIN PA/JP的采样。当JPSS是高,引脚PAR / JP采样,而芯片复位是活跃的。当这个位低时,PAR/JP被采样。当芯片复位或主机复位激活时。

位4:保留位3-0:CKS[3:0]-时钟偏差控制CKS[3:0]用于控制内部时钟的占空比

CCTL1-时钟控制寄存器1-(写入1Ah)位7:流量-流量控制该位用于根据8字节数据FIFO的状态控制管脚IORDY。它应该被设置8位DRAM为高,4位DRAM为低。流通过芯片复位或主机复位被取消激活。

位6:TSYNC-测试同步控制当该位高时,可从CLKO(引脚13)监视检测到/插入的DSP数据同步。

位5,4:保留位3:CLKOS-引脚CLKO选择当CLKOS较低时,CLKO引脚提供一半晶体频率的时钟信号。当这个位CLKOS高,CLKO引脚提供正常晶体频率。

位2,1:保留位0:XTALD2-晶体除以2如果这个位元高,内部时钟频率是晶体频率的一半。

版本寄存器(读取1Ah)此寄存器用于保存版本号。W88111AF的当前版本是1Bh。这个W88112F的当前版本是2Ah。

DSPSL-DSP选择寄存器(写入1Bh)位7:C2ML-C2 MSB到LSB当该位为高位时,C2PO(pin 11)的擦除序列从MSB到LSB。