AD9984A点击型号即可查看芯片规格书

特征

10位模数转换器;170 MSPS最大转换率;170msps时的低PLL时钟抖动;自动增益匹配;自动抵销调整;2:1个输入多路复用器;通过专用引脚或串行寄存器断电;4:4:4、4:2:2和DDR输出格式模式;可变输出驱动强度;奇偶场检测;外部时钟输入;重新生成的Hsync输出;可编程输出高阻抗控制;每个Vsync计数器的Hsyncs;绿色同步(SOG)脉冲滤波器;无铅包装。

应用

高级电视;等离子显示屏;液晶数字电视;高清电视;RGB图形处理;液晶显示器和投影仪;扫描转换器。

一般说明

AD9984A是一个完整的10位、170毫秒/秒的单片模拟接口,为捕获YPbPr视频和RGB图形信号而优化。其170 MSPS的编码速率能力和300兆赫的全功率模拟带宽支持所有高达1080p的HDTV视频模式,以及高达UXGA(1600×1200,60赫兹)的图形分辨率。

AD9984A包括一个170兆赫的三重ADC,带有一个内部基准、一个PLL和可编程增益、偏移和钳位控制。用户仅提供1.8V电源和模拟输入。三态CMOS输出可以从1.8v供电到3.3v。

AD9984A片上PLL从三电平同步(用于YPbPr视频)或水平同步(用于RGB图形)生成采样时钟。采样时钟输出频率范围从10兆赫到170兆赫。通过内部的海岸产生,锁相环在没有同步输入的情况下保持其输出频率。32步提供采样时钟相位调整。保持输出数据、同步和时钟相位关系。

可启用自动偏移功能,以自动恢复信号参考电平并校准三个通道之间的任何偏移差。可以启用自动通道间增益匹配功能,以最小化三个通道之间的任何增益不匹配。

AD9984A还为复合同步和绿色应用程序上的同步提供完全同步处理。钳位信号在内部产生,或者可以由用户通过钳位输入引脚提供。

AD9984A采用先进的CMOS工艺制造,采用节省空间、无铅、80导联的低剖面四平板封装(LQFP)或64导联的框架芯片级封装(LFCSP)并在0°C至70°C温度范围内指定。

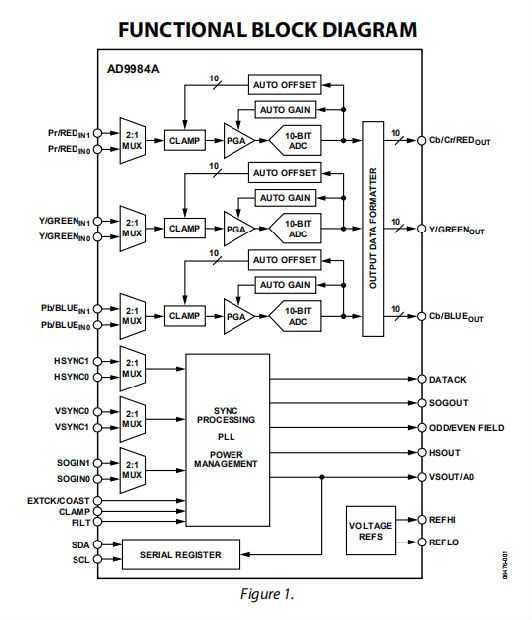

操作理论

AD9984A是一个完全集成的解决方案,用于捕获和数字化模拟RGB或YPbPr信号,以便在高级电视、平板显示器、投影仪和其他类型的数字显示器上显示。在高性能CMOS工艺中实现,接口可以捕获像素速率高达170mhz的信号。

AD9984A包括所有必要的输入缓冲、信号直流恢复(钳位)、偏移和增益(亮度和对比度)调整、像素时钟生成、采样相位控制和输出数据格式化。所有控制都可通过2线串行接口(IC)编程。这些敏感模拟功能的完全集成使得系统设计简单明了,对物理和电气环境的敏感度较低。

该装置的典型功耗小于900兆瓦,工作温度范围为0°C至70°C,无需特别考虑环境因素。

数字输入

AD9984A上的所有数字输入工作到3.3V CMOS电平。以下数字输入为5V耐受电压(即5V不会造成任何损伤:HSYNC0、HSYNC1、VSYNC0、VSYNC1、SOGIN0、SOGIN1、SDA、SCL和夹钳。

模拟输入信号处理

AD9984A有六个高阻抗模拟输入引脚,分别用于红色、绿色和蓝色通道。它们可容纳0.5 V至1.0 V p-p的信号。

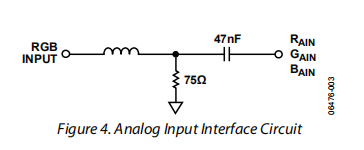

信号通常通过DVI-I连接器、15针D连接器或RCA连接器带到接口板上。AD9984A应尽可能靠近输入接头。应使用匹配的阻抗轨迹(通常为75Ω)将信号路由到IC输入引脚。

在输入引脚处,信号应电阻端接(75Ω至信号接地回路),并通过47个nF电容器电容耦合至AD9984A输入。这些电容器构成直流恢复电路的一部分。

在阻抗完全匹配的理想世界中,尽可能宽的信号带宽可以获得最佳性能。AD9984A(300 MHz)的宽带输入可以在输入信号从一个像素级移动到下一个像素级时连续跟踪该信号,并且可以在长而平坦的像素时间内对该像素进行数字化。然而,在许多系统中,存在不匹配、反射和噪声,这可能导致输入波形的过度振铃和失真。这使得建立提供良好图像质量的采样阶段变得更加困难。与输入串联的小电感器被证明在较宽的条件范围内稍微降低输入带宽并提供高质量信号是有效的。在图4所示的电路中,使用高速信号芯片,磁珠感应器(如Fair Rite 2508051217Z0)在大多数应用中提供了良好的效果。

HSYNC和VSYNC输入

接口还接受Hsync和Vsync信号,这些信号用于生成像素时钟、钳位定时以及海岸和场信息。这些信号可以是直接来自图形源的同步信号,也可以是经过预处理的TTL或CMOS级信号。

Hsync输入包括一个Schmitt触发缓冲器,用于抗噪声和长上升时间信号。在典型的基于PC机的图形系统中,同步信号只是TTL级驱动程序,将非屏蔽线馈入显示器电缆。因此,无需终止。

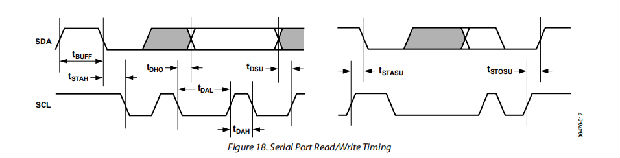

串行控制端口

串行控制端口是为3.3V逻辑设计的;但是,它可以容忍5V逻辑信号。有关更多信息,请参阅2线串行控制端口部分。

输出信号处理

数字输出在1.8 V到3.3 V(V)之间工作。

夹紧

RGB夹紧

为了正确地数字化输入信号,必须调整输入的直流偏移以适应车载adc的范围。

大多数图形系统产生的RGB信号在地面为黑色,在0.75伏左右为白色。但是,如果同步信号嵌入图形中,则同步提示通常在地面,黑色为300毫伏,而白色大约在1.0v。一些常见的RGB线路放大器盒使用发射器跟随器缓冲区来分割信号并提高驱动能力。这将向信号引入700 mV的直流偏移量,AD9984A必须移除该偏移量才能正确捕获。

夹紧的关键是在已知图形系统产生黑色时识别信号的一部分(时间)。然后引入偏移量,当存在已知的黑色输入时,该偏移量导致ADC产生黑色输出(代码0x00)。然后,当处理其他信号电平时,偏移保持在原位,并且整个信号被移位以消除偏移误差。

在大多数PC图形系统中,黑色在活动视频线之间传输。使用CRT显示器,当电子束在屏幕上(在右侧)完成水平线的写入时,电子束迅速偏转到屏幕的左侧(称为水平回程),并且提供黑色信号以防止电子束干扰图像。

在具有嵌入式同步的系统中,会短暂地产生比黑信号更黑的信号(Hsync),以向CRT发出开始回溯的信号。由于此时输入不在黑色级别,因此在Hsync期间避免夹持是很重要的。幸运的是,Hsync(称为后廊)之后通常会有一段时间提供一个良好的黑色参考。这是夹紧的时间。

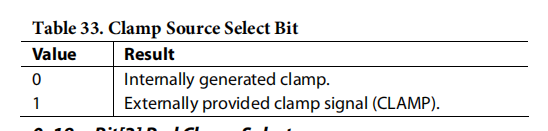

可以通过在适当的时间使用钳位源(寄存器0x18,位4)=1来简单地执行钳位销来建立钳位定时。该信号的极性由钳位极性位(寄存器0x1B,位[7:6])设置。

一种更简单的夹紧定时方法采用AD9984A内部夹紧定时发生器。钳制放置寄存器(寄存器0x19)使用在钳制开始之前应在Hsync的后缘之后经过的像素周期数进行编程。第二个寄存器clamp duration(寄存器0x1A)设置钳位的持续时间。这两个都是8位值,在钳位生成方面提供了相当大的灵活性。尽管Hsync持续时间可以有很大的变化,但是钳位定时是参考Hsync的后缘的,因为后廊(黑色参考)始终跟随Hsync。建立箝位的有效起点是将箝位设置为0x04(提供4个像素周期以使图形信号在同步后稳定),并将箝位持续时间设置为0x28(提供40个像素周期以重新建立黑色参考)。

夹紧是通过在外部输入耦合电容器上放置适当的电荷来完成的。这个电容器的值会影响钳位器的性能。如果太小,则在水平线时间(夹持间隔之间)内有显著的振幅变化。如果电容器太大,钳位器需要很长时间才能从输入信号偏移量的大变化中恢复过来。建议值(100 nF)导致在85赫兹XGA信号上从100 mV的阶跃误差恢复到60行中1 LSB以内,钳制持续时间为20个像素周期。

YPbPr夹紧

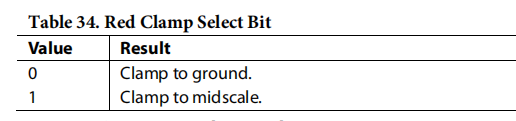

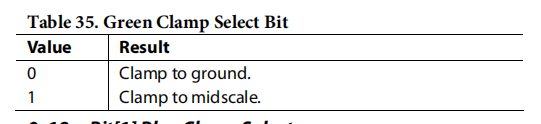

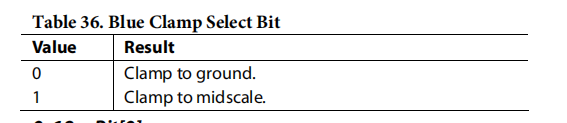

YPbPr图形信号与RGB信号略有不同,因为色差信号的dc参考电平(RGB信号中的黑色电平)位于视频信号的中点,而不是底部。这三个输入由亮度(Y)和色差(Pb和Pr)信号组成。对于色差信号,需要钳制到ADC范围(512)的中刻度范围而不是ADC范围(0)的底部,而Y通道钳制到地上。

通过在串行总线寄存器中设置钳位选择位,可以将钳位锁定到中刻度而不是接地。三个转换器中的每一个都有自己的选择位,使它们能够独立地固定在中刻度或地面上。这些位位于寄存器0x18位[3:1]。中标度参考电压由每个转换器内部产生。

增益和偏移控制

AD9984A包含三个可编程增益放大器(PGA),三个模拟输入端各一个。PGA的范围足以容纳输入信号,其输入范围为0.5v至1.0v满标度。增益设置在三个9位寄存器中:红色增益(寄存器0x05,寄存器0x06)、绿色增益(寄存器0x07,寄存器0x08)和蓝色增益(寄存器0x09,寄存器0x0A)。对于每个寄存器,0d的增益设置对应于最高增益,而511d的增益设置对应于最低增益。请注意,增加增益设置会导致图像的对比度降低。

偏移控制移动模拟输入,导致亮度变化。三个11位寄存器、红色偏移量(寄存器0x0B、寄存器0x0C)、绿色偏移量(寄存器0x0D、寄存器0x0E)和蓝色偏移量(寄存器0x0F、寄存器0x10)为每个通道提供独立设置。注意,偏移寄存器的功能取决于是否启用自动偏移(寄存器0x1B,位5)。

如果使用手动偏移,偏移寄存器的九位(对于红色通道,寄存器0x0B,位[6:0]加上寄存器0x0C,位[7:6])控制添加到通道的绝对偏移量。偏移控制提供±255 LSB的调整范围,1 LSB的偏移对应于1 LSB的输出代码。

自动偏移

除了手动偏移调整模式外,AD9984A还包括自动校准每个通道偏移的电路。通过在输入信号的后廊期间监视每个ADC的输出,AD9984A可以自我调整以消除其自身ADC信道中的任何偏移误差以及传入图形或视频信号中存在的任何偏移误差。

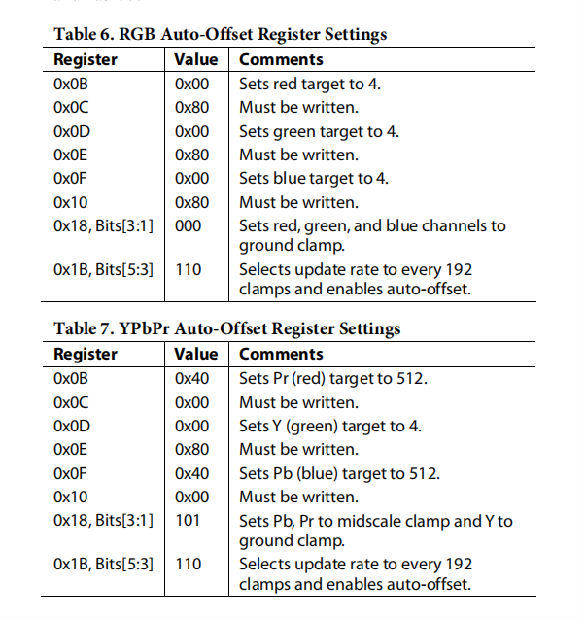

要激活自动偏移模式,请将寄存器0x1B的位5设置为1。接下来,必须对目标代码寄存器(寄存器0x0B到寄存器0x10)进行编程。编程到目标代码寄存器中的值应为AD9984A在后廊参考时间内所需的输出代码。

例如,对于RGB信号,所有三个寄存器通常编程为代码2,而对于Y Pb Pr信号,绿色(Y)通道通常编程为代码2,蓝色和红色通道(Pb和Pr)通常设置为512。目标代码寄存器每个通道有11位,并且是两个补码格式。这允许对-1024和+1023之间的任何值进行编程。尽管此范围内的任何值都可以编程,但AD9984A偏移范围可能无法达到每个值。预期目标代码值范围为(但不限于)接地夹紧时为-160至-1和+1至+160,中刻度夹紧时为350至670。请注意,目标代码0无效。

包含负目标代码以复制手动偏移调整中存在的功能。模拟的好处是能够轻松地调整显示器上的亮度。通过将目标代码设置为与理想ADC范围不对应的值,最终结果是图像变亮或变暗。高于理想值的目标代码会产生较亮的图像,而低于理想值的目标代码会产生较暗的图像。

编程目标代码的能力提供了很大的自由度和灵活性。尽管在大多数情况下,所有通道都设置为1或512,但选择其他值的灵活性使在通道之间插入有意的倾斜成为可能。它还允许ADC范围倾斜,以便可以数字化正常范围以外的电压。例如,将目标代码设置为40允许对通常低于黑色级别的同步提示进行数字化和评估。

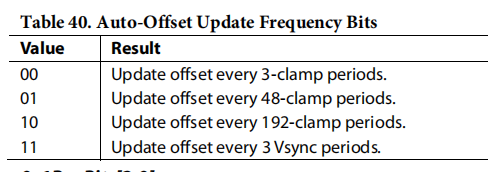

自动偏移电路的内部逻辑需要16个数据时钟周期才能执行其功能。此操作在夹紧脉冲后立即执行。因此,重要的是在激活视频之前结束钳位脉冲信号至少16个数据时钟周期。无论使用AD9984A内部钳位电路还是外部钳位信号,都是如此。自动偏移功能可编程为连续运行或一次性运行(见0x2C位[4]自动偏移保持部分)。在连续模式下,可以对更新频率进行编程(寄存器0x1B,位[4:3])。建议每192个Hsyncs更新一次。

基本自动偏移操作指南如表6和表7所示。

自动增益匹配

AD9984A包括将三个通道之间的增益匹配到彼此1%以内的电路。匹配每个通道的增益是在显示器上实现良好颜色平衡所必需的。在没有此功能的产品上,增益匹配是通过编写软件来实现的,该软件评估每个通道的输出,计算增益不匹配,然后将值写入每个通道的增益寄存器以进行补偿。具有自动增益匹配功能,不再需要此软件例程。要激活自动增益匹配,请将寄存器0x3C的位[2:0]设置为110。

自动增益匹配与自动偏移具有相似的时序要求。它需要16个数据时钟周期来执行其功能,在钳位脉冲结束后立即开始。与自动偏移不同,自动增益匹配不要求这16个时钟周期发生在后廊参考时间内,尽管建议这样做。在自动增益匹配操作期间,AD9984A的数据输出被冻结(保持在操作前的值)。自动增益匹配功能可编程为连续运行或一次性运行(参见0x3C位[3]自动增益匹配保持部分)。在连续模式下,可以对更新频率进行编程(寄存器0x1B,位[4:3])。建议每192个Hsyncs更新一次。

绿色同步

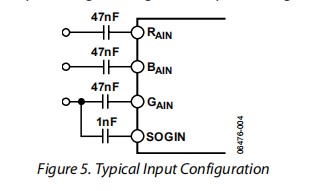

绿色输入上的同步(SOGIN0,SOGIN1)分两步操作。首先,他们用一个负峰值检测器来设置一个基线钳制电平。其次,他们将SOG切片器比较器(寄存器0x1D,位[7:3])的电压电平设置为负峰值以上的可编程电平(通常为128 mV)。每个sync ongreen输入必须通过自己的电容器与绿色模拟输入进行交流耦合。电容器的值必须为1 nF±20%。如果不使用绿色同步,则不需要此连接。绿色同步信号总是具有负极性。

参考旁路

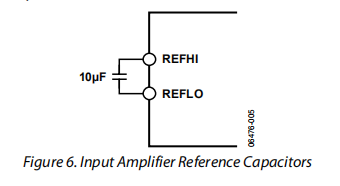

REFLO和REFHI通过10μF电容器相互连接(见图6)。输入ADC电路使用这些参考。

时钟产生

PLL用于产生像素时钟。Hsync输入为PLL提供参考频率。压控振荡器(VCO)产生更高的像素时钟频率。像素时钟除以PLL除法值(寄存器0x01和寄存器0x02)并与Hsync输入相比较。任何错误都被用来转移VCO频率并保持两个信号之间的锁定。

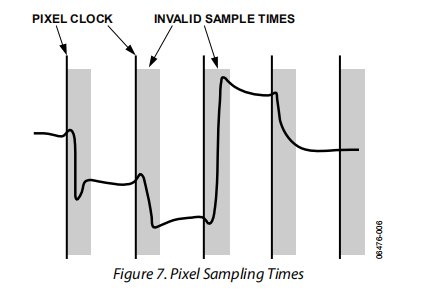

这个时钟的稳定性是提供最清晰和最稳定图像的一个非常重要的因素。在每一个像素时间内,信号从旧像素振幅转换并固定在其新值;这称为转换时间。然后,输入电压在信号必须转换到新值之前稳定下来;这称为稳定时间。回转时间与稳定时间的比值是图形DAC带宽和传输系统带宽(电缆和终端)的函数。这个比率也是整体像素率的函数。如果系统的动态特性保持不变,回转和稳定时间也同样是固定的。必须从总像素周期中减去此时间,以保留稳定周期。在较高的像素频率下,总循环时间更短,稳定像素时间也更短。

时钟中的任何抖动都会降低采样时间的精度,还必须从稳定像素时间中减去它。在AD9984A时钟产生电路的设计中,为了使抖动最小化,已经采取了相当谨慎的措施。在所有工作模式下,AD9984A的时钟抖动都很低,使得由于抖动而导致的有效采样时间减少可以忽略不计。

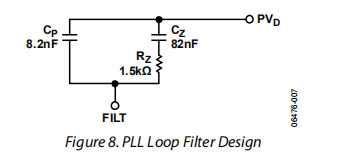

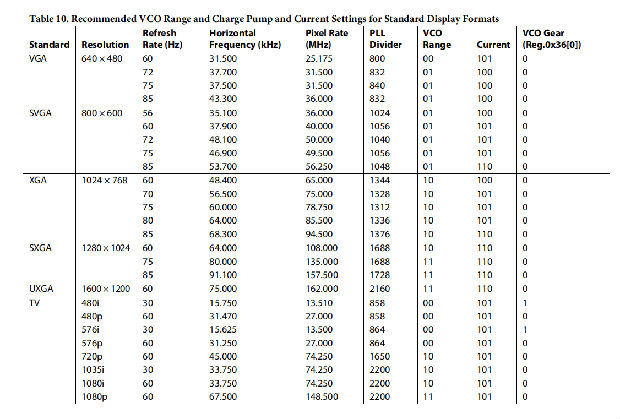

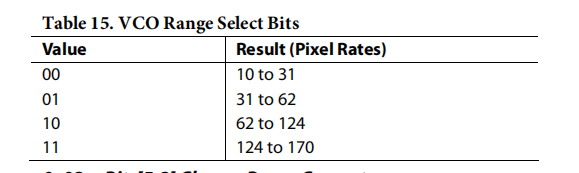

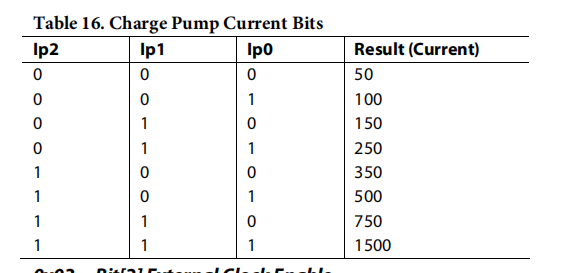

锁相环特性由环路滤波器设计、锁相环电荷泵电流和VCO范围设置决定。环路滤波器的设计如图8所示。表10列出了VESA标准显示模式的VCO范围和电荷泵电流的建议设置。

提供四个可编程寄存器以优化PLL的性能。这些寄存器是12位除数寄存器、2位VCO范围寄存器、3位电荷泵电流寄存器和5位相位调整寄存器。

12位除数寄存器

只要Hsync和PLL除数的乘积在VCO的工作范围内,输入的Hsync频率就可以容纳任何Hsync。PLL将Hsync信号的频率相乘,产生10mhz到170mhz范围内的像素时钟频率。除数寄存器控制精确的乘法因子。只要输出频率在范围内,该寄存器可以设置为2到4095之间的任何值。

2位VCO范围寄存器

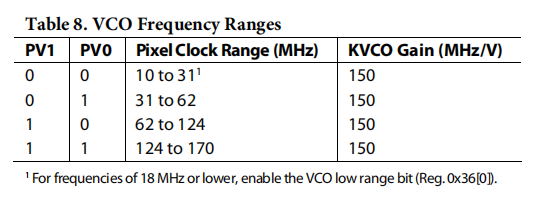

为了提高AD9984A的噪声性能,将VCO的工作频率范围划分为四个重叠区域。VCO范围寄存器设置此工作范围。四个区域的频率范围如表8所示。

三位电荷泵电流寄存器

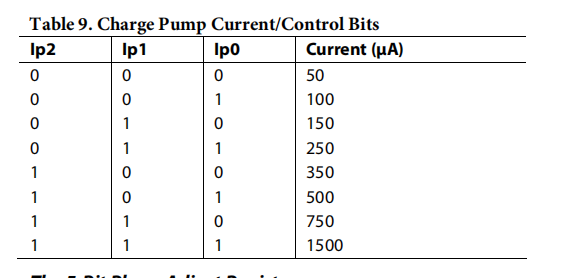

该寄存器改变驱动低通环路滤波器的电流。表9列出了可能的电流值。

5位相位调整寄存器

所生成的采样时钟的相位可以偏移以在时钟周期内定位最佳采样点。相位调整寄存器提供32个移相步骤,每个步骤11.25°。具有相同相移的Hsync信号可通过HSOUT引脚获得。如果使用外部像素时钟,相位调整仍然可用。COAST pin或内部COAST用于允许PLL在没有输入Hsync信号的情况下或在Hsync中的干扰(例如来自均衡脉冲)期间以相同的频率继续运行。这可以在垂直同步期间或在Hsync信号不可用的任何其他时间使用。

可通过海岸极性寄存器(寄存器0x18,位[6:5])设置海岸信号的极性。此外,可以通过Hsync极性寄存器(寄存器0x12,位[5:4])设置Hsync信号的极性。对于Hsync和coast,值1为高激活状态。内部滑行功能由Vsync信号驱动,该信号通常是Hsync信号可被额外均衡脉冲干扰的时间。

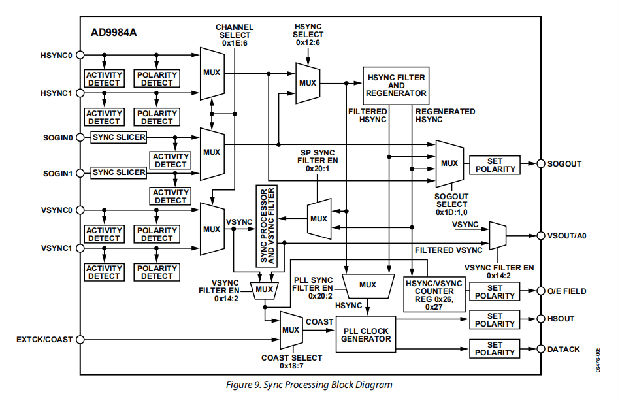

同步处理

AD9984A的sync处理部分的输入是数字Hsyncs和Vsyncs、模拟sync ongreen或sync-on-Y信号以及可选的外部海岸信号的组合。从这些信号中,部件从其锁相环生成精确的无抖动时钟、奇偶场信号、HSOUT和VSOUT信号、每个Vsync的hsync计数和可编程SOGOUT。主要的同步处理块是同步切片器、同步分离器、Hsync滤波器、Hsync再生器、Vsync滤波器和coast生成器。

•同步切片器从连接到SOGINx输入的绿色图形或亮度视频信号中提取同步信号,并输出数字复合同步。

•同步分离器从复合同步信号中提取Vsync,该信号可以来自同步切片器或HSYNCx输入。

•Hsync滤波器用于消除HSYNCx或SOGINx输入中的任何无关脉冲,输出适合模式检测和时钟生成的干净、低抖动信号。

•Hsync再生器用于重新创建干净的Hsync信号,虽然不是低抖动,但可以用于模式检测和计算每个Vsync的Hsync。

•Vsync滤波器用于消除杂散Vsync,在Vsync和Hsync输出信号之间保持稳定的时序关系,并产生奇偶场输出。

•海岸发生器产生一个稳健的海岸信号,允许锁相环在没有Hsync脉冲的情况下保持其频率。

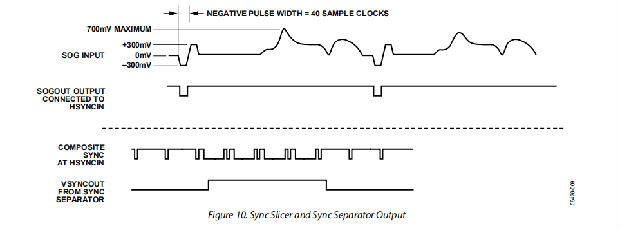

同步切片器

同步切片器的目的是从连接到SOG输入的绿色图形或亮度视频信号中提取同步信号。同步信号在两步过程中提取。首先,SOG输入被钳制到其负峰值(通常比黑电平低0.3v)。接下来,信号进入具有可变触发电平(由寄存器0x1D设置,位[7:3])的比较器,但名义上高于钳位电平0.128 V。同步切片器输出是一个包含Hsync和Vsync信息的数字复合同步信号(参见图10)。

同步分离器

作为同步处理的一部分,同步分离器的任务是从复合同步信号中提取Vsync。它的工作原理是Vsync信号比Hsync信号保持活动的时间长得多。通过使用数字低通滤波器和数字比较器,同步分离器拒绝持续时间较短的脉冲(如hsync和均衡脉冲),只通过持续时间较长的脉冲,如Vsync(见图10)。

数字比较器的阈值可编程以获得最大的灵活性。要编程阈值持续时间,请将值(N)写入寄存器0x11。得到的脉冲宽度为N×200ns。例如,如果N=5,则数字比较器阈值为1μs。任何小于1μs的脉冲被拒绝,而任何大于1μs的脉冲通过。

使用同步分隔符时要记住两个因素。首先,得到的干净Vsync输出从原始Vsync延迟等于数字比较器阈值(N×200ns)的持续时间。其次,200ns倍增值存在一定的可变性。所有操作条件下的最大可变性为±20%(160 ns至240 ns)。因为正常的Vsync和Hsync脉冲宽度相差大约500倍或更多,所以20%的变异性不是问题。

同步滤波器和再生器

Hsync滤波器用于消除Hsync或SOG输入中的任何无关脉冲,输出适合于模式检测和时钟生成的干净、低抖动信号。Hsync再生器用于重新创建干净但不低抖动的Hsync信号,该信号可用于模式检测和计算每个Vsync的Hsync。Hsync再生器对Hsync输入上的无关脉冲和丢失脉冲具有高度的容忍度,但不适合PLL用于由于抖动而创建像素时钟。

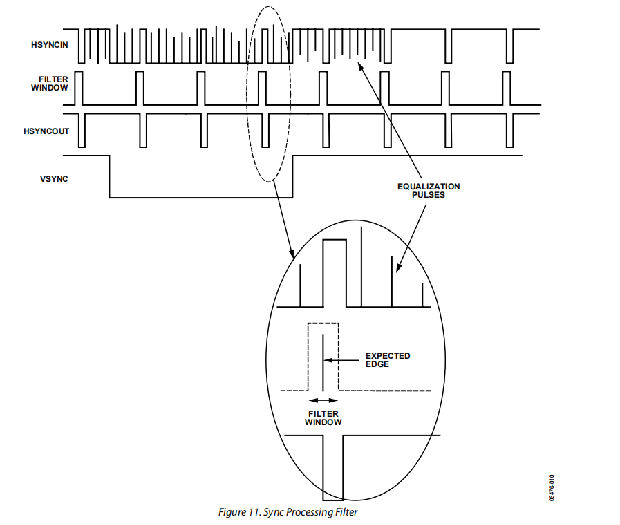

Hsync再生器自动运行,无需设置即可运行。Hsync筛选器需要设置筛选器窗口。过滤器窗口在允许出现有效Hsync的重新生成Hsync前缘周围设置一个周期时间窗口。一般的想法是,同步输入上的无关脉冲发生在这个滤波器窗口之外,因此被过滤掉。要设置过滤器窗口计时,请将值(x)编程到寄存器0x23中。产生的滤波器窗口时间是围绕再生Hsync前缘的±x乘以25 ns。与同步分离器阈值倍增器一样,允许25 ns倍增器中存在±20%的差异,以说明所有操作条件(20 ns至30 ns范围)。

Hsync滤波器的第二个输出是一个状态位(寄存器0x25,位1),它指示输入同步信号上是否存在无关脉冲。外部脉冲通常用于复制保护目的,因此此状态位可用于检测此类脉冲。

由PLL生成像素时钟的滤波Hsync(而不是原始HSYNCx/SOGINx信号)由寄存器0x20第2位控制。同步处理的再生Hsync(而不是原始HSYNCx/SOGINx信号)由寄存器0x20第1位控制。建议使用过滤后的Hsync和重新生成的Hsync。有关过滤的Hsync的说明,请参见图11。

Vsync滤波器与奇偶域

Vsync滤波器用于消除杂散Vsync,保持Vsync和Hsync输出信号之间稳定的时序关系,并产生奇偶场输出。

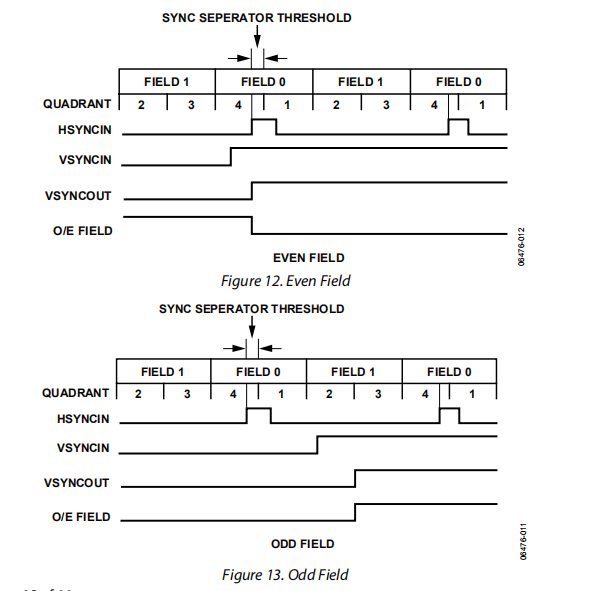

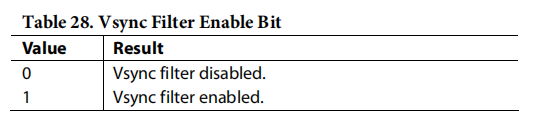

过滤器的工作原理是检查Vsync相对于Hsync的位置,如有必要,稍微及时地移动它。其目的是防止Vsync和Hsync前沿同时切换,从而消除帧的第一行何时发生的混淆。寄存器0x14,位2启用Vsync筛选器。建议在所有情况下(包括隔行扫描视频)使用Vsync滤波器,并且在使用每个Vsync计数器的hsync时需要使用该滤波器。图12和图13说明了两种情况下的奇偶场确定。

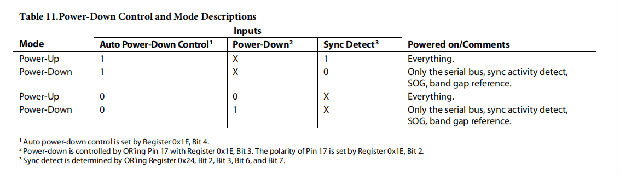

电源管理

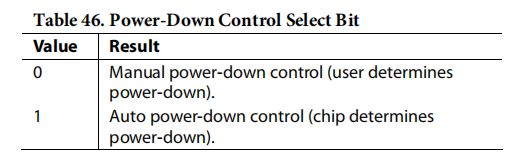

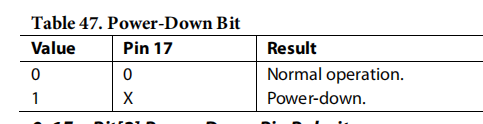

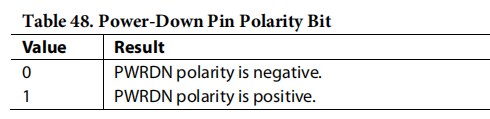

为了满足低待机功率的显示要求AD9984A包括断电模式。断电状态可以手动(通过引脚17或寄存器0x1E,位3)控制,也可以由芯片自动控制。如果选择了自动控制(寄存器0x1E,位4=1),则AD9984A的决定基于寄存器0x24中以下同步检测位的状态:位2、位3、位6和位7。如果在任何输入上检测到Hsync或sync on green输入,则芯片将通电;否则,它将断电。对于手动控制,AD9984A允许通过专用引脚和寄存器位灵活控制。对于专用管脚,硬件看门狗电路控制断电,而软件控制寄存器位的断电。使用手动断电控制时,无论是否使用该引脚,都必须设置断电引脚的极性(寄存器0x1E,位2)。如果未使用,建议将极性设置为高活性,并用10 kΩ电阻将引脚硬接线接地。

在断电模式下,几个电路继续正常工作。串行寄存器和同步检测电路保持电源,以便AD9984A可以从断电状态唤醒。带隙电路保持电源,因为同步检测需要它。绿色同步和SOGOUT功能继续工作,因为当同步检测由辅助芯片执行时,需要SOGOUT。所有这些电路都需要最小的功率才能工作。AD9984A的典型待机功率约为50兆瓦。

断电时有两个选项可供选择。这些由寄存器0x1E中的位0和位1控制。位0控制SOGOUT管脚是否处于高阻抗。在大多数情况下,用户在正常操作期间不会将渗液置于高阻抗中。将渗水沟置于高阻抗的选项主要包括允许工厂测试模式。位1保持AD9984A通电,同时仅将输出置于高阻抗。当两个芯片的数据输出连接到一个PCB上,并且用户希望在这两个芯片之间即时切换时,此选项非常有用。

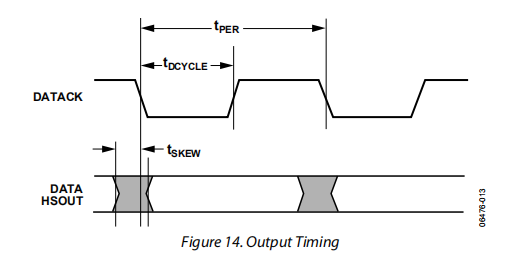

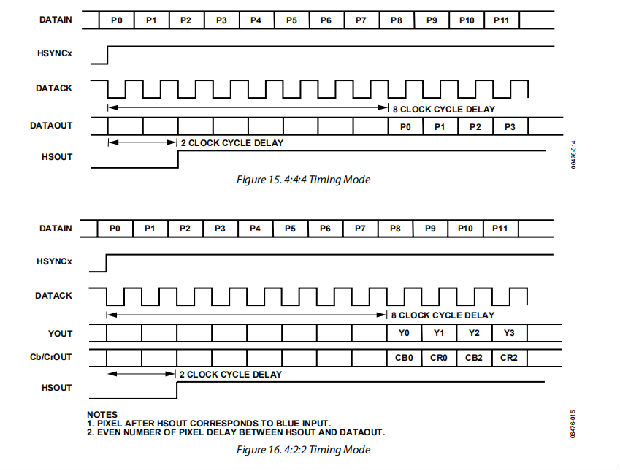

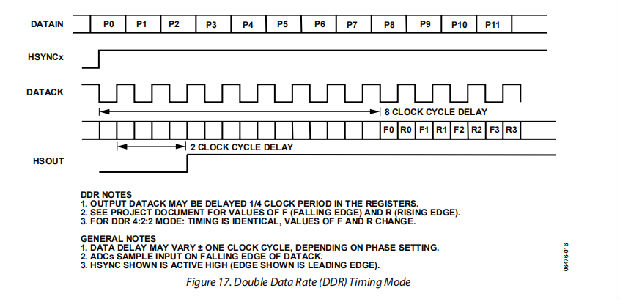

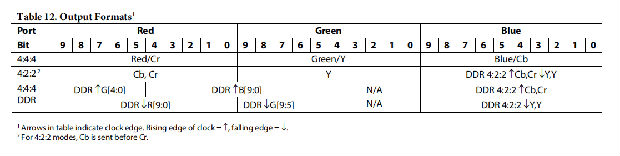

时序图

图14至图17中的时序图显示了AD9984A的工作情况。创建输出数据时钟信号时,其上升沿总是发生在数据转换之间,可用于外部锁定输出数据。AD9984A中有一个管道,必须先刷新该管道,然后才能获得有效数据。这意味着在有效数据可用之前存在六个数据集。

同步定时

在AD9984A中处理Hsync以消除歧义在相对于相位分层像素时钟和数据的前缘的定时中。

Hsync输入用作生成像素采样时钟的参考。可通过相位调整寄存器(以优化像素采样时间)在32个步骤中通过全360°相对于Hsync调整采样相位。显示系统使用Hsync来对齐内存和显示写入周期。

因此,在Hsync输出(HSOUT)和数据时钟(DATACK)之间保持稳定的时序关系是非常重要的。

在AD9984A中,Hsync有三种情况。首先,确定Hsync输入的极性,并因此具有已知的输出极性。已知输出极性可编程为高激活或低激活(寄存器0x12,位3)。其次,HSOUT与数据包和数据输出对齐。第三,HSOUT(像素时钟)的持续时间通过寄存器0x13设置。HSOUT是应该用来驱动显示系统其余部分的同步信号。

滑行时间

在大多数计算机系统中,Hsync信号是通过一根专用线连续提供的。在这些系统中,海岸输入和功能是不必要的,不应使用。

然而,在某些系统中,Hsync在垂直同步期间(Vsync)受到干扰。在某些情况下,Hsync脉冲消失。在其他系统中,例如那些采用复合同步(Csync)信号或嵌入绿色同步的系统,Hsync可以在Vsync期间包括均衡脉冲或其他失真。为了避免在Vsync期间扰乱时钟生成器,忽略这些失真是很重要的。如果像素时钟PLL看到外部脉冲,它会尝试锁定到这个新频率,并在Vsync周期结束时改变频率。然后,需要几行正确的Hsync定时才能在新帧开始时恢复,从而导致显示器顶部的图像撕裂。

提供海岸输入以消除此问题。它是一个异步输入,禁用PLL输入并将时钟保持在当前频率。锁相环可以自由运行几条线路,而无明显的频率漂移。Coast可以由AD9984A内部生成(参见寄存器0x18),也可以由图形控制器外部提供。

当选择内部coast(寄存器0x18,位7=0,寄存器0x14,位[7:6]选择源)时,Vsync用作确定coast位置的基础。内部滑行信号在周期性Vsync信号(预广播寄存器0x16)之前启用编程的Hsync周期数,在Vsync之后丢弃编程的Hsync周期数(后绿洲寄存器0x17)。建议在使用内部滑行功能时启用Vsync滤波器,以允许AD9984A精确确定hsync/Vsync的数量及其位置。在许多发生中断并使用coast的应用中,值2表示预播,值10d表示后烤,足以避免大多数无关脉冲。

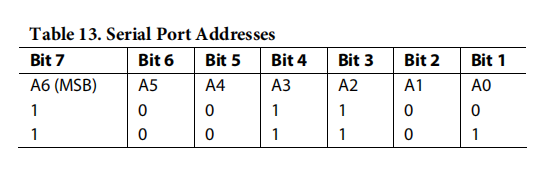

输出格式化程序

输出格式化程序能够生成若干输出格式,以呈现给30个数据输出管脚。表12列出了每种格式的输出格式和管脚分配。此外,输出时钟有几个时钟选项。用户可以选择像素时钟、90°移相像素时钟、2×像素时钟或0.5×像素时钟进行测试。输出时钟也可以反转。

数据输出可用作30针RGB或YCbCr,或者,如果选择4:2:2或4:4:4 DDR,则可以使用辅助通道。这个次通道总是4:2:2 DDR。它包含与主通道相同的视频数据,可由另一个显示或存储设备使用。根据输出模式的选择,主输出可以是30个管脚、20个管脚,或者只有15个管脚。

模式描述

4:4:4

所有通道同时输出10个数据位。

数据与时钟的负边缘对齐,便于捕获。

这是RGB或4:4:4 YCbCr的正常30位输出模式。

4:2:2

红色和绿色通道包含4:2:2格式化数据(20针),绿色通道上有Y数据,红色通道上有Cb、Cr数据。数据与时钟的负边缘对齐。蓝色通道包含具有Cb、Y、Cr、Y格式的4:2:2 DDR数据的次要通道。数据边缘与像素时钟的两个边缘对齐,因此,可能需要使用90°时钟来捕获DDR数据。

4:4:4解甲还原酶

在蓝色频道,如4:2:2模式。

R G B[29:0]=R[9:0]+G[9:0]+B[9:0],所以RGB[29:15]=R[9:0]+G[9:5]和RGB[14:0]=G[4:0]+B[9:0]。

2线串行控制端口

AD9984A配有一个2线串行控制接口。最多可以将两个AD9984A设备连接到2线串行接口,每个设备都有一个唯一的地址。

2线串行接口包括时钟(SCL)和双向数据(SDA)管脚。模拟平板接口用作通过串行接口接收和传输数据的从机。当串行接口未激活时,SCL和SDA上的逻辑电平被外部上拉电阻器拉高。

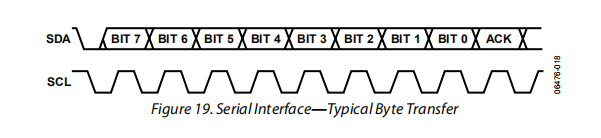

SDA线上接收或传输的数据必须在SCL正向脉冲期间保持稳定。只有当SCL低时,SDA上的数据才能更改。如果在SCL高时SDA改变状态,串行接口将该操作解释为启动或停止序列。

以下是串行总线操作的五个组件:

•启动信号

•从机地址字节

•基址寄存器地址字节

•读取或写入数据字节

•停车信号

当串行接口处于非活动状态(SCL和SDA高)时,通过发送启动信号启动通信。当SCL高时,SDA上的启动信号是从高到低的转换。此信号提醒所有从属设备数据传输序列即将到来。

在开始信号之后传输的前8位数据包括7位从地址(前7位)和单个R/W位(第八位)。R/W位表示从设备上从1读取或写入0的数据传输方向。如果发送的从机地址与设备地址匹配,则AD9984A通过使第九个SCL脉冲的SDA低来确认匹配。如果地址不匹配,则AD9984A不确认。

通过串行接口传输数据

对于读或写的每个数据字节,MSB是序列中的第一位。如果在写入序列期间AD9984A不确认主设备,则SDA保持高,以便主设备可以生成停止信号。如果主设备在读取序列期间未确认AD9984A,则AD9984A将其解释为数据结束。SDA保持在高位,以便主机可以生成停止信号。

将数据写入AD9984A的特定控制寄存器需要在建立从机地址后写入感兴趣的控制寄存器的8位地址。此控制寄存器地址是后续写入操作的基址。写入初始数据字节后,每个附加数据字节的基址自动递增一个。如果传输的字节数超过可用地址,则地址不会递增,并保持其最大值0x44。任何高于0x44的基址都不会产生确认信号。以类似的方式从AD9984A的控制寄存器读取数据。读取需要两个数据传输操作。

•基地址必须用从地址字节的R/W位低位写入,以建立顺序读取操作。读取(从机地址字节高的R/W位)从先前建立的基址开始。读取寄存器的地址在每个字节传输后自动递增。

•要终止对AD9984A的读/写序列,必须发送停止信号。停止信号包括当SCL高时SDA从低到高的转换。

当驱动串行接口的主设备在不首先生成停止信号以终止当前通信的情况下生成启动信号时,发生重复的启动信号。这用于在不释放串行接口线的情况下更改从机和主机之间的通信模式(读、写)。

串行接口读/写示例

写入一个控制寄存器

1、启动信号

2、从地址字节(R/W位=低)

3、基址字节

4、数据字节到基址

5、停车信号

写入四个连续的控制寄存器

1、启动信号

2、从地址字节(R/W位=低)

3、基址字节

4、数据字节到基址

5、数据字节到(基址+1)

6、数据字节到(基址+2)

7、数据字节到(基址+3)

8、停车信号

从一个控制寄存器读取

1、启动信号

2、从地址字节(R/W位=低)

3、基址字节

4、启动信号

5、从地址字节(R/W位=高)

6、来自基地址的数据字节

7、停车信号

从四个连续控制寄存器读取

1、启动信号

2、从地址字节(R/W位=低)

3、基址字节

4、启动信号

5、从地址字节(R/W位=高)

6、来自基地址的数据字节

7、数据字节从(基址+1)

8、数据字节从(基址+2)

9、数据字节从(基址+3)

10、停车信号

2线串行控制寄存器

芯片识别

0x00位[7:0]芯片版本

这是一个8位寄存器,表示硅版本。

分频器控制

0x01位[7:0]PLL除法比MSBs

这些是12位PLL除法比(PLLDIV)的8个MSBs。

PLL从输入的Hsync信号导出像素时钟。然后将像素时钟频率除以整数值,使得输出被相位锁定到Hsync。该PLLDIV值确定每行的像素次数(像素加上水平消隐开销)。这通常比显示中的活动像素数多20%到30%。

只要输出频率在范围内,PLL分频器的12位值支持从2到4095的分频比。该寄存器中加载的值越高,相对于固定的Hsync频率,得到的时钟频率就越高。

VESA已经建立了一些标准的定时规范,帮助确定PLLDIV的值作为水平和垂直显示分辨率和帧速率的函数(见表10)。然而,许多计算机系统并不完全符合这些建议。因此,这些数字只能作为参考。显示系统制造商应提供自动或手动优化PLLDIV的方法。设置不正确的PLLDIV通常会在显示屏上产生一个或多个垂直噪声条。误差越大,产生的钢筋数量就越多。

PLLDIV的加电默认值为1693。PLLDIVM=0x69,PLLDIVL=0xDX。

AD9984A仅在写入LSB时更新全除法比。单独写入此寄存器不会触发更新。0x02位[7:4]PLL除比lsb这是12位PLL除法比(PLLDIV)的四个lsb。PLLDIV的加电默认值为1693。PLLDIVM=0x69,PLLDIVL=0xDX。

时钟发生器控制

0x03位[7:6]VCO范围选择

这两位确定了时钟发生器的工作范围。VCO范围必须设置为与所需工作频率(输入像素速率)相对应。锁相环在高频下具有最佳的抖动性能。因此,为了输出低像素速率并且仍然获得良好的抖动性能,PLL以更高的频率工作,但是随后将时钟速率除以。每个VCO范围设置的像素速率见表15。PLL输出除数由VCO范围设置自动选择。通电默认值为01。

0x03位[5:3]电荷泵电流

这三位建立了驱动时钟发生器中环路滤波器的电流。必须将电流设置为与所需工作频率相对应。通电默认值为current=001。

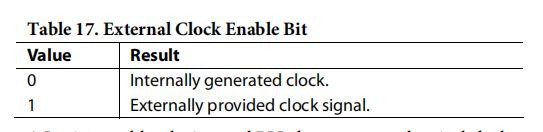

0x03位[2]外部时钟启用

这个位元决定像素时钟的来源。

逻辑0启用从外部提供的Hsync生成像素时钟的内部PLL。

逻辑1启用外部EXTCK输入引脚。在这种模式下,PLL除法比(PLLDIV)被忽略。时钟相位调整(相位)仍然有效。通电默认值为EXTCK=0。

相位调整

0x04位[7:3]ADC时钟相位调整

这些位调整DLL的相位以生成ADC时钟。5位值在一个像素时间内以32步调整采样相位。每一步代表取样阶段的11.25°位移。开机默认值为16。

输入增益

AD9984A可容纳满标度范围在0.5 V和1.0 V p-p之间的输入信号。将红色、绿色或蓝色通道增益设置为511对应于1.0 V的输入范围。红色、绿色,或蓝色通道增益0建立0.5 V的输入范围。注意,增加增益会导致图像的对比度降低(输入信号使用的可用转换器代码更少)。

0x05位[6:0]红色通道增益控制MSBs

此寄存器包含红色通道增益控制的7位MSBs。写入此寄存器的值在LSB寄存器(寄存器0x06)也写入之前不会更新。开机默认值为1000000。

0x06-位[7:6]红色通道增益控制LSB

该寄存器包含红色通道增益控制的2位LSB。除了寄存器0x05中的7个增益控制MSBs外,还有9个增益控制位。默认通电值为00。

0x07位[6:0]绿色通道增益控制MSBs

此寄存器包含绿色通道增益控制的7位MSBs。寄存器更新需要将0x00写入寄存器0x08。

0x08位[7:6]绿色通道增益控制LSB

此寄存器包含绿色通道增益控制的2位LSB。除了寄存器0x07中的7个增益控制MSBs外,还有9个增益控制位。默认通电值为00。

0x09位[6:0]蓝色通道增益控制MSBs

此寄存器包含蓝色通道增益控制的7位MSBs。寄存器更新需要写入0x00以注册0x0A。

0x0A位[7:6]蓝色通道增益控制LSB

该寄存器包含蓝色通道增益控制的2位LSB。除了寄存器0x09中的7个增益控制MSBs外,还有9个增益控制位。默认通电值为00。

输入偏移量

偏移控制移动模拟输入,导致亮度变化。注意,红色、蓝色或绿色通道偏移寄存器的功能取决于是否启用自动偏移(寄存器0x1B,位5)。

如果禁用自动偏移,则偏移寄存器的九位(偏移MSB寄存器的位[6:0]加上以下寄存器的位[7:6])控制添加到通道的绝对偏移量(对于红色通道,寄存器0x0B,位[6:0]加上寄存器0x0C,位[7:6])控制添加到通道的绝对偏移量。偏移控制提供一个±255 LSB的调整范围,1 LSB的偏移对应于1 LSB的输出代码。

如果启用了自动偏移,则11位偏移量(由MSB寄存器的8位和以下LSB寄存器的位[7:5]组成)确定钳位目标代码。11位偏移量由1个符号位加10位组成。如果寄存器编程为530d,则在钳位周期结束时,输出代码等于530d。注意,不管自动偏移设置如何,将偏移寄存器设置增加1lsb会增加1lsb的偏移量。

0x0B位[7:0]红色通道偏移控制MSBs

此寄存器是红色通道偏移控制的8位MSBs。除了寄存器0x0C中红色通道偏移中的3个lsb外,红色通道中还有11位dc偏移控制。写入此寄存器的值在LSB寄存器(寄存器0x0C)也写入之前不会更新。

0x0C位[7:5]红色通道偏移控制LSB

此寄存器包含红色通道偏移控制的3位LSB。将这些位与寄存器0x0B中的MSBs的8位组合将创建11位偏移控制。

0x0D位[7:0]绿色通道偏移控制MSBs

此寄存器包含绿色通道偏移控制的8位MSBs。只有当寄存器0x0E也写入时,才会更新此寄存器。

0x0E位[7:5]绿色通道偏移控制LSB

此寄存器包含绿色通道偏移控制的3位LSB。将这些位与寄存器0x0D中的MSBs的8位相结合,可以生成11位偏移控制。

0x0F位[7:0]蓝色通道偏移控制MSBs

8位蓝色通道偏移控制。仅当寄存器0x10也写入时,才会更新此寄存器。

0x10位[7:5]蓝色通道偏移控制LSB

蓝色通道偏移控制的lsb与寄存器0x0F中的MSBs的8位组合,形成11位偏移控制。

同步控制

0x11位[7:0]同步分隔符阈值

此寄存器设置同步分离器的数字比较器的阈值。写入该寄存器的值乘以200 ns,得到阈值。因此,如果写入值5,则数字比较器阈值为1μs,并且同步分离器拒绝小于1μs的任何脉冲。200ns倍增值有一些变化。所有操作条件下的最大可变性为±20%(160 ns至240 ns)。因为正常的Vsync和Hsync脉冲宽度相差大约500倍或更多,所以20%的变异性不是问题。通电默认值为32d。

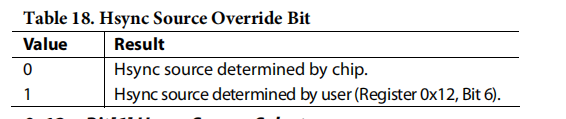

0x12位[7]Hsync源重写

此位是Hsync源重写。将此位设置为0允许芯片确定活动的Hsync源。将其设置为1使用寄存器0x12的位6来确定活动的Hsync源。通电默认值为0。

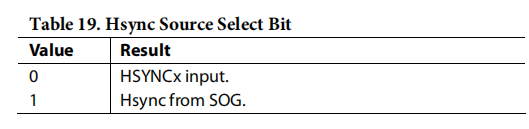

0x12位[6]Hsync源选择

该位选择用于PLL和同步处理的Hsync的源(仅当寄存器0x12的位7设置为1或两个同步都处于活动状态时)。

将此位设置为0指定输入端的Hsync。

将其设置为1将从SOG中选择Hsync。开机默认值为0。

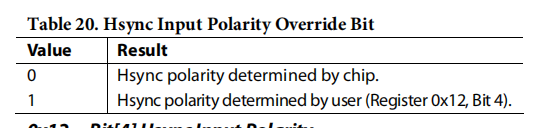

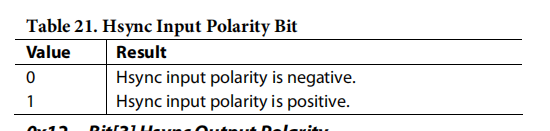

0x12位[5]Hsync输入极性超控

该位决定芯片是否选择Hsync输入极性或是否指定。将该位设置为0允许芯片自动选择输入Hsync的极性。将其设置为1表示寄存器0x12的位4指定极性。开机默认值为0。

0x12位[4]Hsync输入极性

如果寄存器0x12的第5位是1,则该位的值指定输入Hsync的极性。将此位设置为0表示Hsync输入极性为负。将该位设置为1表示Hsync输入极性为正。开机默认值为1。

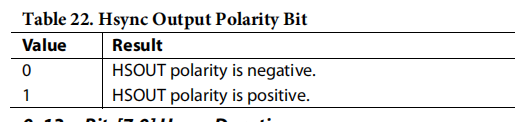

0x12位[3]Hsync输出极性

该位设置Hsync输出(HSOUT)的极性。将此位设置为0表示HSOUT极性为负。将该位设置为1表示HSOUT极性为正。

0x13位[7:0]Hsync持续时间

这个8位寄存器设置HSOUT脉冲的持续时间。Hsync输出的前沿由内部产生的相位调整PLL反馈时钟触发。然后,AD9984A计算与该寄存器中的值相等的像素时钟数。这会触发HSOUT的后缘,该后缘也是相位调整的。

同步控制

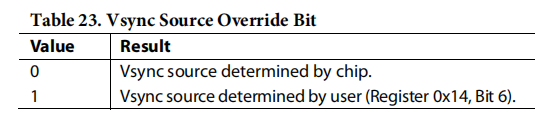

0x14位[7]Vsync源重写

此位是活动的Vsync覆盖。将此设置为0允许芯片确定活动的Vsync源,将其设置为1使用寄存器0x14的位6来确定活动的Vsync源。通电默认值为0。

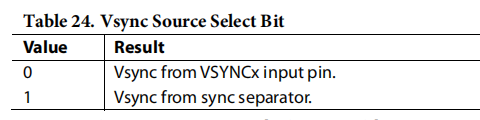

0x14位[6]Vsync源选择

仅当寄存器0x14的位7设置为1时,该位才选择用于同步处理的Vsync源。将位6设置为0指定来自输入管脚的Vsync。将其设置为1将从同步分隔符中选择Vsync。开机默认值为0。

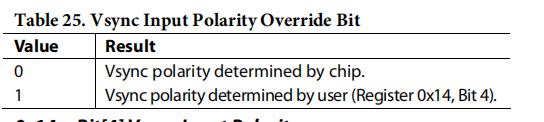

0x14位[5]Vsync输入极性覆盖

该位设置芯片是否选择Vsync输入极性或是否指定了该极性。将该位设置为0允许芯片自动选择输入Vsync的极性。将该位设置为1表示寄存器0x14的位4指定极性。开机默认值为0。

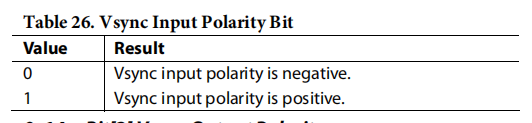

0x14位[4]Vsync输入极性

如果寄存器0x14的第5位是1,则该位的值指定输入Vsync的极性。将此位设置为0表示Vsync输入极性为负。将此位设置为1表示Vsync输入极性为正。开机默认值为1。

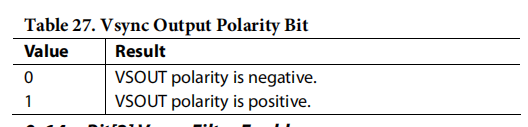

0x14位[3]Vsync输出极性

该位设置Vsync输出(VSOUT)的极性。将此位设置为0表示VSOUT极性为负。将该位设置为1表示电压输出极性为正。开机默认值为1。

0x14位[2]Vsync筛选器启用

该位使Vsync滤波器能够允许Vsync相对于Hsync的精确位置,并促进Hsyncs/Vsync计数的正确操作。

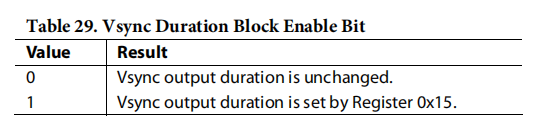

0x14位[1]Vsync持续时间块启用

这将启用Vsync duration块,该块设计用于Vsync筛选器。将位设置为0将使Vsync输出持续时间保持不变。将位设置为1将基于寄存器0x15设置Vsync输出持续时间。通电持续时间为0。

0x15位[7:0]Vsync持续时间

此寄存器用于设置Vsync的输出持续时间,并设计为与Vsync筛选器一起使用。仅当寄存器0x14的位1设置为1时,此选项才有效。开机默认为10d。

滑行和夹紧控制

0x16位[7:0]预播

该寄存器允许在Vsync信号之前应用内部生成的滑行信号。这在存在预均衡脉冲的情况下是必要的。此控件的步长为一个Hsync周期。要使预广播正常工作,必须启用或禁用Vsync筛选器(寄存器0x14,位2)和同步处理筛选器(寄存器0x20,位1)。开机默认值为00。

0x17位[7:0]后处理

该寄存器允许在Vsync信号之后应用内部生成的滑行信号。这在存在均衡后脉冲的情况下是必要的。此控件的步长为一个Hsync周期。要使后处理正常工作,必须启用或禁用Vsync筛选器(寄存器0x14,位2)和同步处理筛选器(寄存器0x20,位1)。开机默认值为00。

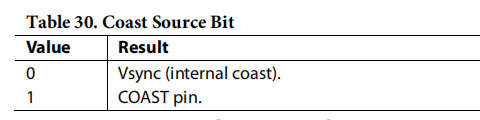

0x18位[7]海岸源

此位用于选择活动海岸源。可选择COAST输入引脚或Vsync。如果选择了Vsync,则需要作出使用VSYNCx输入管脚或同步分离器输出的附加决定(寄存器0x14,位[7:6])。

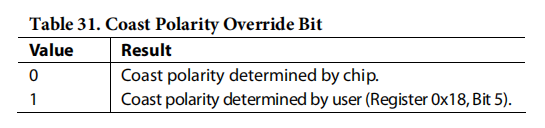

0x18位[6]滑行极性超控

该寄存器用于覆盖确定进入锁相环的海岸信号极性的内部电路。开机默认设置为0。

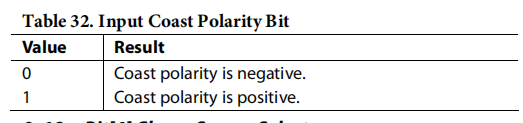

0x18位[5]输入滑行极性

当寄存器0x18的位6为1时,该寄存器设置输入滑行极性。开机默认设置为1。

0x18位[4]钳位源选择

该位决定了钳位定时的来源。0启用由钳位和钳位持续时间控制的钳位定时电路。夹持位置和持续时间从Hsync的前缘开始计算。A 1启用外部夹紧输入引脚。当钳位信号激活时,三个通道被钳位。钳位极性由钳位极性决定。通电默认设置为0。

0x18位[3]红色钳位选择

此位确定红色通道是固定在地面上还是固定在中刻度上。通电默认设置为0。

0x18位[2]绿色钳位选择

该位确定绿色通道是固定在地面上还是固定在中刻度上。开机默认设置为0。

0x18位[1]蓝色钳位选择

该位决定蓝色通道是固定在地面上还是固定在中刻度上。开机默认设置为0。

0x18位[0]

必须设置为0才能正常运行。

0x19位[7:0]钳位

一种8位寄存器,用于设置内部产生的钳位器的位置。当钳位源选择=0(寄存器0x18,位4)时,在由该寄存器建立的位置和钳位持续时间寄存器(寄存器0x1A)设置的持续时间内产生钳位信号。在Hsync后缘之后的像素周期的钳位计数处开始钳位。夹钳位置可以编程为1到255之间的任意值。不支持值0。

钳位应该放置在输入信号呈现稳定的黑电平基准的时间段内,通常是Hsync和图像之间的后廊周期。当钳位源=1时,该寄存器被忽略。通电默认设置为8。

0x1A位[7:0]钳位持续时间

一种8位寄存器,用于设置内部产生的钳位的持续时间。当钳位源选择为0(寄存器0x18,位4)时,钳位信号在钳位寄存器(寄存器0x19)建立的位置内部生成,持续时间由该钳位持续时间寄存器设置。钳制在Hsync的后缘之后开始像素周期的钳制放置计数(寄存器0x19)。钳位持续时间可以编程为1到255之间的任意值。不支持值0。

为了获得最佳结果,应将钳位持续时间设置为包括Hsync信号后缘之后的大部分黑色参考信号时间。夹紧时间不足会在屏幕顶部产生亮度变化,并从平均图像级别(APL)或亮度的大变化中缓慢恢复。当EXTCLMP=1时,忽略该寄存器。通电默认设置为20d。

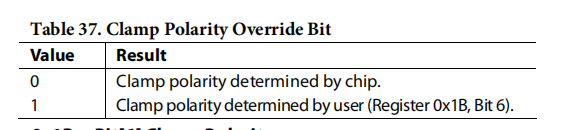

0x1B位[7]钳位极性超控

该位用于覆盖确定钳位信号极性的内部电路。开机默认设置为0。

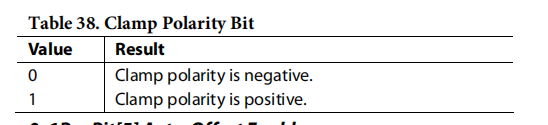

0x1B位[6]钳位极性

仅当寄存器0x1B的位7=1时,该位指示钳位信号的极性。开机默认设置为1。

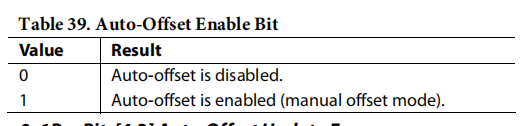

0x1B位[5]自动偏移启用

该位在自动偏移模式和手动偏移模式(禁用自动偏移)之间进行选择。有关详细信息,请参见“自动偏移”部分。开机默认设置为0。

0x1B位[4:3]自动偏移更新频率

这些位控制自动偏移电路的更新频率(如果启用)。建议每192个Hsyncs更新一次。开机默认设置为11。

0x1B位[2:0]

必须写入011才能正常运行。

0x1C位[7:0]测试寄存器0

必须设置为0xFF才能正常运行。

SOG控制

0x1D位[7:3]SOG切片器比较器阈值

这些寄存器位以8mV为步进调整SOG切片器的比较器阈值,最小设置为8mV,最大设置为256mV。通电默认设置为15d,对应于128 mV的阈值。

0x1D位[2]漏极性

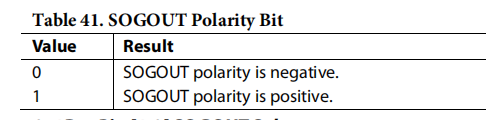

该位设置浸润信号的极性。开机默认设置为0。

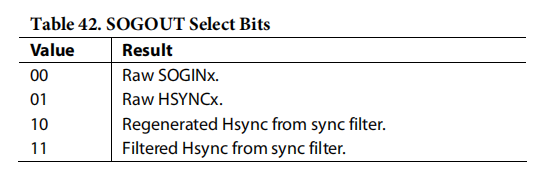

0x1D位[1:0]SOGOUT选择

这些寄存器位控制SOGOUT管脚上的输出。选项包括切片器中的原始同步(即,同步切片器生成的未处理的SOG信号)、原始HSYNCx、同步筛选器中的重新生成的Hsync,这些Hsync可能由于滑行或退出而生成丢失的同步,或者最后是筛选的Hsync,这些Hsync排除了同步筛选器窗口中未出现的外部同步。开机默认设置为0。

输入和功率控制

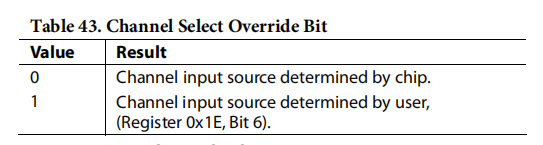

0x1E位[7]通道选择覆盖

该位提供对自动输入通道选择的覆盖。开机默认设置为0。

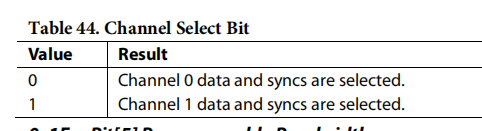

0x1E位[6]通道选择

如果寄存器0x1E的位7为1,则该位选择激活的输入通道。这将在通道0数据与同步或通道1数据与同步之间进行选择。开机默认设置为0。

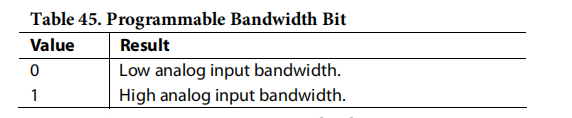

0x1E位[5]可编程带宽

该位在低或高输入带宽之间进行选择;具有低输入带宽有助于限制低频输入的噪声。开机默认设置为1。低模拟输入带宽~7mhz;高模拟输入带宽~300mhz。

0x1E位[4]断电控制选择

该位决定断电是由芯片手动控制还是自动控制。如果选择自动控制(通过将该位设置为1),则AD9984A的决定基于某些同步检测位(寄存器0x24、位2、位3、位6和位7)的状态。如果在任何输入上检测到Hsync或sync on green输入,则芯片将通电或断电。对于手动控制,AD9984A允许通过专用引脚和寄存器位灵活控制。专用管脚允许硬件看门狗电路控制掉电,而寄存器位允许由软件控制掉电。使用手动断电控制时,无论是否使用,都必须设置断电引脚的极性(寄存器0x1E,位2)。如果未使用,建议将极性设置为高活性,并用10 kΩ电阻将引脚硬接线接地。

0x1E位[3]断电

此位用于手动将芯片置于断电模式。仅当选择了手动断电控制(寄存器0x1E,位4=0)时才使用。此寄存器位的状态和掉电引脚(引脚17)都用于控制手动断电。(有关关机的详细信息,请参阅电源管理部分。)

0x1E位[2]断电引脚极性

该位定义掉电引脚(引脚17)的极性。仅当选择了手动断电控制(寄存器0x1E,位4=0)时才使用。

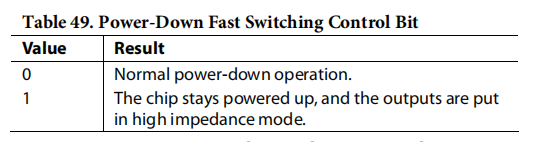

0x1E位[1]掉电快速切换控制

该位控制一种特殊的快速切换模式。使用该位,AD9984A可以在断电期间保持激活状态,并且只将输出置于高阻抗。当两个芯片的数据输出连接到一个PCB上,并且用户希望在两个芯片之间即时切换时,此选项非常有用。

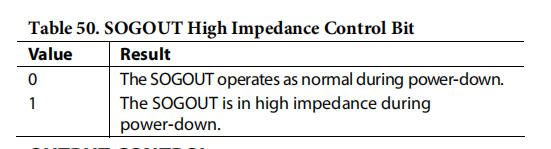

0x1E位[0]浸没高阻抗控制

此位控制断电模式下浸没输出引脚是否处于高阻抗。在大多数情况下,在正常运行期间,由于通常需要图形控制器进行同步检测,所以不会将SOGOUT置于高阻抗状态。将渗水沟置于高阻抗的选项主要包括允许工厂测试模式。

输出控制

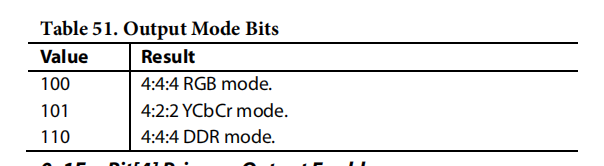

0x1F位[7:5]输出模式

这些位在输出模式的三个选项之间进行选择。在4:4:4模式下,RGB是标准的。在4:2:2模式下,YCbCr是标准配置,它将输出管脚的数量从30个减少到20个。在4:4:4ddr输出模式下,数据处于RGB模式,但在每个时钟边缘都会发生变化。通电默认设置为100。

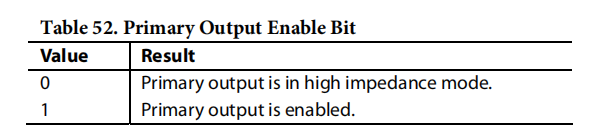

0x1F位[4]主输出启用

该位将主输出置于激活或高阻抗模式。开机默认设置为1。

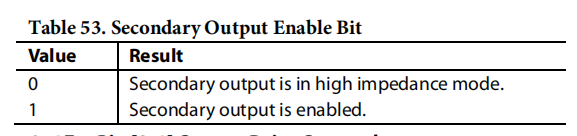

0x1F位[3]辅助输出启用

该位将二次输出置于激活或高阻抗模式。

在使用4:2:2或4:4:4 DDR时指定辅助输出。在这些模式中,蓝色输出通道上的数据是次要输出,而红色和绿色通道上的输出数据是主要输出。辅助输出始终是DDR YCbCr数据模式。请参阅输出格式化程序部分和表12。开机默认设置为0。

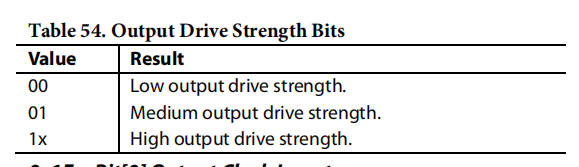

0x1F位[2:1]输出驱动强度

这两个位为所有高速数字输出(除了VSOUT、A0和O/E字段)选择驱动强度。更高的驱动强度会导致更快的上升/下降时间,并且通常更容易捕获数据。较低的驱动强度会导致上升/下降时间变慢,并有助于降低EMI和数字产生的电源噪音。通电默认设置为10。

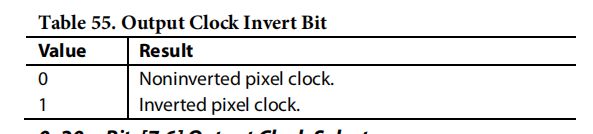

0x1F位[0]输出时钟反转

该位允许输出时钟反转。开机默认设置为0。

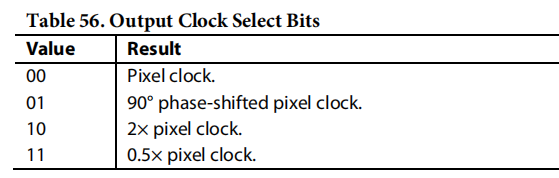

0x20位[7:6]输出时钟选择

这些位选择可选的输出时钟,例如固定的40mhz内部时钟、2×时钟、90°相移时钟或正常像素时钟。通电默认设置为00。

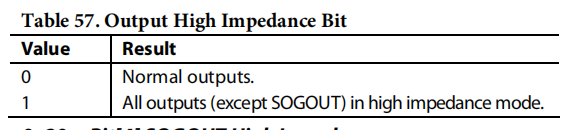

0x20位[5]输出高阻抗

该位将所有输出(除浸渍)置于高阻抗状态。通电默认设置为0。

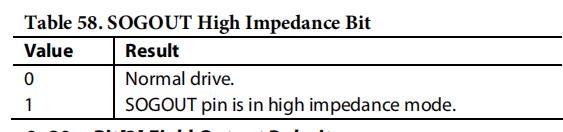

0x20位[4]吸收高阻抗

该位允许将渗液管脚置于高阻抗模式。开机默认设置为0。

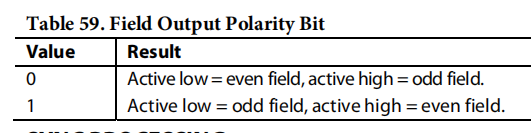

0x20位[3]场输出极性

该位设置磁场输出位的极性。开机默认设置为1。

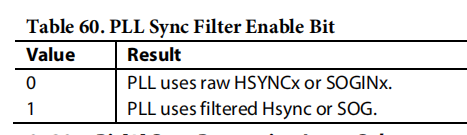

同步处理

0x20位[2]PLL同步滤波器启用

该位选择PLL使用的信号。它可以在HSYNCx/SOGINx的原始版本和Hsync/SOG的过滤版本之间进行选择。Hsync和SOG的过滤可以消除几乎所有传统上导致PLL中断的无关转换。开机默认设置为0。

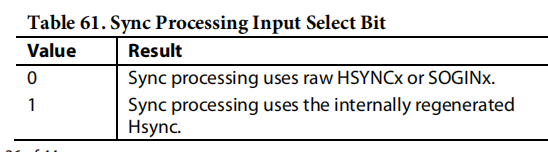

0x20位[1]同步处理输入选择

此位选择同步处理器是否使用原始同步或重新生成的Hsync执行以下功能:coast、Hsyncs per Vsync count、field detection和Vsync duration counts。建议使用重新生成的Hsync。

0x20位[0]

必须设置为1才能正常工作。

0x21位[7:0]

必须设置为默认值。

0x22位[7:0]

必须设置为默认值。

0x23位[7:0]同步滤波器窗口宽度

这个8位寄存器设置重新生成的Hsync前沿的时间窗口(以25 ns为步进),以及允许同步脉冲通过的时间。因此,默认值为10时,窗口宽度为±250 ns。目标是设置窗口宽度以拒绝无关脉冲(请参阅同步处理部分)。与同步分隔符阈值一样,25ns的乘数值也有些变化。所有操